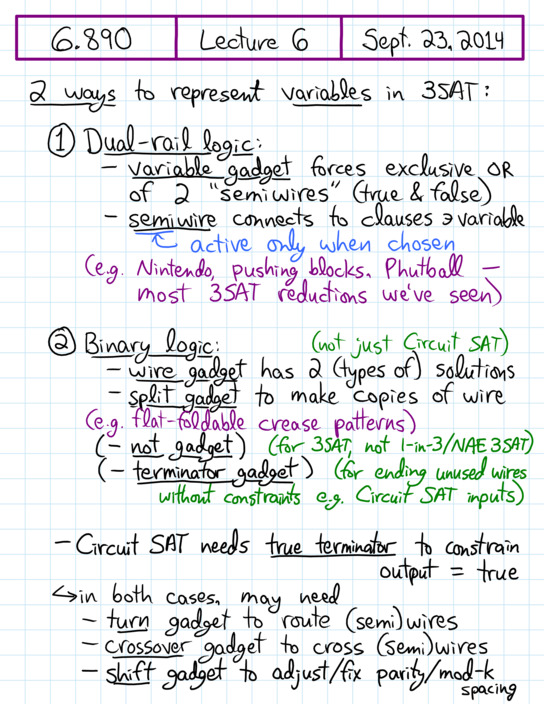

Handwritten notes, page 1/6 •

[previous page] •

[next page] •

[PDF]

Handwritten notes, page 1/6 • [previous page] • [next page] • [PDF]

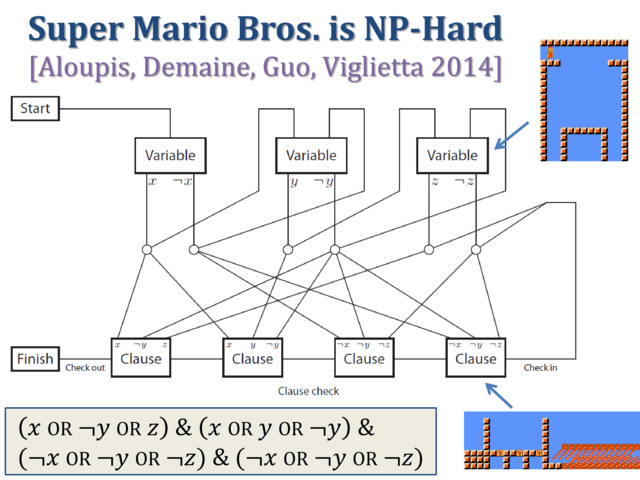

Slides, page 1/28 •

[previous page] •

[next page] •

[PDF]

http://arxiv.org/abs/1203.1895

Slides, page 1/28 • [previous page] • [next page] • [PDF]