## Design and Implementation of a Video Game System: Rodent Revenge in Space

Naoshin Haque Matthew Kwan Lynne Salameh

6.111: Introductory Digital Systems Laboratory December 9, 2004

**Abstract:** Rodent Revenge in Space is a video game, featuring Tim the beaver. Tim moves around the virtual world, where he encounters various enemies and obstacles. When facing an enemy, Tim throws logs at him. Tim will lose a life if an enemy injures him, but can gain lives by picking up powerups. The three modules in the game are the game controller unit, video controller unit, and the resizer. The game controller interfaces with the user and coordinates with the video controller unit to advance the game accordingly. The video controller unit outputs the images onto the screen and interfaces with the resizer in order to output the correct enemy size frame onto the screen. The resizer uses interpolation and decimation to shrink the enemy frame into different sizes. In conclusion, the project was a satisfying and extremely informative experience.

## **Table of Contents**

| 1 Video Game System Overview                              |    |  |  |  |

|-----------------------------------------------------------|----|--|--|--|

| 2 Subsystem 1: Game Controller Unit (by Lynne Salameh)    | 6  |  |  |  |

| 2.1 PC Module                                             | 8  |  |  |  |

| 2.2 Instruction Decoder                                   | 10 |  |  |  |

| 2.3 Register FSM                                          | 15 |  |  |  |

| 2.4 Testing and Debugging                                 | 17 |  |  |  |

| 3 Subsystem 2: The Resizer (by Naoshin Haque)             | 19 |  |  |  |

| 3.1 Resizer System Overview                               | 19 |  |  |  |

| 3.2 Resizer System Module Descriptions and Implementation | 21 |  |  |  |

| 3.2a Major FSM                                            | 22 |  |  |  |

| 3.2b Minor FSM                                            | 25 |  |  |  |

| 3.2c Overall Resizer Module                               | 31 |  |  |  |

| 3.3 Testing and Debugging                                 | 31 |  |  |  |

| 4 Subsystem 3: Video Controller Unit (by Matthew Kwan)    | 33 |  |  |  |

| 4.1 Video Controller Overview                             | 33 |  |  |  |

| 4.2 Sprite_table Module                                   | 34 |  |  |  |

| 4.3 Sync_generator Module                                 | 35 |  |  |  |

| 4.4 Timing Controls                                       | 36 |  |  |  |

| 4.5 Line Register Module                                  | 38 |  |  |  |

| 4.6 Overview Module                                       | 39 |  |  |  |

| 4.7 Debugging and Testing                                 | 40 |  |  |  |

| 5 Conclusion                                              | 42 |  |  |  |

| 6 Appendix: Verilog Code                                  | 44 |  |  |  |

| 6.1 Game Controller Unit                                  | 44 |  |  |  |

| 6.1a Controller                                           | 44 |  |  |  |

| 6.1b Decoder                                              | 44 |  |  |  |

| 6.1c PC                                                   | 53 |  |  |  |

| 6.1d Register File                                        | 54 |  |  |  |

| 6.2 Resizer                                               | 57 |  |  |  |

| 6.2a Major FSM                                            | 57 |  |  |  |

| 6.2b Minor FSM                                            | 59 |  |  |  |

| 6.2c Overall Resizer Module                               | 76 |  |  |  |

| 6.2d Filter Coefficients                                  | 77 |  |  |  |

| 6.3 Video Controller Unit                                 | 78 |  |  |  |

| 6.3a 6bit Reg                                             | 78 |  |  |  |

| 6.3b Line Reg                                             | 78 |  |  |  |

| 6.3c Overall                                              | 79 |  |  |  |

| 6.3d Sprite Table                                         | 83 |  |  |  |

| 6.3e Sync Gen                                             | 88 |  |  |  |

# List of Figures

| Figure 1: Overall Block Diagram for Video Game System          | 5  |

|----------------------------------------------------------------|----|

| Figure 2.1: Block Diagram for Game Controller                  | 7  |

| Figure 2.2: State Transition Diagram for PC FSM                | 10 |

| Figure 2.3: State Transition Diagram for Instruction Decoder   | 14 |

| Figure 2.4: State Transition Diagram for Register FSM          | 17 |

| Figure 3.1: Overall Resizer Block Diagram                      | 21 |

| Figure 3.2: Major FSM State Transition Diagram                 | 24 |

| Figure 3.3: Minor FSM State Transition Diagram                 | 28 |

| Figure 3.4: Example Image Matrix                               | 30 |

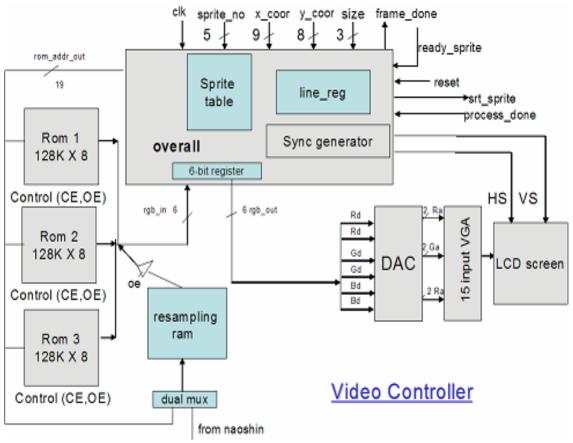

| Figure 4.1: Video Controller Block Diagram                     | 34 |

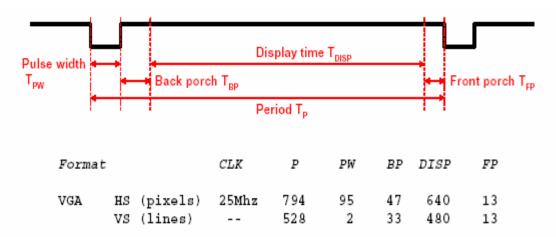

| Figure 4.2: Sync_generator Timing Durations                    | 36 |

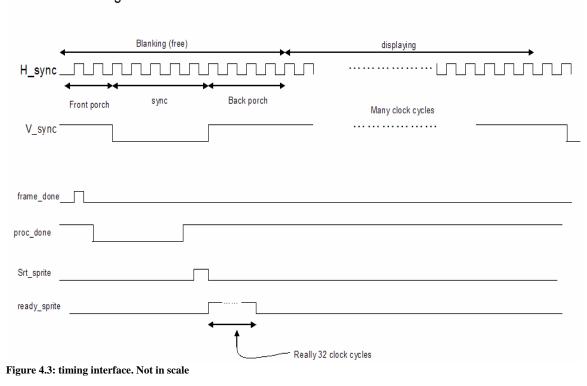

| Figure 4.3: Timing Interface between Game and Video Controller | 37 |

|                                                                |    |

## List of Tables

Table 1: Opcodes and Their Description

12

### 1 Video Game System Overview

This project will consist of a video game named Rodent Revenge in Space. The main character, Tim the beaver, is lost in outer space. Tim is trying to find the wormhole, which will lead him back to MIT. Along the way, many aliens will try to stop Tim from completing his journey, because they want to use his intelligence to take over the universe. Tim can only counter the aliens by throwing deadly wooden stakes at them. Initially, Tim has three lives, but if he is injured by an alien, he loses a life. However, if Tim has less than three lives and he collects enough energy drinks, he can regain the lives he lost.

The game will be configured so that the user's perspective coincides with Tim's perspective. The user will have access to six controls to manipulate the game:

- 1. Start button: initiates the game. If the user has pressed quit once, then pressing start would cancel the quit.

- 2. Up button: moves Tim forward through space.

- 3. Left Button: moves Tim sideways left across the screen

- 4. Right Button: moves Tim sideways right across the screen

- 5. Shoot Button: Triggers Tim to shoot a stake from where he is located on the screen

The screen display will be divided into several frames, which will each have x, y, and z coordinates. The x and y coordinates denote the horizontal and vertical position of the frame on the screen, respectively. The z coordinate determines which frame will take precedence on the screen. The frames will be of the following description:

- Tim's frame: A frame containing a back view of Tim's head. This frame will be positioned at the bottom of the screen, and will have the highest z value, meaning it will take the most precedence on screen.

- 2. Background frame: This frame is static, has the lowest z value, and consists of a space backdrop.

- 3. Road frames: There will only be one road frame on screen at a time, depending upon Tim's forward motion. Each road frame will lie centrally in the screen and will have a higher z value than the background frame.

- 4. Enemy frames: These frames will move along the road frame and their size depends on the enemy's distance from Tim. Their z value will be higher than the previous frames.

- Log/bullet frames: The log/bullet frames will be moving along the road frame.

These frames will have the second highest z value.

- 6. Energy frame: This frame will be moving with the road frame, but it will have a higher z value than the road frame.

- 7. Score/Lives frames: These frames will be at the top of the screen and will have a z value higher than that of the background frame.

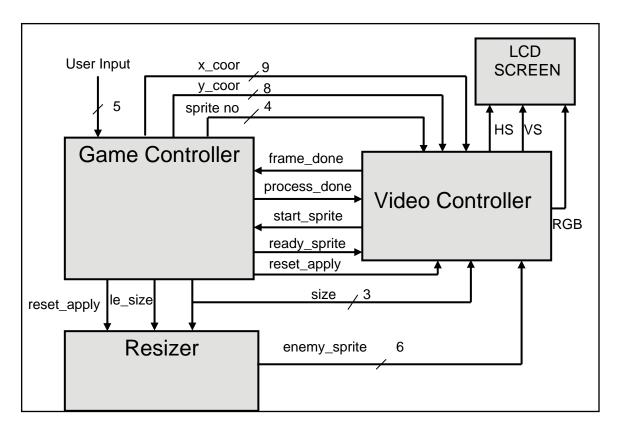

The game will be subdivided into three sections of roughly the same complexity: a game controller (Lynne), a decimator (Naoshin) and a video display module (Matt). A general block diagram for the system is shown below:

Game Controller Unit:

The game controller module handles the game's logistics. The game controller is in fact an FSM which has various states depending on the inputs. The game controller's main job is to decide which frames are going to be used in the video display at each timeslice. The time-slice's value will be chosen to simulate the game smoothly. The game controller will have an algorithm which decides when the alien will come on screen, and its trajectory towards Tim. The information associated with the alien will take form of output *size* which will be passed on to the Decimator. *Size* denotes how big the alien frame should be on screen.

Depending on the input of the user, the game controller will move Tim accordingly. The controller will keep track of the score and of Tim's lives. In addition, the game controller handles the timing and trajectory of the stakes and alien's photon bullets. Therefore, the game controller will output each frame's x, y, and z coordinates to the frame handler. The game controller will also output to the frame handler the frames which will be used in the next scene. In addition, the game controller will receive inputs from the frame handler indicating whether a bullet frame overlaps with the beaver frame, or if the log frame overlaps with the enemy frame. The game controller will then either, respectively, decrement the beaver's life or kill the enemy and increase the score of the beaver. After the beaver loses all lives, the game controller would signal the game is over.

Resizer:

The resizer changes the size of the enemy frames. The resizer receives input from the game controller denoting the size of the frame to be passed on to the frame handler. The resizer has access to a fixed-sized image which will then filter and downsamples at a rate specified by the game controller. The sampled image will be stored in the resizer's

3

ROM. It outputs an address range denoting where it will store the picture to the frame handler.

Video Controller Unit:

The Video Controller is divided into several submodules: Frame Handler, Sync generator, video memory, and the DAC.

<u>Frame Handler:</u> The frame handler receives an output from the Sync generator denoting the coordinates of the next pixel to be drawn. The frame handler will then check each frame to see if it contains the indicated pixel. If the pixel is contained in more than one frame, the handler will check the z values of those frames to see which frame has precedence. It will then output the color value of the pixel in that frame to the screen.

Sync generator: The sync generator controls the how the fast the electron beam sweeps across the screen. There are two sync signals: vertical and horizontal sweep. It outputs to the frame handler the coordinates of the next pixel to be drawn. The video memory stores the frames and outputs them to the frame handler, and the DAC converts the pixels from digital to analog.

Figure 1: Overall Block Diagram for Video Game System

#### 2 Subsystem 1: Game Controller Unit (by Lynne Salameh)

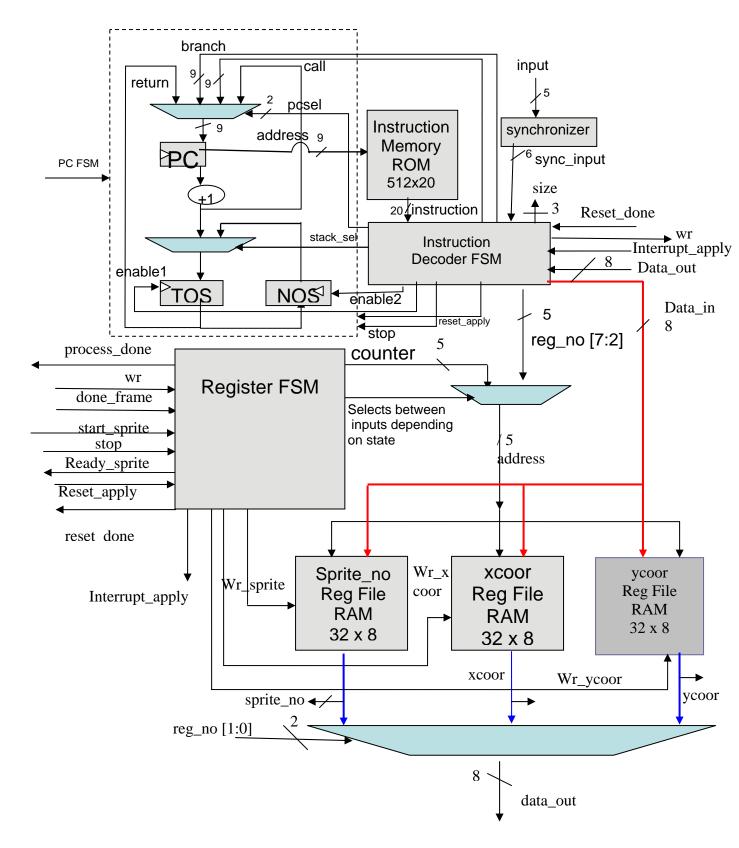

The game controller handles the user input and the progress of the game. It is in a sense a simple microprocessor that is programmed with instructions that simulate the game by choosing which sprites are going to be present on screen next. This functionality is captured by the sprite's *sprite no*, an index needed to differentiate between the different sprites, and its location on screen given by *xcoor* and *ycoor*. The information about the sprites is transmitted to the Video Controller as soon as it is ready. In addition, the controller determines the size of the alien sprite which needs to be passed on to both the Resizer and the Video Controller. The game controller is subdivided into three main submodules: PC module, Instruction Decoder module and the Register FSM module. A 512 x 20 built in MegaWizard ROM was used to store the instructions, and three 32 x 8 MegaWizard RAM's were used as the three register files needed to store sprite\_no, x\_coor and y\_coor. The game controller receives several control signals from the Video Controller which allow it to switch between processing mode and outputting the sprites, and these signals are *frame\_done*, triggering the start of the processing cycle, and a *start\_sprite* signal, triggering the sprite output cycle. A block diagram of the over all Game Controller Module can be seen in Figure 2.1. on the following page.

Java was used to write a compiler, which would take in an instruction and transform it into a 20 bit binary line, which was written to a .mif file.

Figure 2.1: Game Controller Block Diagram

## 2.1 PC Module

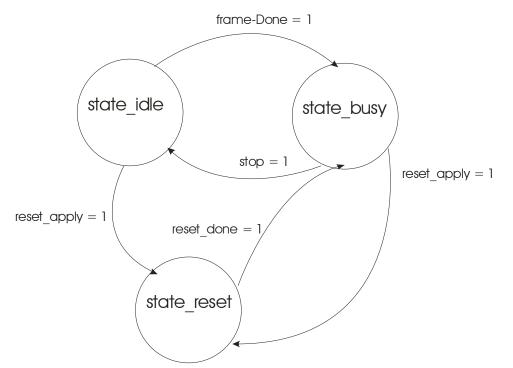

The PC module is in fact a simple FSM that controls the addressing of the instruction memory. The address is 9 bits, and is stored in a register called PC, or program counter. The PC determines which instruction will be read next. The PC module receives several control signals from the Instruction Decoder, in addition to the *frame\_done* signal from the Video Controller. The *frame\_done* signal indicates the begging of the processing cycle, and moves the FSM from state\_idle to state\_busy, as can be seen in the State Transition Diagram in figure 2.2. In state\_busy, the PC FSM takes into consideration several control signals : *pcsel*, *enable* and *stack\_sel* from the Instruction Decoder. The *pcsel* signal determines what value the PC register will assume next and therefore which line to be read from the Instruction Memory. The PC module also implements a two element stack, in the form of the registers TOS and NOS. These are loaded when they receive the *enable* signal from the Instruction Decoder.

There are five different values for *pcsel*, which are:

- 1. pcsel = 0: The program is advancing normally, and therefore the next instruction to be read is the current instruction + 1, i.e. PC + 1.

- pcsel = 1: This control signal causes the PC to branch to a new value, and therefore loads the value of the *branch* from the Instruction Decoder into the PC register. This in effect causes the address of the instruction memory to jump from on value to the other.

- 3. pcsel = 2: Facilitates calls to instruction lines. A call causes the PC to jump to a new value, while at the same time storing the current value + 1 into a stack. The

signal *call* from the Instruction Decoder determines the new address, and is loaded into the PC register.

- 4. *pcsel* = 3: Triggers a return, that is, the value of TOS is loaded into the PC register, and therefore the instruction that is read returns to the instruction after when the most recent call was made.

- 5. pcsel = 4: Maintains the current PC and does not change it. This is needed during the intermediate states of the Instruction Decoder which will be discussed later.

As for *enable*, it is three bit, and it can take 3 meaningful values:

- 1. enable[0] = 1: Loads PC +1 into the top of the stack TOS.

- 2. *enable*[1] = 1: Loads the value of TOS into NOS the rest of the stack.

- 3. *enable*[3] = 1 : Loads the current PC into TOS, which is needed when an interrupt occurs.

Similarly *stack\_sel* can take two values:

- 1.  $stack\_sel = 0$ : Allows PC +1 to be loaded into TOS.

- 2. *stack\_sel* = 1: Allows the value of NOS to be loaded into TOS.

The control signals described enable PC + 1 to be pushed onto the top of the stack, TOS, on a call. In other words *stack\_sel* = 0 and *enable* = 3 causes the TOS to be loaded with PC + 1 and NOS would take the value of the old TOS. On the other hand, *stack\_sel* is set of 1 on a return, which, combined with setting *pcsel* to 3 and *enable* to 1 pushes the return address of the TOS and loads it into the PC. When *enable[2]* = 1, indicating that an interrupt has occurred, the TOS will be loaded with PC rather than PC + 1, NOS is loaded with the old value of TOS and therefore an interrupt functions in a similar way to call, except for that PC is loaded into TOS. During the busy state, a *stop* signal from the Instruction Decoder would cause the PC to revert back into its idle state, and await from a new *frame\_done* signal from the Video Controller. A *reset\_apply* from the Instructon Decoder causes the PC FSM to revert to the reset state, from which it would go to the busy state on receiving a *frame\_done* signal from the Register FSM.

Figure 2.2: State Transition Diagram for PC FSM

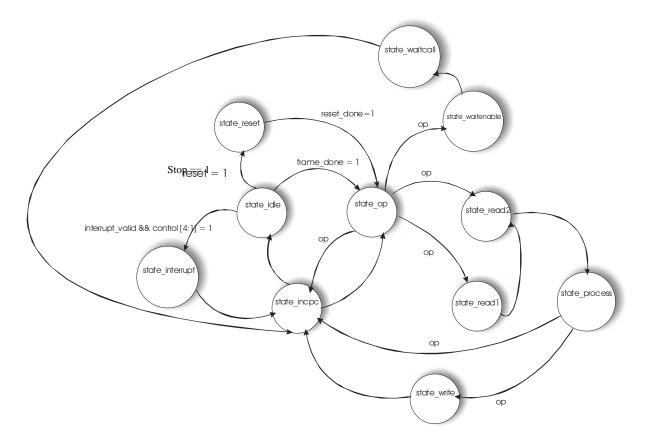

## **2.2 Instruction Decoder**

The Instruction Decoder processes the 5 user inputs that signify forward, right, left, shoot and reset. This 5 bit input in the form of *user\_in* is first synchronized to match the 12 MHz clock the Game Controller runs on. The Game Controller also takes the 20 bit instruction outputted from the Instruction Memory, and determines which action to take next depending on the 4 bit operation code at the beginning of the instruction. The

action is in the form of several control signals to be sent to the other modules. The rest of the 20 bit instruction contains relative information that will be used by the decoder to complete the operations described by the opcode, such as the address to be read or written to in the Register RAMS (*reg\_no [7:0]*), the register which is to be read or written to (i.e. whether it is sprite\_no, xcoor or ycoor, handled by the signal *reg\_no[1:0]*), call and branch addresses, which input to look at, and the internal register number for which results of comparisons are stored. The Instruction Decoder reserves four internal registers that will store the values of comparisons and these are set by operations such as COMPEQ, COMPLE, COMPEQC, and COMPLEC. The signals *branch* and *call* are always set to be equal to *instruction[8:0]*. Table 1 summarizes up all the opcodes and the information captured by the remaining 16 bits of the instruction.

| Opcode | Instruction | Description                                                                    |  |  |

|--------|-------------|--------------------------------------------------------------------------------|--|--|

| 0000   | ASSIGN      | Assigns a value equal to <i>instruction</i> [7:0] to the register              |  |  |

|        |             | memory line with address <i>reg_no[15:9]</i>                                   |  |  |

| 0001   | ADDC        | Reads in the value of the register memory line with address                    |  |  |

|        |             | instruction[15:9] and writes back onto that address the value                  |  |  |

|        |             | of the memory line plus <i>instruction</i> [7:0]                               |  |  |

| 0010   | BRANCHCOND  | Compares the synchronized input <i>control</i> to                              |  |  |

|        |             | <i>instruction</i> [15:11] and causes a branch if they are equal               |  |  |

| 0011   | COMPEQ      | Compares the value of the register file at address <i>reg_no</i> =             |  |  |

|        |             | instruction[15:9] with the value of the register file at address               |  |  |

|        |             | <i>reg_no= instruction[8:2]</i> and sets the internal registers                |  |  |

|        |             | specified by <i>instruction[1:0]</i> to be 1 if the values are equal, (        |  |  |

|        |             | otherwise                                                                      |  |  |

| 0100   | BEQ         | Causes a branch to <i>instruction</i> [8:0] if the internal register           |  |  |

|        |             | specified by <i>instruction</i> [15:14] equals 0                               |  |  |

| 0101   | CALL        | Causes a call to <i>instruction</i> [8:0]                                      |  |  |

| 0110   | RETURN      | Causes a return                                                                |  |  |

| 0111   | STOP        | Makes the stop signal that is an input to the PC and Register                  |  |  |

|        |             | File modules go high for 1 clock cycle                                         |  |  |

| 1000   | SIZE        | Sets <i>size</i> to be equal to <i>instruction</i> [2:0]                       |  |  |

| 1001   | COMPEQC     | Compares the value of the register file at address <i>reg_no</i> =             |  |  |

|        |             | <i>instruction</i> [15:9] with a literal of value <i>instruction</i> [8:2] and |  |  |

|        |             | sets the internal registers specified by <i>instruction[1:0]</i> to be         |  |  |

|        |             | if the values are equal, 0 otherwise                                           |  |  |

| 1010   | COMPLE      | Compares the value of the register file at address $reg_no =$                  |  |  |

| 1010   | 0011122     | <i>instruction</i> [15:9] with the value of the register file at address       |  |  |

|        |             | $reg_no = instruction[8:2]$ and sets the internal registers                    |  |  |

|        |             | specified by <i>instruction</i> [1:0] to 1 if the former value is less         |  |  |

|        |             | than or equal to the later.                                                    |  |  |

| 1011   | COMPLEC     | Compares the value of the register file at address <i>reg_no</i> =             |  |  |

|        |             | <i>instruction</i> [15:9] with the literal of value <i>instruction</i> [8:2]   |  |  |

|        |             | and sets the internal registers specified by <i>instruction</i> [1:0] to       |  |  |

|        |             | 1 if the former value is less than or equal to the later.                      |  |  |

| 1100   | AND         | Computes the value of the internal registers specified by                      |  |  |

|        |             | <i>instruction</i> [15:14] AND the value of the internal register              |  |  |

|        |             | specified by <i>instruction</i> [13:12], placing the result in the             |  |  |

|        |             | internal register specified by <i>instruction</i> [11:10]                      |  |  |

| 1101   | OR          | Computes the value of the internal registers specified by                      |  |  |

|        |             | <i>instruction</i> [15:14] AND the value of the internal register              |  |  |

|        |             | specified by <i>instruction</i> [13:12], placing the result in the             |  |  |

|        |             | internal register specified by <i>instruction</i> [11:10]                      |  |  |

| 1110   | EQIN        | Sets the internal register specified by <i>instruction</i> [12:11] to 1        |  |  |

|        | -21         | if <i>control</i> specified by <i>instruction</i> [15:13] is equal to          |  |  |

|        |             | instruction[10]                                                                |  |  |

| 1111   | BNE         | Causes a branch to <i>instruction</i> [8:0] if the internal register           |  |  |

| 1111   |             | a causes a branch to mon nemon [0,0] if the internal register                  |  |  |

## Table 1: Opcodes and their Description

Since the register file memories can only be read and written to at separate times, several states were constructed in order to allow for this functionality, as shown in Figure 2.3, which is a state transition diagram of the decoder. The instruction decoder remains in the idle state till it receives a *frame done* signal from the Video Controller, indicating that it needs to transition to state\_op, where the begging of the processing occurs. In state op, the opcodes are used to determine which state will be chosen next. In cases where there will be no accesses to memory, i.e. for operations such as COMPEQ and CALL, the control signals are set to the correct values, and the FSM transitions to state\_incpc, in which control signals are set to increment the PC in the PC module according to the opcode. Other operations such as ASSIGN and ADDC, require writing onto the memory, in which case, whereas operations such as COMPEQ require reading from two memory locations. In order to facilitate these operations, several read states for the two reads required were added to the FSM, a write state where wr would be high for one clock cycle, and a process state acts as an intermediate and chooses to continue onto the write state or the state\_incpc. Assigning the *xcoor* and *ycoor* memory locations to a non-zero value when the corresponding *sprite\_no* location is 0 has no effect on displaying the sprites, since the Video Controller ignores the sprites with sprite number 0. Therefore assigning these registers to certain values was used when writing the game code in order to use several local variables.

**Figure 2.3: state transition diagram for the Instruction Decoder**. All states lead into the reset state when *reset\_apply* is high. Similarly, all states lead into state\_interrupt when *interrupt\_valid* and *control[4:1]* are high

The call operation requires the enable signal for NOS to go high before the enable signal for the TOS, at the same time keeping the PC constant for an extra clock cycle to avoid timing issues. Adding two extra states wait\_enable and wair\_call allows for this behavior to occur. These states are only accessed during a call procedure.

On reaching state\_inpc, a stop operation from the Instruction Memory would cause the FSM to revert back to state\_idle, and wait for the next *frame\_done* signal. Otherwise, the state\_incpc would lead back into state\_op on the next clock cycle, freezing the pc by setting *pcsel* to 4. Two deviations may occur from this standard flow:

- A reset is pressed, and therefore *reset\_apply* is high, which triggers all the states to revert to state\_reset. In state\_reset, the PC is frozen by selecting *pcsel* = 4 and data\_in is set to 0, until a *reset\_done* signal is received from the Register File FSM, indicating that the memories have been blanked and that it is possible to proceed to state\_op.

- 2. An interrupt occurs, i.e. the *interrupt\_valid* signal from the Register FSM, occurring a clock cycle after the *frame\_done* signal, coincides with a non-zero value for *control[4:1]*, in other words, the user has pressed one or more of the buttons. An interrupt can occur in any state, and this causes the FSM to jump to state\_interrupt, where control signals are chosen so as to force the PC to jump to location 461 of the memory, the location of the interrupt handler code. The control signals also ensure that the PC is stored in the TOS.

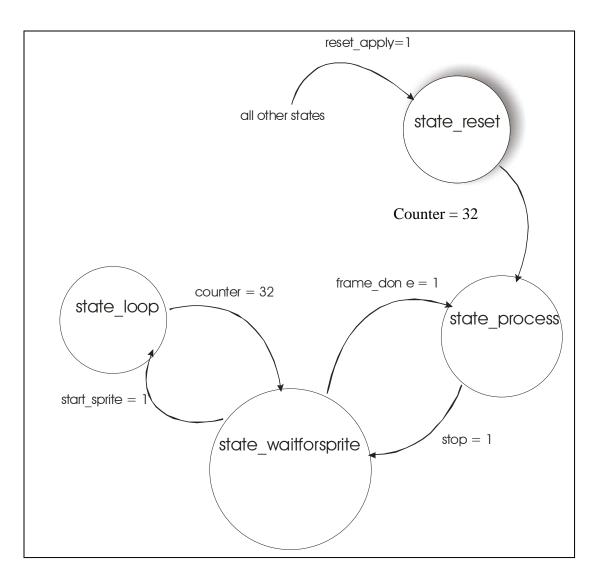

#### 2.3 Register FSM

The Register FSM controls the reading and writing onto the three 32 x 8 RAM's that contain information about the sprite\_no, xcoor and ycoor of the sprites to be used in the current frame of the video memory. The Register FSM has two main states, as shown in Figure 2.4, and these are state\_process and state\_loop. An intermediate stage between these two processes occurs as state\_waitforsprite, in which the FSM waits for either a *start\_sprite* signal from the Video Controller, causing it to transition to state\_loop, or a *frame\_done* signal, causing it to return to state\_process.

state\_process: in this state the Instruction Decoder drives the address line using *reg\_no*, whose lowest 2 bits are used to determine which of the three memories to be written or read from. In this state, the signal *wr* is translated into the separate

write enables for each RAM, depending on the value of *reg\_no*[1:0]. Similarly, *data\_in* is the value from the Instruction Decoder that is written to one of the memories, and *data\_out* is the value read from one of the memories, which is chosen by *reg\_no*[1:0]. During state\_process, the control signal *process\_done* which is outputted to the Video Controller goes low as long as the FSM is in this state, indicating that the Game Controller is processing instructions from the Instruction Memory. As soon as a *stop* signal is received, the FSM would revert to state\_waitforsprite.

2. state\_loop: In this state, and internal counter which counts from 0 to 31 drives the address lines of the three RAM's at the same time. The control signal *ready\_sprite* goes high as long as the FSM is in this state. The outputs of the three RAM's, in the form of xcoor, ycoor and sprite\_no, are transmitted to the Video Controller. The information is transmitted in 32 cycles, after which the FSM returns to state\_waitforsprite.

On receiving a *reset\_apply* signal from the Instruction Decoder, the FSM would revert to state\_reset, in which the counter drives the RAM's once again, but this time the write enable signals of all three RAM's is set to high, and a zero valued *data\_in* is used to blank the RAMs.

Figure 2.4: State Transition Diagram for Register FSM

## 2.4 Testing and Debugging

The early stages of debugging incorporated unit testing of each separate module, and used Max II plus' waveform editor to simulate the results of the module. For the Instruction Decoder module, each opcode was tested separately in the waveform editor in or to determine whether it indeed provided the correct functionality. After completing all the smaller modules, integration testing was performed on the top level module, controller. A simple program was written using the Java compiler, which only assigned several frames and provided an interrupt handler for the forward input. The Controller module was simulated using this program in the Instruction Memory, and the 32 cycle output to the Video Controller was checked to see whether it contains the correct information about the sprites. Wire signals were temporarily converted into outputs in order for them to appear in the waveform editor.

A had added a few more opcodes after I had done testing Instruction Decoder, and regression testing was performed through more simulation of the Instruction Decoder module to double check whether it still provided the correct functionality.

After the top level Display module was constructed, combining the Game Controller module and the Video Controller into one module on a single FPGA, the *vsync* and *hsync* values were changed to smaller ones for the purpose of simulation, and the module was simulated to ensure the correct functionality. The Display module was then loaded onto the FPGA and was tested directly by examining the output to the screen. By examining the screen, several bugs were detected, and to help with the debugging process, the 9 bit *pc* was converted to an output and connected to the logic analyzer, which was triggered on the *frame\_done* signal. An illegal loop which occurred when applying a STOP instruction followed by a RETURN was discovered and the higher order bits of the *enable* signal were also connected to the logic analyzer to study their behavior.

## **3** Subsystem 2: The Resizer (by Naoshin Haque)

## **3.1 Resizer System Overview**

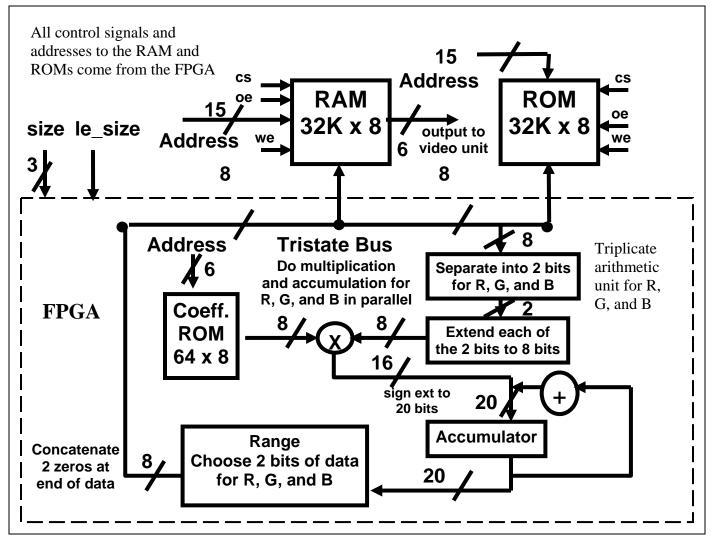

The purpose of the resizer is to take an original 64x64 pixel image of the alien and either replicate it or shrink it down to five different sizes. The six different sized images that can be produced are 64x64, 43x43, 32x32, 22x22, 16x16, and 11x11 pixels. In order to achieve this, interpolation and decimation methods are used on the original image. The image can be interpolated by a factor of 1 or 2 and decimated by a factor of either 1, 2, 3, 4, or 6. See Figure 3.1 on page 21 for an overall block diagram of the resizer subsystem.

The original colored image is stored in an external 32Kx8 Flash Memory, where only 4097 lines of memory are taken up. The first 4096 lines hold the image, and the 4097<sup>th</sup> line is all zeros. The resizer receives a constant 3-bit size from the video controller unit. This size is used to look up the interpolation and decimation factors in a lookup table. After the size has been valid for at least one clock cycle, the resizer receives a load enable signal, called le\_size, from the video game controller unit, signaling the resizer to begin its processing.

Once the resizer starts its processing, it goes through three or four stages, depending on the decimation factor. The FPGA sends control signals and addresses to all of the ROMs and the 32kx8 external RAM, accordingly. In addition, a tristate bus is shared between the FPGA, the RAM, and the ROM for the 8-bit data. The first stage is copying the original image from the ROM to the RAM or storing an upsampled version of the image in the RAM if the interpolation factor is 1 or 2, accordingly. Once the image is stored in the RAM, the ROM is no longer used for any calculations. The second stage is where the image stored in the RAM is interpolated, while the third stage is decimation

on this interpolated image. If the decimation factor is 4 or 6, the resizer goes into its fourth stage, so that it can perform decimation on the already decimated image.

The color being used for the image is 64-bits, meaning there are only four shades of intensity per R, G, and B. When reading from the RAM to do the calculations, the 8bit data is separated into 2-bits for R, 2-bits for G, 2-bits for B, and the last 2-bits are discarded. The arithmetic unit is triplicated so that two-dimensional convolution can be performed on the R, G, and B in parallel. The two-dimensional convolution consists of looking at a 3x3 matrix around the appropriate R, G, or B component of the pixel and multiplying these 9 values with the appropriate filter coefficients. The filter coefficients are stored in a 64x8 ROM. The 9 products are accumulated and sent through a range to select the 2-bits for R, G, and B. These bits are then concatenated with 2 zeros and sent to the tristate bus to be written back to a different portion of the RAM.

Once all of the calculations for the two-dimensional convolution are completed and the final data has been written to the RAM, the video controller unit reads from the RAM. The addresses to the RAM, which are sent from both the resizer module and the video controller module, are put through four 8-to-1 multiplexers, while the data bus for the RAM is put through two tristate drivers. The output enable signals to the multiplexers and the tristate drivers are controlled by the video controller unit. Once the video controller unit is done processing, it once again sets the output enables to their correct values to enable the resizer to start its processing once again.

Figure 3.1: Overall Resizer Block Diagram

## 3.2 Resizer System Module Descriptions and Implementation

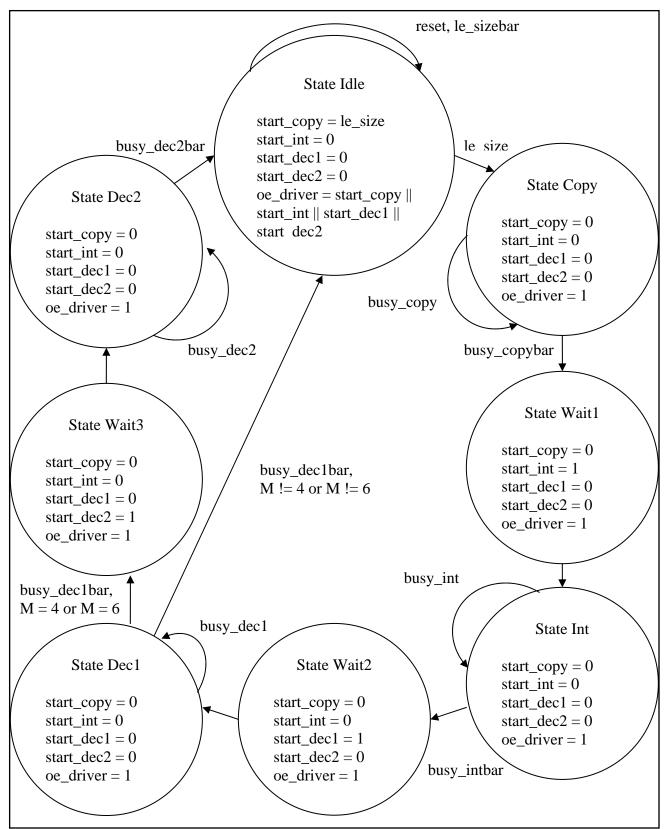

The resizer system consists of two main modules, which are the major finite state machine and the minor finite state machine (FSM). The minor FSM can be in four different stages, which are copying, interpolating, decimating, and decimating twice. The major FSM sends the appropriate control signals to tell the minor FSM which stage to be in. The minor FSM sends busy signals back to the major FSM, to denote when it is still processing. Using these communication signals, the major and minor FSM are able to coordinate such that the two-dimensional convolution is performed correctly.

## 3.2a Major FSM

The main purpose of the major FSM is to control which of the four stages the minor FSM is in. These four stages include copying, which includes both copying and upsampling, if necessary, interpolation, decimation, and decimation twice if needed. The major FSM starts off in the idle state, which it also returns to any time a reset button is pushed. The major FSM remains in the idle state until it receives a load enable signal from the video controller unit. It then sets start\_copy to equal le\_size, which is just high for one clock cycle. This tells the minor FSM to go to its copy stage. The major FSM state transition to the copy state. See Figure 3.2 on page 24 for the major FSM state transition diagram.

Once in the copy state, the major FSM remains there as long as it receives a high busy\_copy signal from the minor FSM. This busy\_copy signal denotes that the minor FSM is still processing. Once the busy\_copy signal goes low, the major FSM goes to the wait1 state, where it remains for one clock cycle. In this state, the major FSM sets the start\_int signal to high, indicating that the minor FSM should now go into its interpolation stage. The major FSM then transitions to the interpolation stage, where it remains as long as it receives a high busy\_int signal from the minor FSM. Once the minor FSM is finished performing the interpolation, it sends a low busy\_int signal to the major FSM.

The wait2 state has a duration of one clock cycle and is also the state in which the major FSM sets start\_dec1 to high. The major FSM then transitions to the dec1 stage, which is where the minor FSM outputs a high busy\_dec1 signal as long as it is in this first decimation stage. After receiving a low busy\_dec1 signal, the major FSM must look up

the decimation factor by using the size lookup table before progressing. If the decimation factor, M, is equal to 1, 2, or 3, the major FSM transitions to the idle state, where it remains until it receives another high load enable signal from the video controller unit. However, if M is equal to 4 or 6, the major FSM goes to stage wait3, where it sets start\_dec2 to high. After staying in the wait3 state for one clock period, the major FSM transitions to the dec2 stage.

The major FSM continues to stay in the dec2 state as long as it receives a high busy\_dec2 signal from the minor FSM. Once the minor FSM is finished doing the second decimation, it sends a low busy\_dec2 signal to the major FSM. The major FSM then transitions back to its idle state, where it will remain until it receives another high load enable signal. When the major FSM has returned back to the idle state, it denotes that one full resizing has occurred, meaning that the final replicated or shrunken image has been written into the RAM, and is waiting to be read by the video controller unit.

Another signal in the major FSM module is the oe\_driver signal, which is used as an output to the minor FSM. While the major FSM is in its idle state, the video controller unit must be able to read from the RAM, so the oe\_driver signal is low only during this time to indicate this. Therefore, when the minor FSM is in its idle state, it will use the oe\_driver signal as an input to set the control signals of the RAM accordingly.

Figure 3.2: Major FSM State Transition Diagram

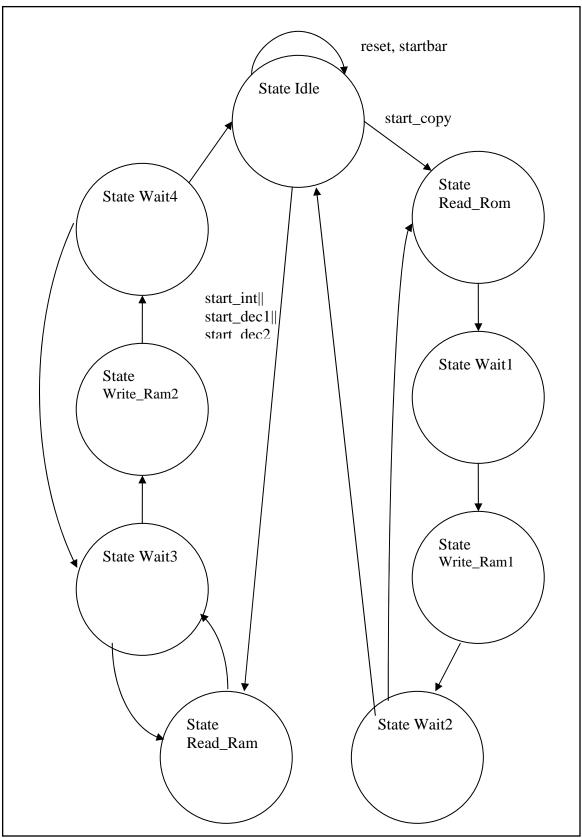

### 3.2b Minor FSM

The main purpose of the minor FSM is to perform all of the operations necessary to take the 64x64 image and resize it accordingly. The minor FSM can be in four different modes, which are the copy mode, the interpolation mode, the decimation mode, and the second decimation mode. The minor FSM has nine states, whose general state transition diagram can be seen in Figure 3.3 on page 28.

The minor FSM is able to receive four different start signals from the major FSM. Upon receiving one of these signals, the minor FSM will act accordingly by going to the correct mode. In addition, the minor FSM is the module that outputs the 15-bit addresses to the RAM and the ROM. The minor FSM also outputs the 6-bit address to the 64x8 filter coefficients ROM, which was generated using the Mega-Wizard, and is instantiated within the minor FSM module.

The minor FSM also receives a 3-bit size from the video controller unit, which it uses to look up the interpolation factor, L, and the decimation factor, M, in a lookup table. Upon reset, the minor FSM goes to its idle state, where all of the initial values are set. The minor FSM remains in the idle state until it receives a start signal from the major FSM. If this start signal is start\_copy, the minor FSM sets busy\_copy to high and transitions to the read\_rom state. In this state, the minor FSM reads from the appropriate line of the ROM, according to the assigned address. If the interpolation factor is 1, the exact image is copied from the ROM to the RAM, so the 4097th of the ROM is never used. However, if the interpolation factor is 2, an upsampled image is stored into the RAM. This upsampled image contains zeros in every other row and zeros in every other column, so the ROM reads from the 4097<sup>th</sup> line for quite some time.

The minor FSM stays in the read\_rom state for one cycle and then transitions to state wait1. State wait1 lasts for 1 clock cycle and sets the control signals so that the data read from the ROM can be written to the RAM. The data pins of the external ROM are connected directly to the data pins of the external RAM, which are also connected to the FPGA. The minor FSM writes the data to the RAM in state write\_ram1. After one clock period, the minor FSM transitions to the wait2 state. In this state, the minor FSM checks to see if all of the pixels of the image have been copied or upsampled depending on the interpolation factor. If this process is not done, the minor FSM will transition back to the read\_rom state to read and copy another pixel from the ROM to the RAM. However, if the process of copying is complete, the minor FSM goes to the idle state, where it remains until it receives another start signal from the minor FSM. The minor FSM only sets busy\_copy to low when it returns to the idle state.

The minor FSM goes through a very similar process when it receives either a high start\_int, start\_dec1, or start\_dec2 signal. After receiving either of these signals, the minor FSM sets the appropriate busy signal to high. This busy signal remains high until the FSM returns to the idle state again. After any of these three start signals goes high, the minor FSM transitions to the read\_ram state. The minor FSM remains in this state for one clock cycle and reads from the RAM according to the address assigned.

The minor FSM then transitions to the wait3 state, where it stays for one clock period. There are three multipliers, which are made by the Mega-Wizard, instantiated within the minor FSM module. Each of these multipliers take in two 8-bit inputs and outputs a 16-bit product. Since all of the numbers are positive, unsigned multiplication is being used. The two-dimensional convolution is performed by looking at a 3x3 matrix

around the appropriate R, G, or B component of the pixel. This means that each element of the matrix must be multiplied by the appropriate filter coefficient, which is read from the filter coefficients ROM. Since the R, G, and B are only 2-bits, 6 zeros are concatenated to the end of each component. This way higher precision arithmetic is being used, because the 6 zeros are considered to be after the decimal point. Then, these 9 products must be accumulated in order to output the new pixel. Since there are 9 products that are 16-bits each, three 20-bit accumulators are used to do the parallel processing of the R, G, and B. Therefore, all of the products must be sign extended from 16-bits to 20bits. In the wait3 state, the accumulation of the sign extended multiplication products takes place.

There also many internal counters that are used in the wait3 state, as well as some other states in the minor FSM. The first counter, count0, is used to tell which mode the minor FSM is in. Since the copying uses different states than the minor FSM, it is not included in these modes. The minor FSM is in the interpolation mode when count0=1, the decimation 1 mode when count0=2, and the decimation 2 mode when count0=3. Another counter, count1 is used to count the entries in each row of the image being processed on at the time. Count2 and Count3 are 15-bit counters used to tell the RAM what address to read and write to, respectively. Another counter, count4, denotes when all of the accumulations are done, and which filter coefficient to use for this element of the matrix. Finally, count5 is used for the decimation by 6 stage to see whether an entry in the 22x22 matrix is divisible by 22 or not, since the modulo function in Altera was not working.

Figure 3.3: Minor FSM State Transition Diagram

In state wait3, count4 is always incremented. If count4 does not equal 9, many other steps must be taken. First, after staying in the wait3 state for one clock cycle, the minor FSM will then transition to the read\_ram state. While in the wait3 state, count0 is checked to see whether the minor FSM is in the interpolation, decimation 1, or decimation 2 mode. Depending on the mode, the minor FSM will check the interpolation or decimation factor, so that it can act accordingly. When count4 is equal to 0 through 8, it assigns the address of the RAM so that data can be read from the RAM. It also assigns the address to the filter coefficients ROM, so that this data can be used in the multiplication along with the data from the RAM.

At each count4 value, the value of count2 is checked, to see which entry of the image matrix it is reading from. If count2 is assigned to a pixel that is placed in either the top row, bottom row, most left column, or most right column, then some of the entries of the 3x3 matrix surrounding the pixel will not exist in the image matrix. For instance, in Figure 3.4 shown on page 30, the entry 0 will only have four existing elements in its 3x3 matrix, which are the entries 0, 1, 6, and 7. In order to make sure the other products go to 0, count2 is checked to see whether it is in either the top, bottom, left, or right according to the what size image is being looked at the time. If the entry is in either of these locations, then the address of the filter coefficients RAM is set to 45, which is a line of 8 zeros. This way the product is equal to 0, and this value will not be taken into consideration during the accumulation. Usually the entries can be checked by seeing if count2 falls within a range of values or if count2 is a multiple of some power of 2 according to the size of the matrix. However, the only size where this was not the case was when doing decimation on the 22x22 image. Therefore, the count5 needed to

be used to check whether the entry was divisible by 22 or not, in order to see where the entry was located in the image matrix.

| 0  | 1  | 2  | 3  | 4  | 5  |

|----|----|----|----|----|----|

| 6  | 7  | 8  | 9  | 10 | 11 |

| 12 | 13 | 14 | 15 | 16 | 17 |

| 18 | 19 | 20 | 21 | 22 | 23 |

| 24 | 25 | 26 | 27 | 28 | 29 |

| 30 | 31 | 32 | 33 | 34 | 35 |

**Figure 3.4: Example Image Matrix**

However, if count4 equals 9, this means that all of the calculations in the arithmetic unit have taken place, so the data is ready to be written into the RAM. In this case, the address to be written into is set to count3 and the control signals of the RAM are set appropriately. Since the accumulation results are 20-bits, they must be sent through a range to pick 2-bits for R, 2-bits for G, and 2-bits for B. In the write\_ram2 state, the data output to the tristate bus is then the concatenation for the bits for R, G, and B, with 2 zeros, in order to comply with the 8-bits that must be written into the RAM.

After this data has been written to the RAM, the minor FSM sets all three of the accumulators back to zero, in order to make them ready for the next set of calculations. The minor FSM then transitions to the wait4 state, where it increments the address of where the RAM should be written to, which only takes effect if the minor FSM ever transitions back to the write\_ram2 state. Also in the wait4 state, the minor FSM first checks which mode it is in. Then, according to the mode, it uses either the interpolation

and decimation factor to check whether all of the data has been written to the ram by checking the value of either count2 or count3.

If all of the data has not been written to the RAM, the minor FSM transitions to the wait3 state, where it outputs the addresses and correct control signals to the RAM and coefficients ROM. This denotes the beginning of another cycle through the arithmetic unit, which will perform all of the necessary multiplication and accumulation before outputting another pixel of the new image. However, if all of the data for this new image has been written to the RAM, the minor FSM returns to the idle state. The minor FSM remains in this idle state, until it receives another high start signal from the major FSM.

## **3.2c Overall Resizer Module**

The top level module is a very simple module, which included instantiations of both the major and minor FSMs. The inputs to the entire resizer system are the clock, the synchronized reset from the game controller unit, the 3-bit size and le\_size signal from the video controller unit, and the 8-bit data from the RAM. The output of the resizer system are the 15-bit addresses to the RAM and the 32Kx8 ROM, and all of the control signals to both of these external memory devices. All other signals that were just used to communicate internally between the ROM and the RAM were wired within the top level module for the resizer system.

#### **3.3 Testing and Debugging**

Due to the fact that much time was spent planning the design and implementation of the process, only a short time was needed to debug the entire module. First, the major FSM was designed and tested. Since this module was quite simple, it worked perfectly on the first try. Next, the complex minor FSM was tested. Various things had to be checked for this module. For instance, each of the modes had to do all of the calculations correctly and at the correct time, as well as transitioning to the proper state. In addition, the counters had to increment in the proper pattern, so that the RAM and ROMs were being read from and in the case of the RAM, also written to correctly. After changing minor issues, such as the timing of the busy signals and timing of the count4 values, the minor FSM worked properly for a general set of filter coefficients. In addition, the top level module had to be tested to make sure that both of the modules worked together properly. After fixing a few timing issues between state transitions, such as the timing for the multiplication between the correct filter coefficient and the correct component of the image matrix, the top level module seemed to work correctly.

After the resizer seemed to be working for any general filter coefficients, the correct filter coefficients needed to be found. A MATLAB program had to written in order to find the most accurate coefficients. After this, the resizer needed to be tested to see the real-time image that it produced. Since the resizer was not interfaced with the video controller unit, there needed to be a way to output the image from the RAM onto a screen.

At first serial communication was going to be used to read the data from the RAM and output it to the computer screen. However, the timing for this was very complicated, so instead, the HP Logic Analyzer was used to store data. Using the Logic Analyzer in the state mode, a set of triggers can be set such that the Logic Analyzer only stores data on certain states. The Logic Analyzer was used to check the state transitions and data that was being written to the RAM. While the range was pretty much chosen by normalizing the filter coefficients, it was still helpful to check them and at times even improve them by looking at the data from the Logic Analyzer.

The stored data in the Logic Analyzer was then saved using a floppy disk and converted into the appropriate format to be used in MATLAB. A program was written to change the 8-bit data into a 64-bit color image. Using this program, it was demonstrated that the resizer module was working as it should be and was able to output 6 different sized images of the alien.

#### 4 Subsytem 3: Video Controller Unit (by Matthew Kwan)

### 4.1 Video Controller Overview

In the final project, I was in charge of the video controller. The general purpose of the video was being able to display each screen of the video game or any function run by the game controller. It did this by taking input from the game logic subsystem and used it to generate the images displayed to the user. The video component was partially designed using 3 external ROMs which stored every sprite. In addition to being an important feedback tool for the game controller, the video component was also used as a useful debugging tool for both the game controller and the video controller. The video system displayed a 64-bit color VGA video at 60 frames per second. The resolution was 320 by 480. There were 4 major modules. These were the sync\_generator module, the line\_register module, the sprite\_table module, and the overview module which pieced together the entire video component. The 4 modules were internal, meaning that they were written and programmed into the FPGA. See Figure 4.1 for block diagram.

Figure 4.1: Block Diagram of Video Controller

# 4.2 Sprite\_table Module

The sprite\_table module was essentially a lookup table. Its inputs included the sprite numbers to be displayed onto the screen, and if the sprite number referred to the enemy sprite, a certain size would also be inputted. Altogether there were 25 sprites. Each sprite has as outputs the memory address where the 1<sup>st</sup> pixel of a particular sprite is located at in the memory, and the sprite's corresponding width and height. The first two bits of the memory address output was dedicated to determining which of the 3 ROMs or RAM were being used. Two of the ROM's contained the 4 road sprites which were each 240 by 240 resolution. The other ROM contained the background image and all the other

sprites, including the powerup and score. Most of the sprites were drawn on Paint, the rest were drawn on Coral Draw. The sprites were drawn using RGB values, with 2 bits assigned to each color, therefore each color having 4 different shades. The overall number of colors was 64. The sprites were then saved as a bitmap file, and formatted appropriately using Matlab. Lastly, the sprites were programmed on the chip. The RAM, on Naoshin's board, contained the enemy image whose size could change depending on the current stage of the game, and what size the game controller inputted. Because both the resampler and the video controller had to use the same RAM, a dual input multiplexor was used to figure out when either the resampler or the video controller could access it.

## 4.3 Sync\_generator Module

The sync\_generator module generates the control signals necessary to drive the VGA monitor. These signals include the vertical sync, the horizontal sync, the vertical blanking, and the horizontal blanking signals. The sync\_generator module reads the color value of the current pixel from the external ROMs and outputs it to the DAC, which consists of a 6-bit register and 6 resistors. The DAC performs the digital to analog conversion necessary to display the data on the VGA monitor. Both the game controller and the video controller operated on the same 12mhz clock. This was used so that the timing controls between the two parts would be in sync.

The 12 mhz clock was mainly used as a "pixel clock" to display on the VGA screen. Every time the clock pulsed high, the current pixel data presented to the 6-bit register in the DAC would be latched in and converted to analog through the resistors. Each horizontal sync pulse is preceded by a complete line of pixels. Each vertical sync pulse is similarly preceded by a complete frame of lines of pixels. Each sync is

surrounded by a blanking interval, which consists of the back and front porches, and a pulse width. The duration and timing of these pulses depends on the resolution and refresh rate of the VGA monitor being used. See figure 4.2 below.

Figure 4.2: Timing durations based on 25 mhz clock, for timing based on 12 mhz clock multiple each number by .48

#### 4.4 Timing Controls

Every time after the last pixel of a frame is displayed on the screen, the game controller gives a frame\_done signal. In the overall module, this is when vblankon is pulsed high. The game controller then deasserts the process\_done signal to tell the video controller that it is done processing all the information needed to setup for the next picture frame to be displayed onto the screen. When the game controller is done processing, which should take much less than 2x10^4 clock cycles (app. the length of time vblanking is on), it's process\_done signal then goes high. This signals the opportunity for the video controller to give the game controller a start\_sprite signal whenever h\_blankon is high and v\_blankon is not high. Whenever the game controller is ready, the ready\_sprite signal will be asserted high. The game controller will then "spit" out 32 sprite numbers and their x and y coordinates that will be in the next frame, with each sprite number and corresponding information given during each clock cycle. The

video controller uses this information to detect whether the certain pixels of any of the sprites the game controller "spits" out are on a given line. Since there are only 25 sprites in total and most of them won't be displayed on a frame at the same time, the game controller will input to the video controller a sprite number of zero to signal that there is no sprite. After the 32 clock cycles, the game controller's ready\_sprite signal is deasserted, and the video controller can start displaying on the screen whenever its h\_reset signal is pulsed high. The cycle then starts over again when the video controller finishes displaying a line of pixels on the screen, and its h\_blankon signal is high (meaning the video controller gives another start\_sprite signal). See Figure 4.3 below for timing diagram.

Timing Interface between Game Controller and Video Controller

## 4.5 Line Register Module

The line register module is primarily used to store all the requisite information of each sprite that is supposed to be on a given line on the screen. At each line, the overview module (which will be discussed shortly) will check to see whether or not the sprites given by the game controller have pixels that are contained in that line. If it is, the load\_enable signal goes high, and that particular sprite's width, height, and rom\_addr (also discussed later) gets latched into a register. Those three pieces of information of each sprite is stored into registers to hold and remember the values later on. All this is done during the horizontal blanking intervals. When it comes time to display on to the screen (at h\_reset), the x\_hit signal then checks which of the stored sprite's pixels on that line get displayed on the screen. This is done by checking if the current x\_coor of the pixel at display is greater or equal to the x\_coor of the sprite (given by the game controller) with larger precedence and less than the x\_coor plus width of that sprite. If it is, x\_hit is one, otherwise x\_hit is zero. The overview module then proceeds to display that most precedence sprite's pixels onto the screen on the particular line. Whenever reset is high (which is when srt\_sprite is high, see the instantiation in overview) or frame\_done is high, the video controller makes sure to clear all the previous line's information from the registers so that it can use those registers to store information for the next line of pixels. In addition, the video controller sets the x\_coor register to a large value, so that it won't accidentally get an x\_hit.

# 4.6 Overview Module

The overview component is the module that puts all the other modules together, and directly interfaces with the game controller's top module. Whenever the game controller's ready sprite signal is high (this means when game controller tells me the sprites that are in the current frame), the video controller checks whether yt (where the current y\_coor of the pixel at display is on screen) is greater than or equal to the y\_coor of the sprite or less than/equal to the y\_coor plus height of the sprite. It also checks to see if the sprite\_no is not zero. If these conditions are true, y\_hit is high which means the sprite is on the next line, and will get stored into the registers in the line\_reg module. Otherwise, y\_hit is low and nothing happens. The video controller also keeps a counter in this module. Initially, when srt\_sprite is high, its counter is set to zero. Whenever ready\_sprite and y\_hit are asserted high, it increments the counter. The video controller then enables the load signal (which would load the sprite information into a register as described in the line\_reg module) at each count and when y\_hit is high. Because it is not expected for there to be more than 10 sprites displayed onto a single line in the screen, there are only 10 load enable signals and, therefore, 10 instantiations of the line\_reg module in the overview module. As mentioned before, the registers in the line\_reg module latch in 3 different values, one which is the rom\_addr. The rom\_addr is not merely the same as the mem\_addr, which is the address of one of the 3 ROMs where the 1<sup>st</sup> pixel of a particular sprite is at. Rather, the rom\_addr is the address in the ROM whose data (pixel) contents are fetched, and whose address changes depending on where in the screen the current pixel is being displayed. Besides knowing the mem\_addr to calculate the rom\_addr, the y\_coor, x\_coor, width of the sprite, and yt are used to calculate the rom\_addr. Although yt is 10 bits, the least significant bit is taken out because each line needs to be displayed twice on the screen to get the 640 by 480 frame. This is because all the sprites were drawn relative to a 320 by 240 frame. The calculation of rom\_addr abnormally took a vast majority of the 83 nanoseconds of the clock, because of the somewhat complicated computation and huge propagation delays. This complicated things because the video controller had to store all the sprite information in one clock cycle, since the game controller "spitted" out each sprite in one clock cycle. Therefore, all inputs to the rom\_addr made as registers and, in consequence, delayed by one clock cycle. This meant that though the game controller gave the sprite number and its corresponding x\_coor and y\_coor at a particular cycle, the information and calculations wouldn't be latched in until the following clock cycle. This gave ample time for the rom\_addr calculation as well as other things to be done in one clock cycle. The addition of xt was not added into the rom\_addr until much later when actually displaying on the screen to further alleviate the situation of having a potential problem due to "heavy" computation. If there were no x-hits, then the background pixels would show up by default.

# 4.7 Debugging and Testing

During the course of the final project, my video controller went through many design stages. The biggest one turned out to be one week before it was due. In my previous design, I used many external chips, including two SRAMs used for memory. Two video memory chips were used because so that I could interleave the two memories together such that one would be read from at the same time the other would be written to. I also would have used a number of tri-state buffers and a 8-bit register for my DAC. Though I did a lot of extensive simulations on my modules pertaining to that previous design, it was unfortunate that I only realized the futility of my design this late into the process when I was about to wire it and assign pins. In total, I had to use approximately 70 pins, while the FPGA only had 50+ pins. This did not include the additional 10 pins that the game controller needed since we would be using the same FPGA. Although it was still somewhat feasible to decrease the number of pins using various methods, including faking more pins by time multiplexing several signals onto one set of pins, I would have needed to run at a higher clock frequency in order to get the same amount of information as the non-multiplexed scheme out of the chip within a given time interval. This meant running I would have had to run at a 25mhz pixel clock, which was not guaranteed to work on the FPGA kits. In order to be within the allotted set of pins, I still would have had to reduce approximately 15 pins, and though this was plausible theoretically (I won't go into detail) it was both not guaranteed to work and even more timing issues would be involved. I also decided to do away with my original design because the amount of wiring would have been enormous. Although I was extremely hesistant to implement the new design back then, in the end, it turned out to be a success. Though there was still a lot of wiring, it was much less than what it could have been. The number of FPGA pins that I used were also within the scope of what the FPGA could provide.

One of the biggest issues I had when debugging my overall module was the amount of propagation delay I had because of somewhat "heavy" computation which used depended on a lot of inputs. I couldn't afford this since I had to do everything in one clock cycle, since there was only a limited amount of time the hblanking could provide. This led me to delay all the inputs by one clock cycle which was good, since I would be using up only an extra clock cycle as mentioned previously. Another issue I had was the number of if and else if statements I had in my code, with more than half of those statements in the sprite table module. One improvement I made to my code was the use of case statements. The optimization of my code in the sprite table module managed to decrease the computation and propagation delays by nearly 30ns, which was a lot considering each clock cycle was 83ns. Another problem I had was that I didn't clear my registers in the line\_reg after each line drawn on the screen. This presented problems since there would be times when I was not supposed to have an x-hit, but had one anyway.

# **5** Conclusion

Design which facilitated easy interfacing between three separate components was the lesson to be learnt from this experience. The design process itself consumed a large part of our project time. It was particularly challenging to work out the timing between the three separate components, especially since the Video Controller needed to output to the screen continuously. We learnt how to bypass such timing constraints with clever design techniques, which allow the processing time of the Game Controller to occur during the blanking of the vertical signal from the Video Controller. We also learnt about designing modules while taking into consideration the total size of the FPGA and EAB's. At the very beginning, each of us was busy designing his/her own module that we completely overlooked the size and pin limitations of the FPGA. The progress of the project should have been planning more carefully, allocating more time towards implementation and interfacing, since we learnt that interfacing consumes a very large amount of time. In fact, we couldn't manage to fit the Resizer Module onto one FPGA, and in the end we did not have time to interface with the Resizer. Yet, the project, although challenging, was a greatly informative experience, and although our results did not match our original expectations, we were quite satisfied with the progress we made.

# 6 Appendix: Verilog Code

# **6.1 Game Controller Unit**

#### 6.1a Controller

module controller(user\_in, clk, xcoor, ycoor, size, sprite\_no, le\_size, frame\_done, ready\_sprite, start\_sprite, reset apply, data\_out, data\_in, process\_done, wr, reset\_done, interrupt\_valid, enable, instruction); input [4:0] user\_in; input clk, frame\_done, start\_sprite; output [7:0] data out, data in; output [19:0] instruction; output[8:0] xcoor; output [7:0] ycoor; output [2:0] size, enable; output [4:0] sprite\_no; output wr; output le size, process done, reset apply, ready sprite, reset done, interrupt valid; wire stop, wr, busy, temp\_reg3, temp\_reg4, reset\_done, reset\_apply, interrupt\_valid; wire [2:0] pcsel, size\_dat; wire [1:0] stack\_sel; wire [2:0] enable; wire [6:0] reg no; wire [8:0] branch, call, pc; wire [7:0] data\_in, data\_out; wire [19:0] instruction;

insrom myrom(pc, instruction);

decoder insdecoder(clk, user\_in, instruction, pcsel, stack\_sel, enable, data\_out, data\_in, le\_size, size, stop,branch,

call, reg\_no, wr, temp\_reg3, temp\_reg4, frame\_done, reset\_apply, reset\_done, reset\_reg, interrupt\_valid);

pc mypc(clk, reset\_apply, pcsel,call, branch,frame\_done, enable, pc, stack\_sel, stop, reset\_done, tos, nos);

reg\_file regfile(clk, reset\_apply, start\_sprite, frame\_done, wr, data\_in, data\_out, reg\_no, sprite\_no, xcoor, ycoor, ready\_sprite, stop, wr\_sprite, wr\_xcoor, wr\_ycoor, reset\_done, process\_done, interrupt\_valid);

endmodule

#### 6.1b Decoder

output [8:0] branch, call; output [6:0] reg\_no; reg [2:0] enable; reg stack\_sel, size\_en, sizen, le\_size, stop, reset, wr, intreg1, intreg2, intreg3, intreg4, apply\_reset, reset reg; reg temp\_reg3, temp\_reg4; reg [7:0] data\_in, temp\_reg1, temp\_reg2; reg [2:0] size\_dat, pcsel; reg [3:0] state; reg [8:0] branch, call; reg [6:0] reg no; reg [4:0] user in old, control; parameter op\_assign=0; parameter op addc = 1; parameter op\_branchcond = 2; parameter op\_compeq =3; parameter op\_beq = 4; parameter op\_call = 5; parameter op\_return = 6; parameter op\_stop = 7; parameter op\_size = 8; parameter op compeqc = 9;parameter op\_comple = 10; parameter op\_complec = 11; parameter op and = 12; parameter op\_or = 13; parameter op\_eqin = 14; parameter op\_bne = 15; parameter state write = 0; parameter state\_op = 1; parameter state\_process = 2; parameter state read 1 = 3; parameter state\_read2= 4; parameter state\_incpc = 5; parameter state idle = 6;parameter state\_reset = 7; parameter state\_interrupt = 8; always @ (posedge clk) begin //Synchronizer for the inputs user\_in\_old <= user\_in; control <= user\_in\_old; reset <= control[0]; sizen <= size\_en;</pre> le\_size <= sizen;</pre> wr <=0;

wr <=0; branch <= instruction[8:0]; call <= instruction [8:0];</pre>

```

stop \leq 0;

size_en \leq 0;

stack_sel <=0;</pre>

apply_reset<=0;

enable <=0;

reset_reg <= reset? 1: reset_reg;</pre>

if(reset_reg)

begin

pcsel <=4;

enable <= 0;

stack_sel <= 0;</pre>

stop \leq 0;

wr<=0;

reset_reg <=0;

apply_reset <=1;

state <= state_reset;</pre>

end

else if((control [4:1] !=0) && interrupt_valid)

begin

call<= 461;

pcsel \ll 2;

enable \leq 7;

stack sel <=0;

state <= state_interrupt;</pre>

end

else case(state)

state_reset:

begin

if(reset_done)

begin

state<= state_op;</pre>

reset_reg <=0;

data_in <=0;

apply_reset <=0;

end

end

state_interrupt:

begin

enable <=0;

pcsel<=4;

state<= state_incpc;</pre>

end

state_write:

begin

wr<=1;

state <= state_incpc;</pre>

pcsel <=0;

end

state_incpc:

begin

if(stop)

begin

pcsel <=4;

state <= state_idle;</pre>

end

```

```

else

begin

pcsel \ll 4;

state <= state_op;</pre>

end

end

state_idle:

begin

if(frame_done)

begin

state<= state_op;</pre>

pcsel \ll 4;

end

end

state_process:

begin

case(instruction[19:16])

op_addc:

begin

data_in<= temp_reg1 +

instruction[7:0];

state<= state_write;</pre>

end

op_compeq:

begin

case (instruction[1:0])

0: intreg1 \leq=

(temp\_reg1 == temp\_reg2)? 1: 0;

1: intreg2 \leq=

(temp\_reg1 == temp\_reg2)? 1: 0;

2: intreg3 <=

(temp\_reg1 == temp\_reg2)? 1: 0;

3: intreg4 <=

(temp\_reg1 == temp\_reg2)? 1: 0;

endcase

state<= state_incpc;</pre>

pcsel \ll 0;

end

op_comple:

begin

case (instruction[1:0])

0: intreg1 <=

(temp_reg1 <= temp_reg2)? 1: 0;

1: intreg2 \leq=

(temp_reg1 <= temp_reg2)? 1: 0;

2: intreg3 <=

(temp_reg1 <= temp_reg2)? 1: 0;

3: intreg4 <=

(temp_reg1 <= temp_reg2)? 1: 0;

endcase

state<= state_incpc;</pre>

pcsel \ll 0;

end

op_complec:

begin

```

case (instruction[1:0]) 0: intreg1 <=

1: intreg2  $\leq$ =

2: intreg3 <=

3: intreg4 <=

endcase

state<= state\_incpc;

pcsel <= 0;</pre>

op\_compeqc: begin case (instruction[1:0]) 0: intreg1 <=

U

1: intreg2 <=

2: intreg3 <=

3: intreg4 <=

```

endcase

```

state<= state\_incpc;

pcsel <= 0;</pre>

```

state <= state_incpc;

pcsel <=0;</pre>

```

1

```

end

```

end default: begin

end

endcase

temp\_reg2 <= data\_out; reg\_no <= instruction [15:9]; state <= state\_read2;</pre>

end

state\_read2: begin

end

begin

state\_read1:

temp\_reg1 <= data\_out;

state <= state\_process;</pre>

end

```

state_op:

case(instruction[19:16])

op_assign:

begin

```

reg\_no <= instruction [15:9]; data\_in <= instruction [7:0]; enable <=0; state<= state\_write;</pre>

```

end

```

```

op_addc:

```

48

(temp\_reg1 <= instruction[8:2])? 1: 0;

$(temp\_reg1 \le instruction[8:2])? 1: 0;$

(temp\_reg1 <= instruction [8:2])? 1: 0;

(temp\_reg1 <= instruction[8:2])? 1: 0;

(temp\_reg1 == instruction[8:2])? 1: 0;

(temp\_reg1 == instruction[8:2])? 1: 0;

(temp\_reg1 == instruction [8:2])? 1: 0;

$(temp\_reg1 == instruction[8:2])? 1: 0;$

```

begin

reg_no <= instruction [15:9];

enable <=0;

state<= state_read1;</pre>

end

op_branchcond:

begin

if(instruction[15:11] == control)

pcsel \ll 1;

else

begin

pcsel <=0;

end

enable \leq 0;

state <= state_incpc;</pre>

end

op_compeq:

begin

reg_no <= instruction[8:2];</pre>

state<= state_read1;</pre>

enable \leq 0;

end

op_beq:

begin

case(instruction[15:14])

0: pcsel <= intreg1? 0:1;

1: pcsel <= intreg2? 0:1;

2: pcsel <= intreg3? 0:1;

3: pcsel <= intreg4? 0:1;

endcase

enable <= 0;

state <= state_incpc;</pre>

end

op_bne:

begin

case(instruction[15:14])

0: pcsel <= intreg1? 1:0;

1: pcsel <= intreg2? 1:0;

2: pcsel <= intreg3? 1:0;

3: pcsel <= intreg4? 1:0;

endcase

enable \leq 0;

state <= state_incpc;</pre>

end

op_call:

begin

pcsel <= 2;

enable \leq 3;

```

stack\_sel <= 0; state <= state\_incpc;</pre>

end

```

op_return:

begin

pcsel <=3;

stack_sel <= 1;</pre>

enable \leq 1;

state <= state_incpc;</pre>

end

op_stop:

begin

stop <= 1;

enable\leq = 0;

pcsel \ll 0;

state <= state_incpc;</pre>

end

op_size:

begin

size_dat<= instruction [2:0];</pre>

size_en \leq 1;

pcsel \ll 0;

enable <= 0;

state <= state_incpc;</pre>

end

op_comple:

begin

reg_no <= instruction[8:2];</pre>

state<= state_read1;</pre>

enable \leq 0;

end

op_compeqc:

begin

reg_no <= instruction[15:9];</pre>

state<= state_read2;</pre>

enable \leq 0;

//pcsel <= 4;

end

op_complec:

begin

reg_no <= instruction[15:9];</pre>

state<= state_read2;</pre>

enable \leq 0;

end

op_and:

begin

case(instruction [11:10])

0: intreg1 <= (temp_reg3 &&

temp_reg4)? 1:0;

1: intreg2 <= (temp_reg3 &&

temp_reg4)? 1:0;

2: intreg3 <= (temp_reg3 &&

temp_reg4)? 1:0;

3: intreg4 <= (temp_reg3 &&

temp_reg4)? 1:0;

endcase

enable <=0;

pcsel <=0;

state <= state_incpc;</pre>

```

op\_or: begin case(instruction [11:10]) 0: intreg1 <= (temp\_reg3 || temp\_reg4)? 1:0; 1: intreg2 <= (temp\_reg3 || temp\_reg4)? 1:0; 2: intreg3 <= (temp\_reg3 || temp\_reg4)? 1:0; 3: intreg4 <= (temp\_reg3 || temp\_reg4)? 1:0; endcase enable <=0; pcsel <=0; state <= state\_incpc;</pre> end op\_eqin: begin case(instruction [12:11]) 0: intreg1 <= (temp\_reg3 == instruction[10]); 1: intreg2 <=(temp\_reg3 == instruction[10]); 2: intreg3 <= (temp\_reg3 == instruction[10]); 3: intreg4 <=(temp\_reg3 == instruction[10]); endcase  $pcsel \ll 0;$ enable <=0; state <= state\_incpc;</pre> end endcase

end

endcase

end

always @(state) begin if(state == state\_op) begin case(instruction[19:16]) op\_and: begin case(instruction [15:14]) 0: temp\_reg3 <= intreg1; 1: temp\_reg3 <= intreg2;

2: temp\_reg3 <= intreg3;

3: temp\_reg3 <= intreg4; endcase case(instruction [13:12]) 0: temp\_reg4 <= intreg1; 1: temp\_reg4 <= intreg2; 2: temp\_reg4 <= intreg3; 3: temp\_reg4 <= intreg4; endcase end op\_or: begin case(instruction [15:14]) 0: temp\_reg3 <= intreg1; 1: temp\_reg3 <= intreg2; 2: temp\_reg3 <= intreg3; 3: temp\_reg3 <= intreg4; endcase case(instruction [13:12]) 0: temp\_reg4 <= intreg1; 1: temp\_reg4 <= intreg2; 2: temp\_reg4 <= intreg3; 3: temp\_reg4 <= intreg4; endcase end op\_eqin: begin case(instruction[15:13]) 0: temp\_reg3 <= control[0]; 1: temp\_reg3 <= control [1]; 2: temp\_reg3 <= control [2]; 3: temp\_reg3 <= control[3]; 4: temp\_reg3 <= control [4]; default: temp\_reg3 <=0;</pre> endcase end default: begin temp\_reg3<=0; temp\_reg4 <=0;</pre> end endcase end else begin temp\_reg3 <=0; temp\_reg4 <=0; end

end

endmodule

## 6.1c PC

module pc(clk, reset\_apply, pcsel,call, branch,frame\_done, enable, pc, stack\_sel, stop, reset\_done, tos, nos);

```

input clk, frame_done, stack_sel, stop, reset_apply, reset_done;

output[8:0] tos, nos;

input [2:0] pcsel;

input [2:0] enable;

input [8:0] call, branch;

output[8:0] pc;

wire [8:0] new_pc, return;

reg [8:0] pc;

reg[8:0] tos, nos;

reg [1:0] state;

parameter state_idle = 0;

parameter state_busy = 1;

parameter state_reset = 3;