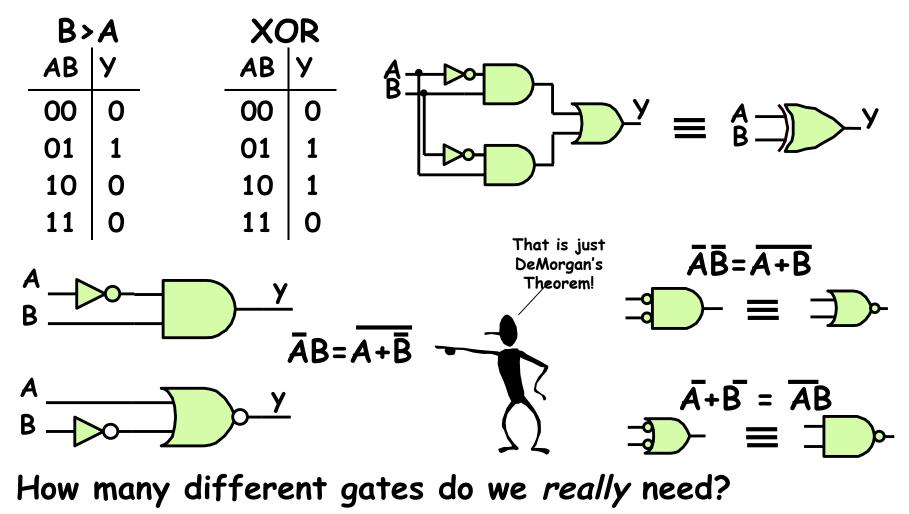

Fortunately, we can get by with a few basic gates...

AND, OR, and NOT are sufficient... (cf Boolean Expressions):

Lecture 3, Slide 1

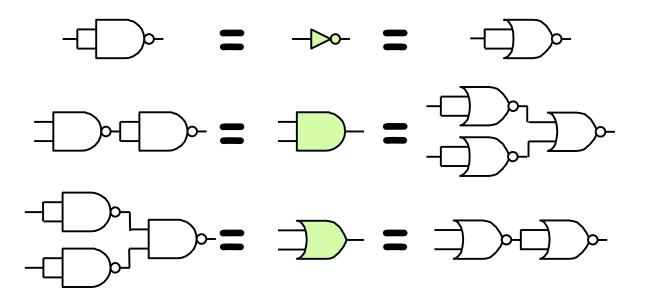

#### One will do!

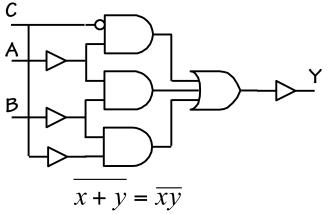

NANDs and NORs are <u>universal</u>:

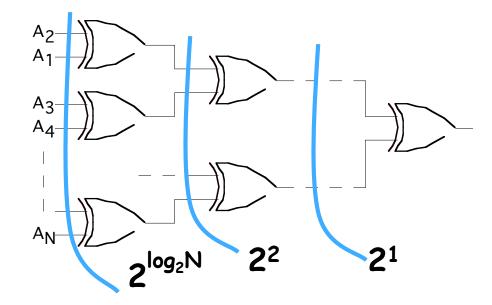

Ah!, but what if we want more than 2 inputs?

Lecture 3, Slide 2

#### I think that I shall never see a circuit lovely as...

N-input TREE has O( <u>log N</u> ) levels...

Signal propagation takes O(  $\log N$  ) gate delays.

Question: Can EVERY N-Input Boolean function be implemented as a tree of 2-input gates?

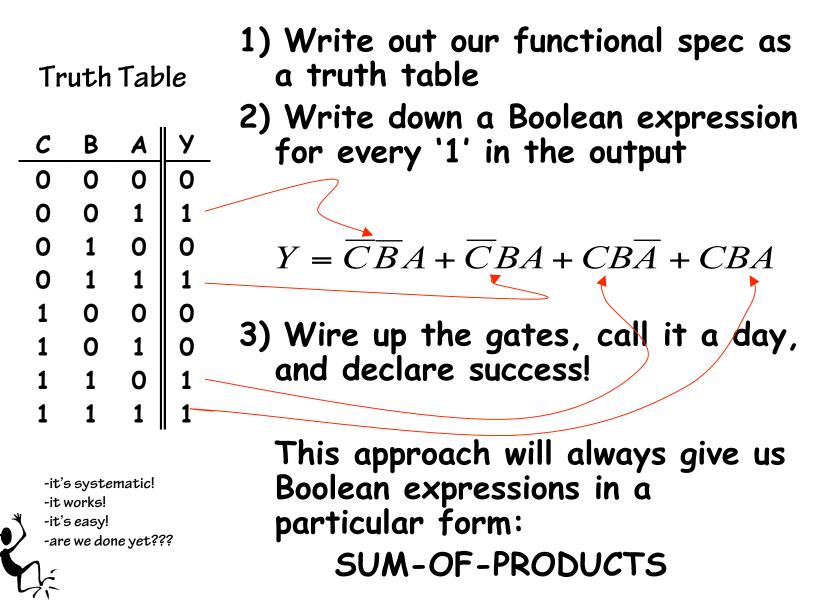

## Here's a Design Approach

6.111 Fall 2007

## Straightforward Synthesis

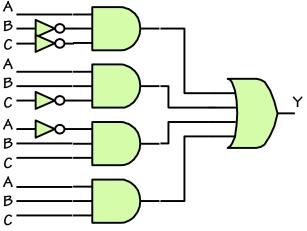

We can implement SUM-OF-PRODUCTS with just three levels of logic.

INVERTERS/AND/OR

Propagation delay --No more than "3" gate delays (well, it's actually O(log N) gate delays)

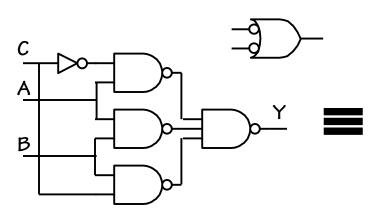

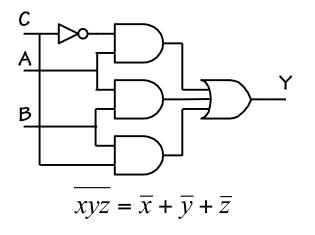

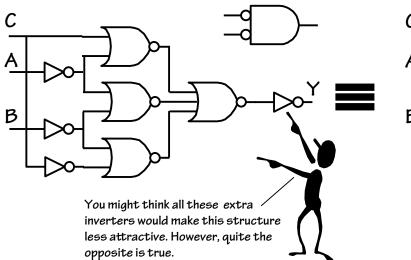

## Practical SOP Implementation

• NAND-NAND  $\overline{AB} = \overline{A} + \overline{B}$

"Pushing Bubbles"

· NOR-NOR

$\overline{A}\overline{B}=\overline{A+B}$

### Logic Simplification

Can we implement the same function with fewer gates? Before trying we'll add a few more tricks in our bag. BOOLEAN ALGEBRA:

OR rules: AND rules: Commutative: Associative: Distributive: Complements: Absorption:

Reduction: DeMorgan's Law: a + 1 = 1, a + 0 = a, a + a = a a 1 = a, a0 = 0, aa = a a + b = b + a, ab = ba (a + b) + c = a + (b + c), (ab)c = a(bc) a(b+c) = ab + ac, a + bc = (a+b)(a+c)  $a + \overline{a} = 1, \quad a\overline{a} = 0$   $a + ab = a, \quad a + \overline{a}b = a + b$   $a(a + b) = a, \quad a(\overline{a} + b) = ab$   $ab + \overline{a}b = b, \quad (a + b)(\overline{a} + b) = b$  $\overline{a} + \overline{b} = \overline{ab}, \quad \overline{a}\overline{b} = \overline{a+b}$

# **Boolean Minimization:**

An Algebraic Approach

Lets (again!) simplify  $Y = \overline{CBA} + CB\overline{A} + CBA + \overline{CBA}$ Using the identity  $\alpha A + \alpha \overline{A} = \alpha$ For any expression  $\alpha$  and variable A:

$$Y = \overline{CBA} + CB\overline{A} + CBA + \overline{CBA}$$

$$Y = \overline{CBA} + CB + \overline{CBA}$$

$$Y = \overline{CA} + CB$$

$$A \text{ program to do That!}$$

Can't he come up with a <u>new</u> example???

Hey, I could write

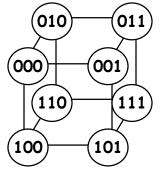

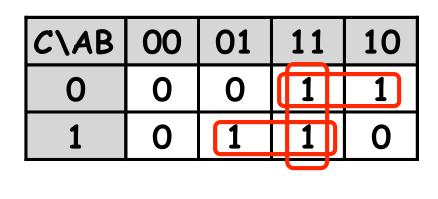

#### Karnaugh Maps: A Geometric Approach

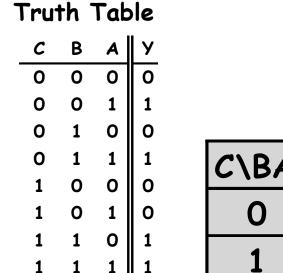

K-Map: a truth table arranged so that terms which differ by exactly one variable are adjacent to one another so we can see

potential reductions easily. Here's the layout of a 3-variable K-map filled

in with the values from our truth table:

| C\AB | 00 | 01 | 11 | 10 |

|------|----|----|----|----|

| 0    | 0  | 0  | 1  | 1  |

| 1    | 0  | 1  | 1  | 0  |

It's cyclic. The left edge is adjacent to the right edge. (It's really just a flattened out cube).

Lecture 3, Slide 9

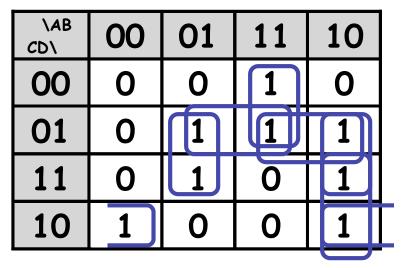

# On to Hyperspace

4-variable K-map for a multipurpose logic gate:

|                                                                   | A·B                   | if CD = 00            | \AB<br>CD\ | 00 | 01 | 11 | 10 |

|-------------------------------------------------------------------|-----------------------|-----------------------|------------|----|----|----|----|

| $\mathbf{Y} = \begin{cases} \mathbf{B} \\ \mathbf{B} \end{cases}$ | A + B                 | if CD = 01            | 00         | 0  | 0  | 1  | 0  |

|                                                                   |                       | if CD = 10            | 01         | 0  | 1  | 1  | 1  |

|                                                                   |                       |                       | 11         | 0  | 1  | 0  | 1  |

|                                                                   | [ <b>A</b> ⊕ <b>B</b> | $\oplus$ B if CD = 11 | 10         | 1  | 0  | 0  | 1  |

Again it's cyclic. The left edge is adjacent to the right edge, and the top is adjacent to the bottom.

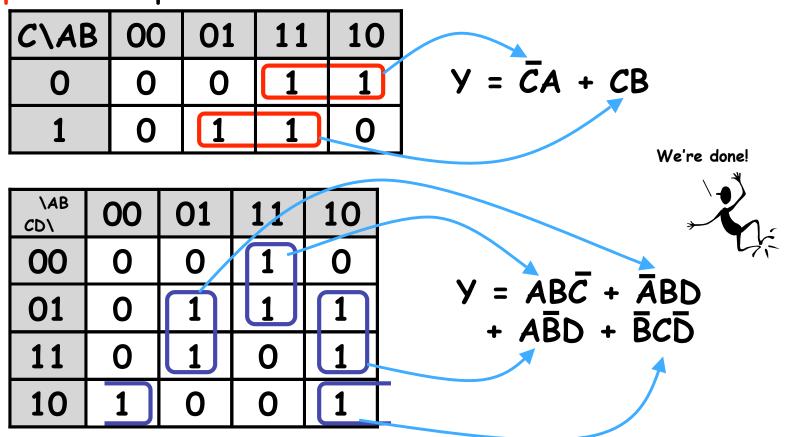

# Finding Subcubes

We can identify clusters of "irrelevent" variables by circling adjacent subcubes of 1s. A subcube is just a lower dimensional cube.

The best strategy is generally a greedy one.

- Circle the largest N-dimensional subcube (2<sup>N</sup> adjacent 1's)

4x4, 4x2, 4x1, 2x2, 2x1, 1x1

- Continue circling the largest remaining subcubes (even if they overlap previous ones)

- Circle smaller and smaller subcubes until no 1s are left.

#### Write Down Equations

Write down a product term for the portion of each cluster/subcube that is invariant. You only need to include enough terms so that all the 1's are covered. Result: a minimal sum of products expression for the truth table.

## **Recap: K-map Minimization**

- 1) Copy truth table into K-Map

- 2) Identify subcubes,

selecting the largest available subcube at each step, even if it involves some overlap with previous cubes, until all ones are covered. (Try: 4x4, 2x4 and 4x2, 1x4 and 4x1, 2x2, 2x1 and 1x2, finally 1x1)

3) Write down the minimal SOP realization

JARGON: The circled terms are called *implicants*. An implicant not completely contained in another implicant is called a *prime implicant*.

| C\BA | 00 | 01 | 11 | 10 |

|------|----|----|----|----|

| 0    | 0  | 1  | 1  | 0  |

| 1    | 0  | 0  | 1  | 1  |

$Y = \overline{C}A + CB$

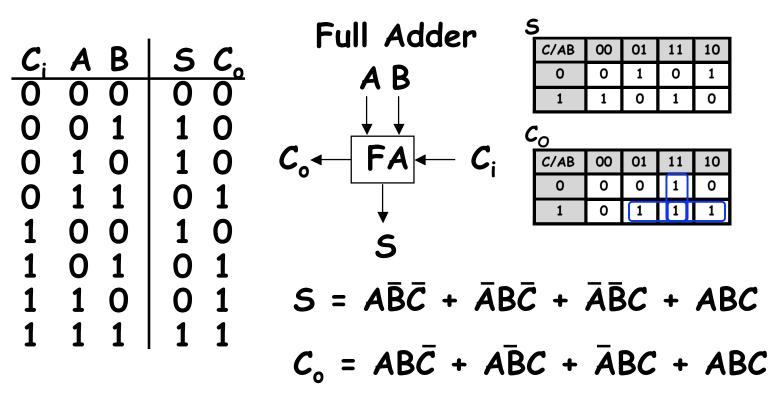

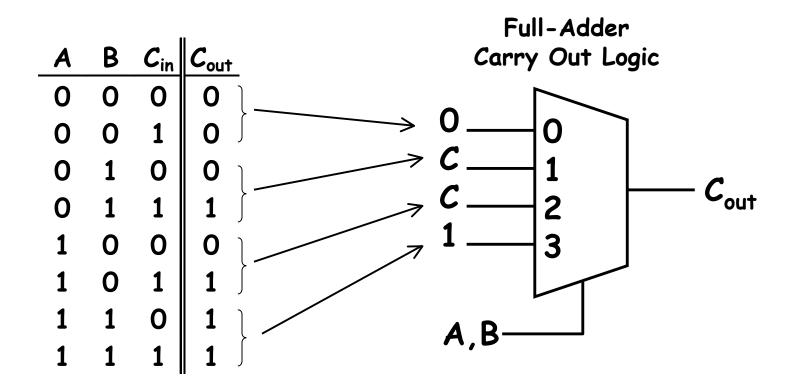

Can simplify the carry out easily enough, eg...

$C_{o} = BC + AB + AC$

But, the sum, S, doesn't have a simple sum-of-products implementation even though it can be implemented using only two 2-input XOR gates. 6.111 Fall 2007

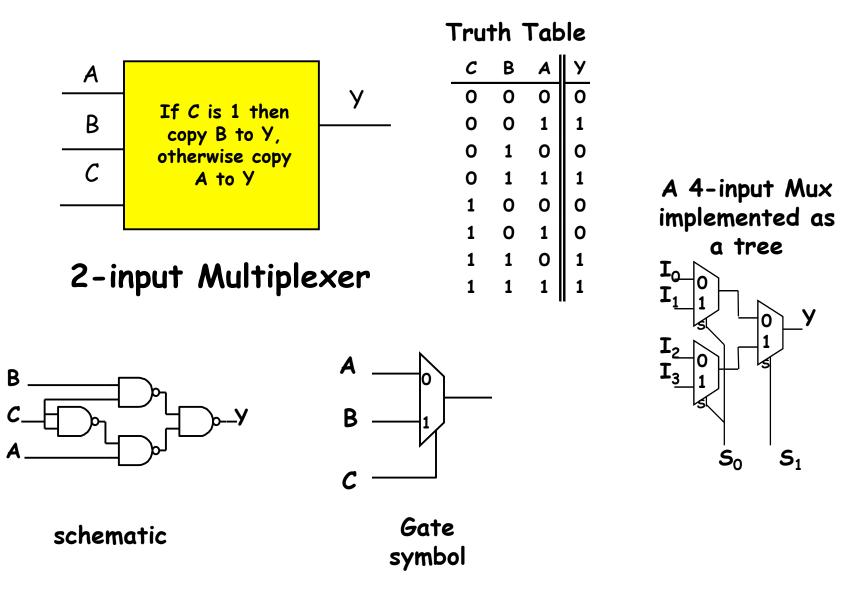

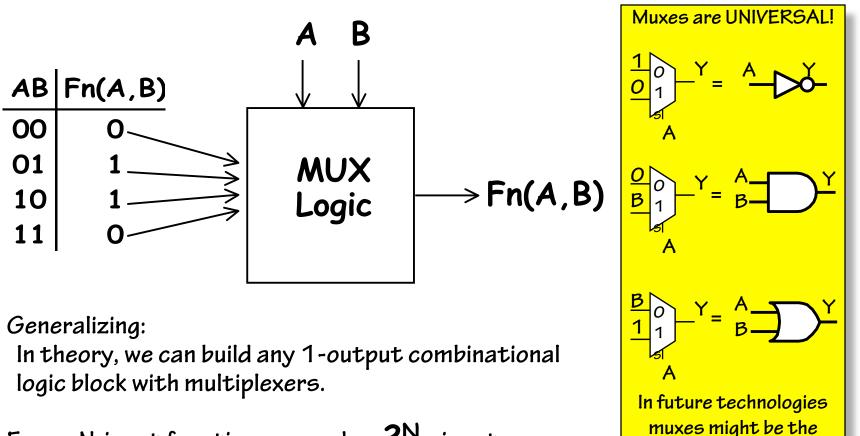

### Logic Synthesis Using MUXes

#### Systematic Implementation of Combinational Logic

#### Systematic Implementation of Combinational Logic

Same function as on previous slide, but this time let's use a 4-input mux

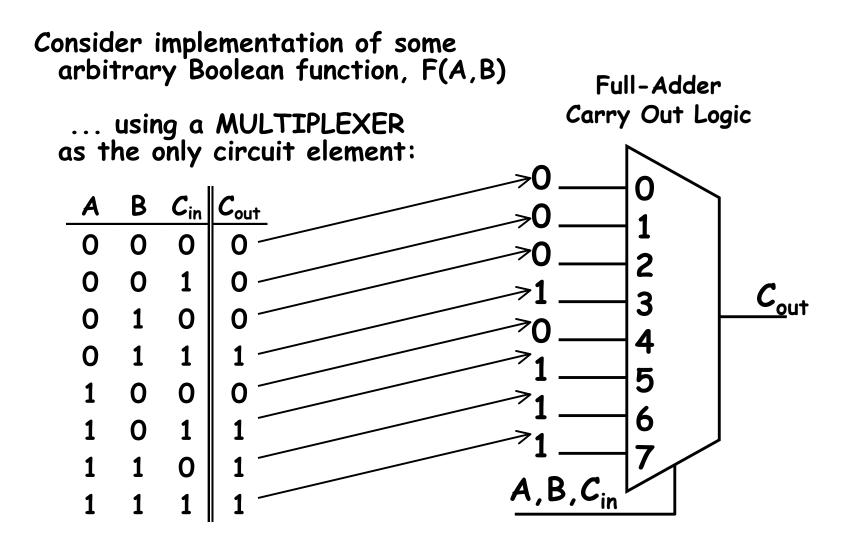

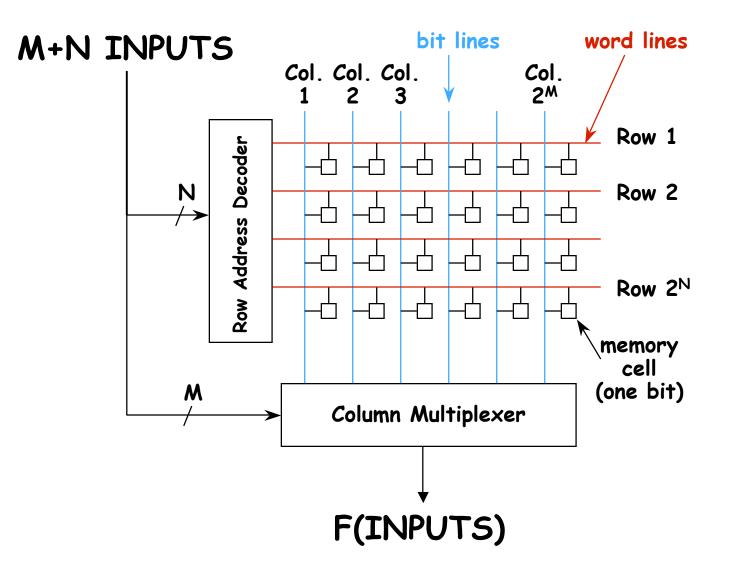

# General Table Lookup Synthesis

For an N-input function we need a  $2^{N}$  input mux.

```

BIG Multiplexers?

How about 10-input function? 20-input?

```

"natural gate".

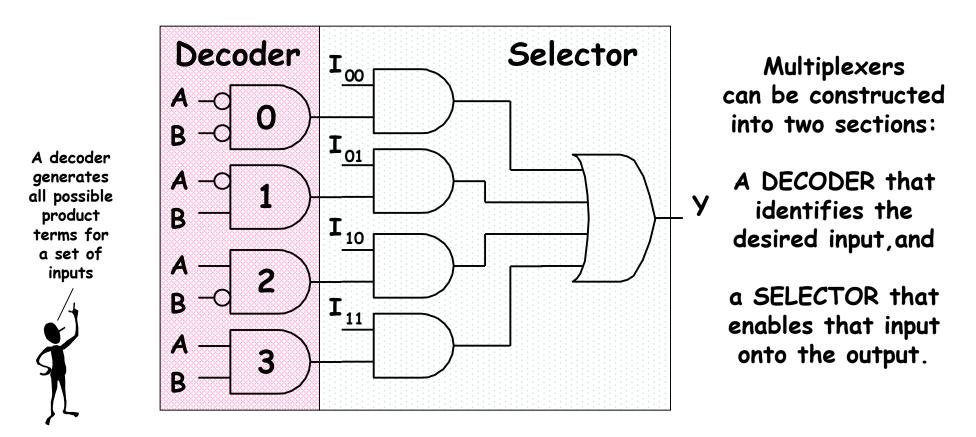

# A Mux's Guts

Hmmm, by sharing the decoder part of the logic MUXs could be adapted to make lookup tables with any number of outputs

#### Using Memory as a Programmable Logic Device

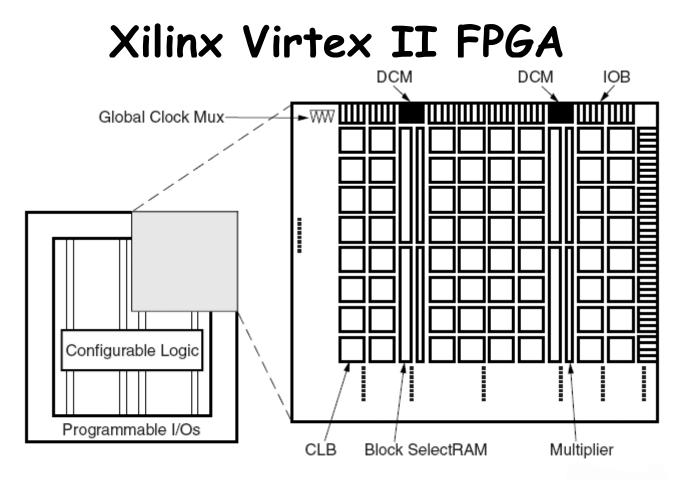

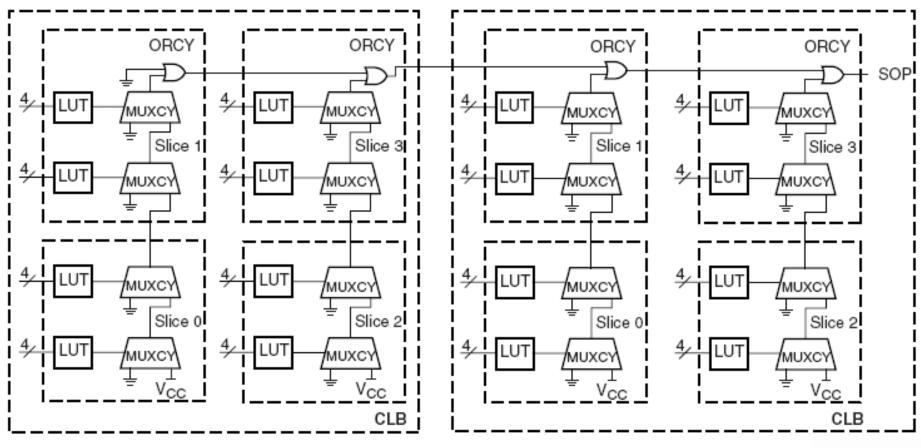

Virtex-II Architecture Overview

#### XC2V6000:

- 957 pins, 684 IOBs

- CLB array: 88 cols x 96/col = 8448 CLBs

- 18Kbit BRAMs = 6 cols x 24/col = 144 BRAMs = 2.5Mbits

- 18x18 multipliers = 6 cols x 24/col = 144 multipliers

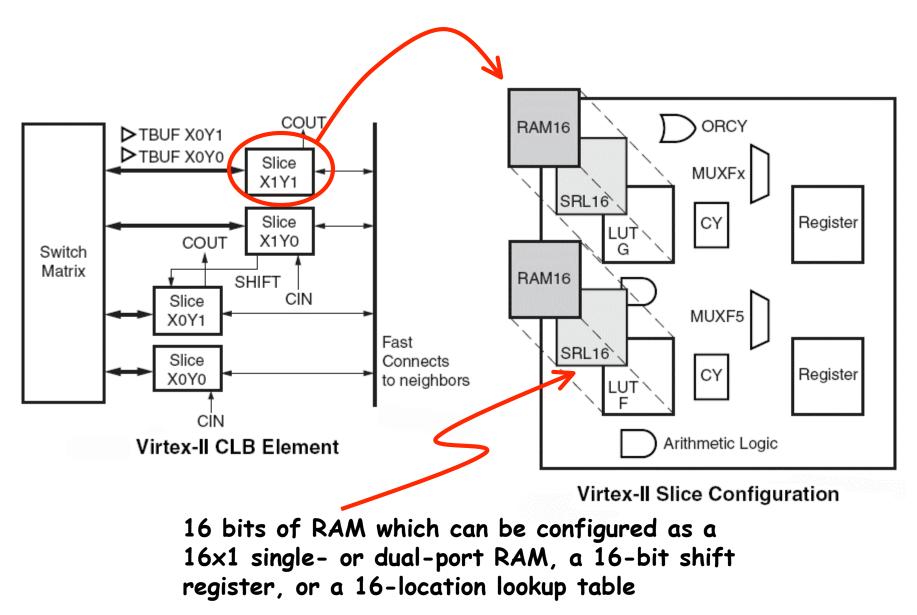

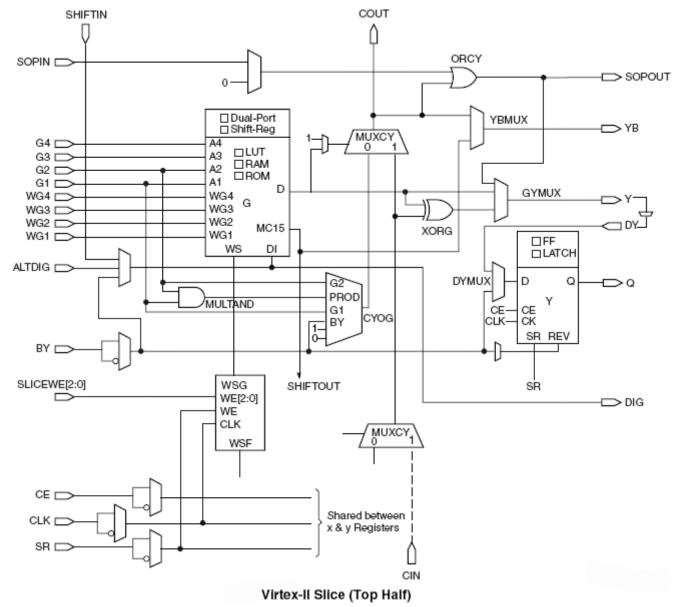

#### Virtex II CLB

#### Virtex II Sum-of-products

Horizontal Cascade Chain