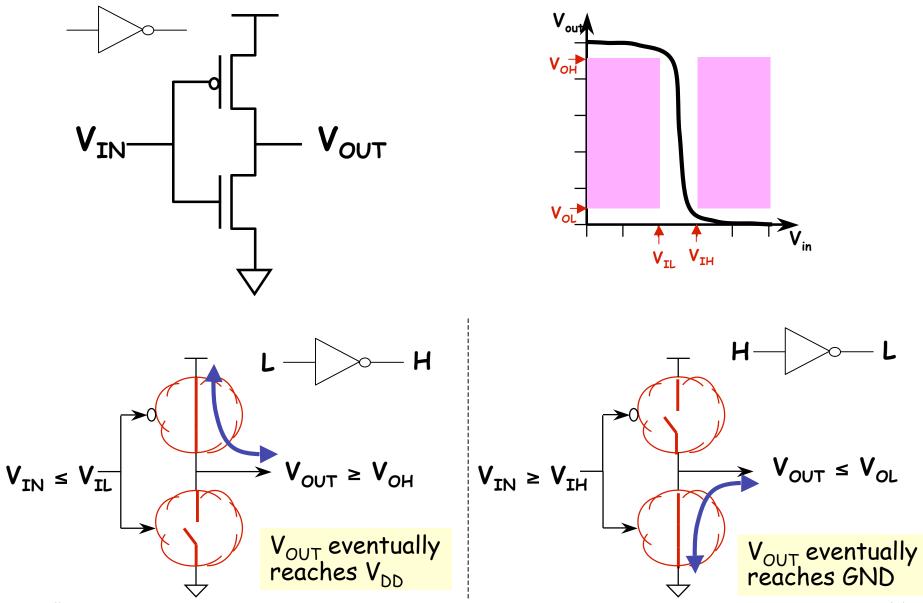

Static Discipline requires that we avoid the shaded regions aka "forbidden zones"), which correspond to valid inputs but invalid outputs. Net result: combinational devices must have GAIN > 1 and be NONLINEAR.

6.111 Fall 2007

$\partial V_{IN}$

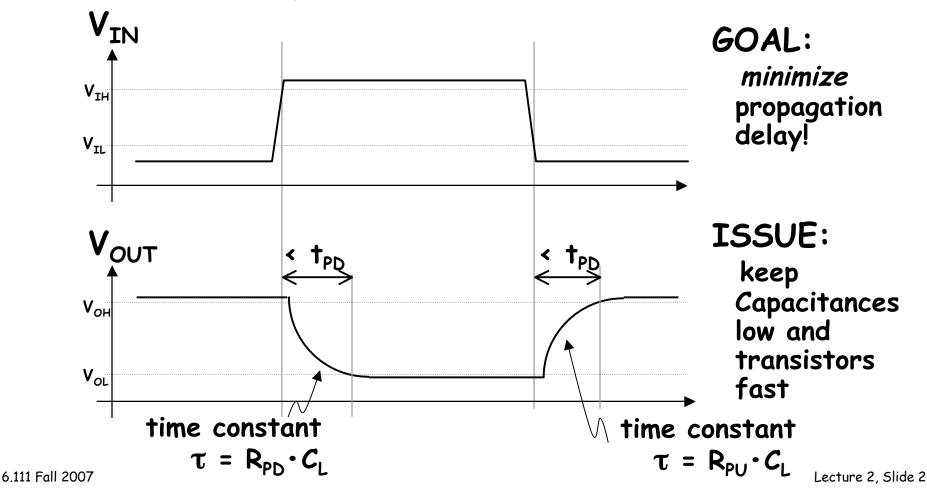

#### Due to unavoidable delays...

Propagation delay (t<sub>PD</sub>): An UPPER BOUND on the delay from valid inputs to valid outputs.

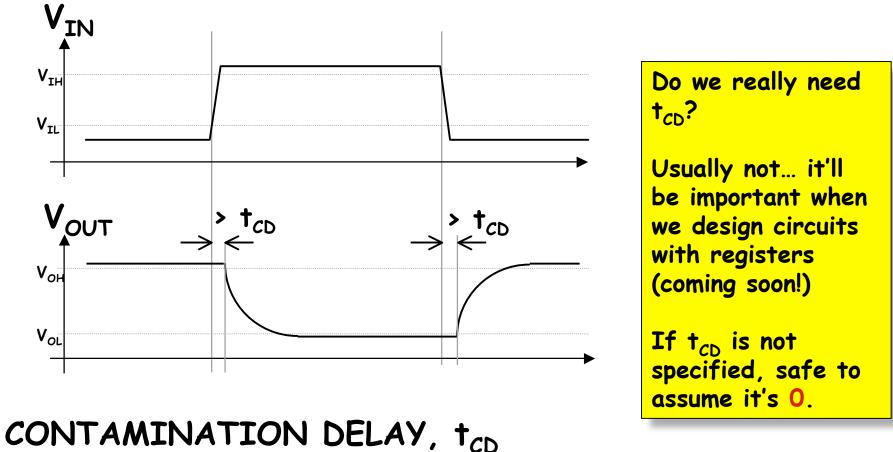

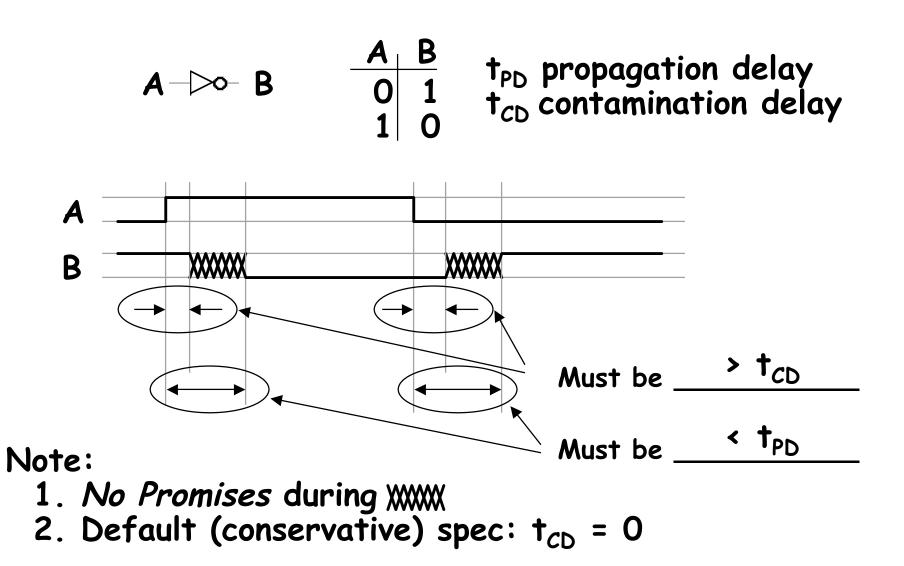

# **Contamination Delay**

an optional, additional timing spec

INVALID inputs take time to propagate, too...

A LOWER BOUND on the delay from any invalid input to an invalid output

### The Combinational Contract

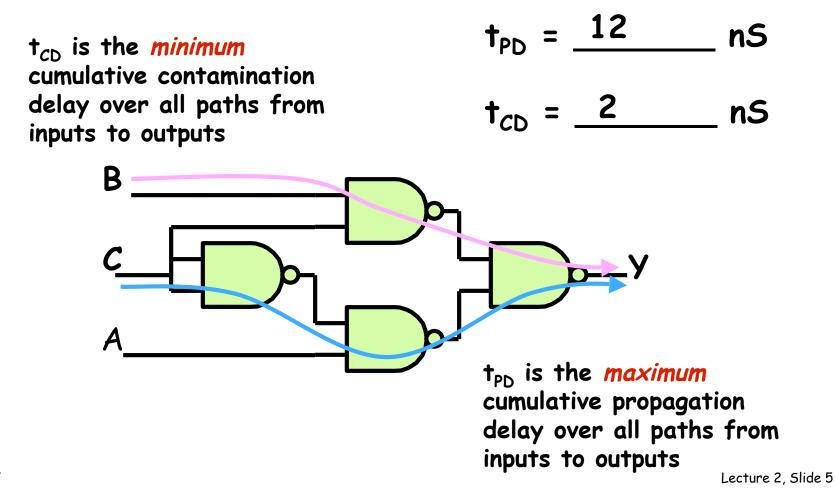

## Example: Timing Analysis

If NAND gates have a  $t_{PD}$  = 4nS and  $t_{CD}$  = 1nS

# The "perfect" logic family

- Good noise margins (want a "step" VTC)

- Implement useful selection of (binary) logic

- INVERTER, NAND, NOR with modest fan-in (4? Inputs)

- More complex logic in a single step? (minimize delay)

- Small physical size

- Shorter signal transmission distances (faster)

- Cost proportional to size (cheaper)

- Inexpensive to manufacture

- "print" technology (lithographic masks, deposition, etching)

- Large-scale integration

- Minimal power consumption

- Portable

- Massive processing without meltdown

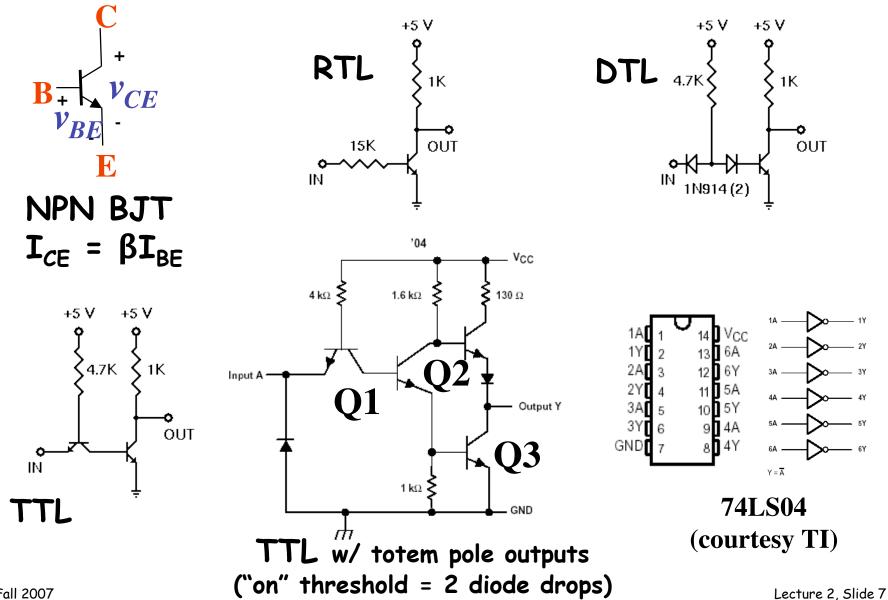

### Transitor-transitor Logic (TTL)

# TTL Signaling

- Typical TTL signaling spec

- $I_{OL} = 16mA$ ,  $I_{OH} = -0.4mA$  ( $V_{OL} = 0.4V$ ,  $V_{OH} = 2.7V$ ,  $V_{cc} = 5V$ )

- $I_{IL} = -1.6mA$ ,  $I_{IH} = 0.04mA$  ( $V_{IL}=0.8V$ ,  $V_{IH}=2.0V$ )

- Switching threshold = 1.3V

- Each input requires current flow  $(I_{IL}, I_{IH})$  and each output can only source/sink a certain amount of current  $(I_{OL}, I_{OH})$ , so

Max number of inputs that can be driven by a single output is  $min(-I_{IL}/I_{OL}, -I_{IH}/I_{OH}) \approx 10$ .

Current-based logic → power dissipation even in steady state, limitations on fanout

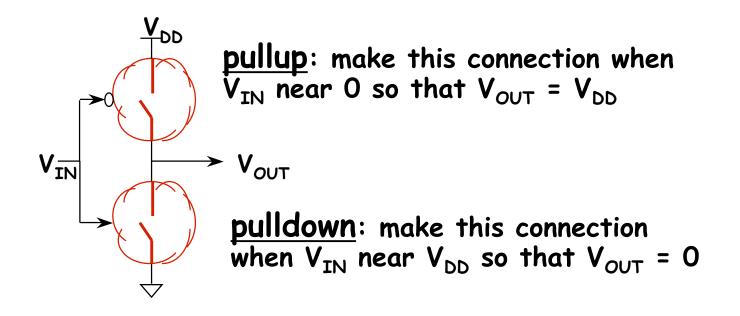

#### CMOS Gate Recipe: Think Switches

One power supply  $\rightarrow$ Two voltages ( $V_{DD}$ , GND)  $\rightarrow$ **Binary signaling**

#### Wishes Granted: CMOS

6.111 Fall 2007

# CMOS Signaling

- Typical CMOS signaling specifications:

- $V_{OL} \approx 0, V_{OH} \approx V_{DD}$  ( $V_{DD}$  is the power supply voltage)

- $V_{IL} \approx \text{just under } V_{DD}/2, V_{IH} \approx \text{just over } V_{DD}/2$

- Great noise margins!  $\sim V_{DD}/2$

- Inputs electrically isolated from outputs:

- An output can drive many, many inputs without violating signaling spec (but transitions will get slower)

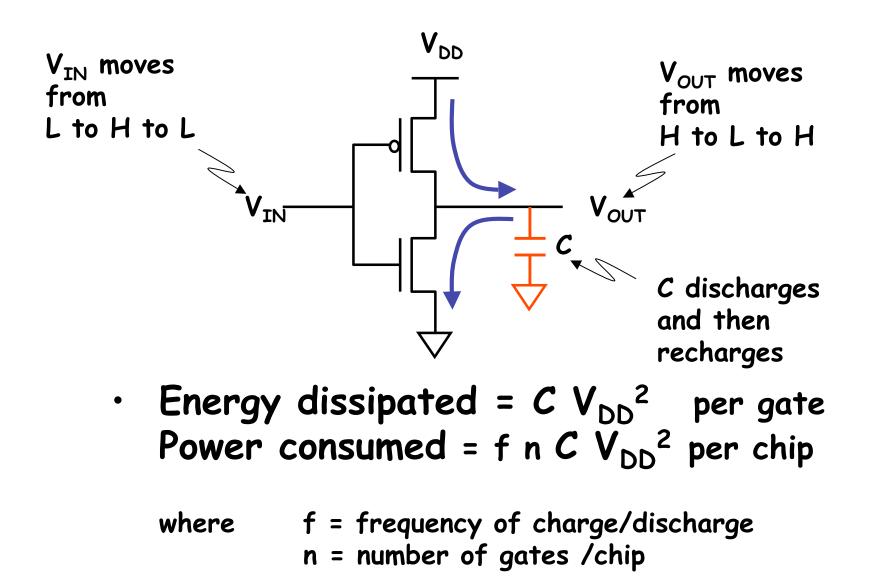

- In the steady state, signals are either "O" or "1"

- When  $V_{OUT} = OV$ ,  $I_{PD} = O$  (and  $I_{PU} = O$  since pullup is off)

- When  $V_{OUT} = V_{DD}$ ,  $I_{PU} = 0$  (and  $I_{PD} = 0$  since pulldown is off)

- No power dissipated in steady state!

- Power dissipated only when signals change (ie, power proportional to operating frequency).

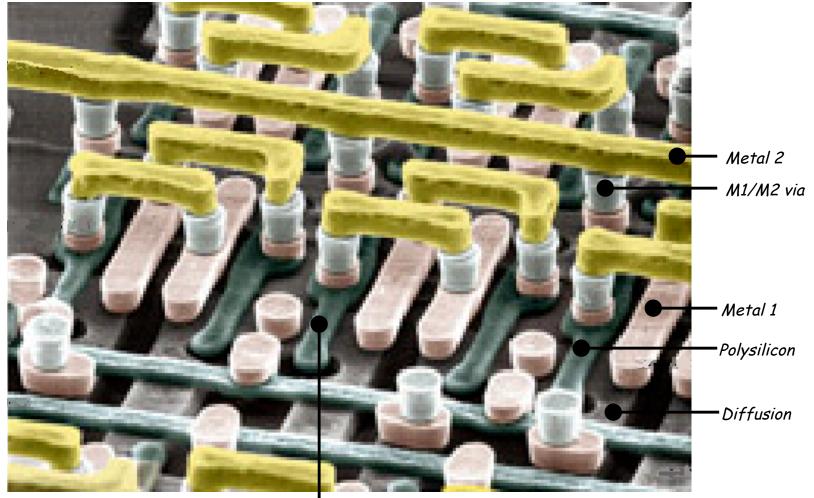

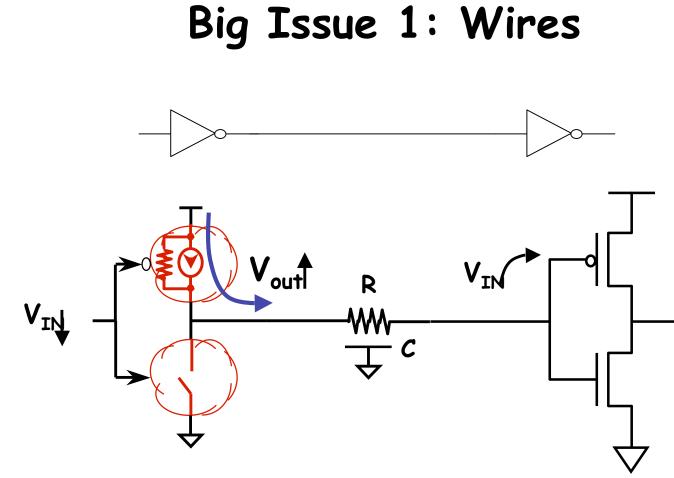

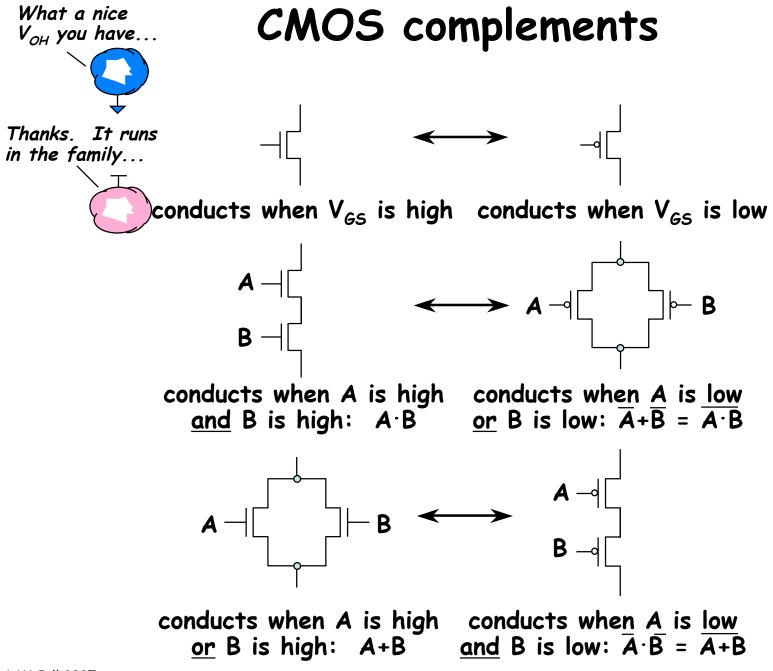

# Multiple interconnect layers

IBM photomicrograph (SiO<sub>2</sub> has been removed!)

Mosfet (under polysilicon gate)

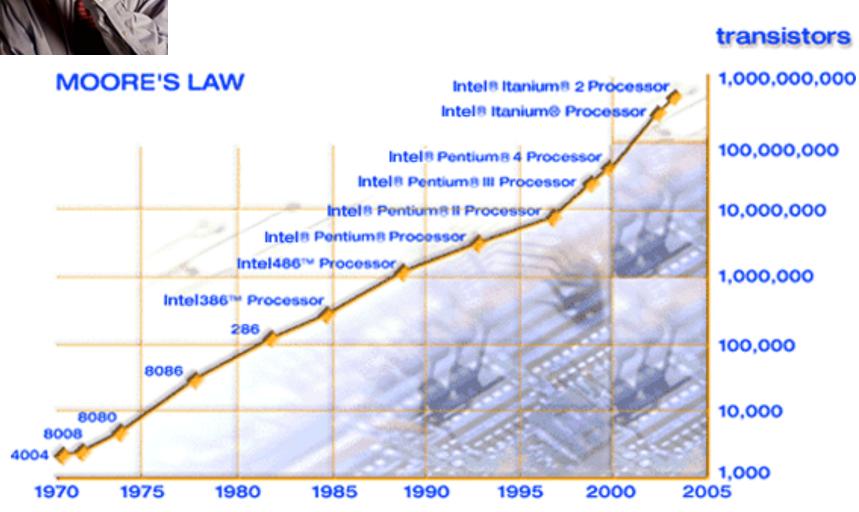

### CMOS Forever!?

6.111 Fall 2007

• Today (i.e., 65nm):

τ<sub>RC</sub> ≈ 50ps/mm Implies > 1 ns to traverse a 20mm x 20mm chip This is a long time in a 4GHz processor

### Big Issue 2: Power

32 Amps (@220v)

MIT Computation Center and Pizzeria

### Unfortunately...

- Modern chips (UltraSparc III, Power4, Itanium 2) dissipate from 80W to

150W with a Vdd ≈ 1.2V

(Power supply current is ≈ 100 Amps)

- Cooling challenge is like making the filament of a 100W incandescent lamp cool to the touch!

- •Worse yet...

- Little room left to reduce Vdd

- nC and f continue to grow

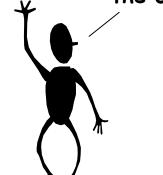

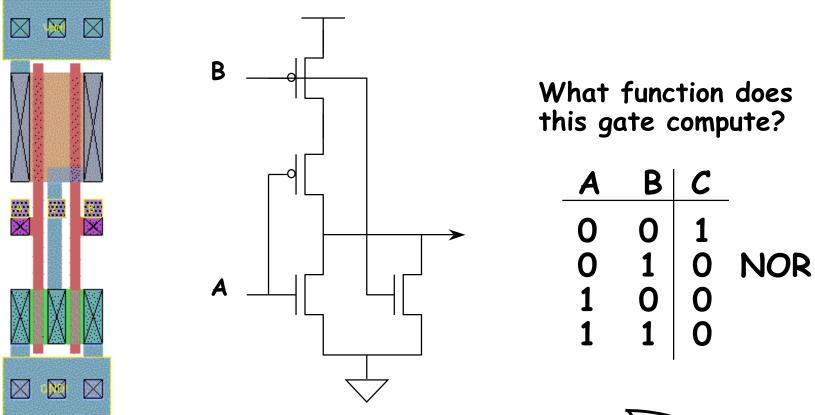

# Beyond Inverters: Complementary pullups and pulldowns

Now you know what the "C" in CMOS stands for! We want complementary pullup and pulldown logic, i.e., the pulldown should be "on" when the pullup is "off" and vice versa.

| pullup | pulldown | <b>F(A</b> <sub>1</sub> ,, <b>A</b> n) |

|--------|----------|----------------------------------------|

| on     | off      | driven "1"                             |

| off    | on       | driven "O"                             |

| on     | on       | driven "X"                             |

| off    | off      | no connection                          |

|        |          | 1                                      |

Since there's plenty of capacitance on the output node, when the output becomes disconnected it "remembers" its previous voltage – at least for a while. The "memory" is the load capacitor's charge. Leakage currents will cause eventual decay of the charge (that's why DRAMs need to be refreshed!).

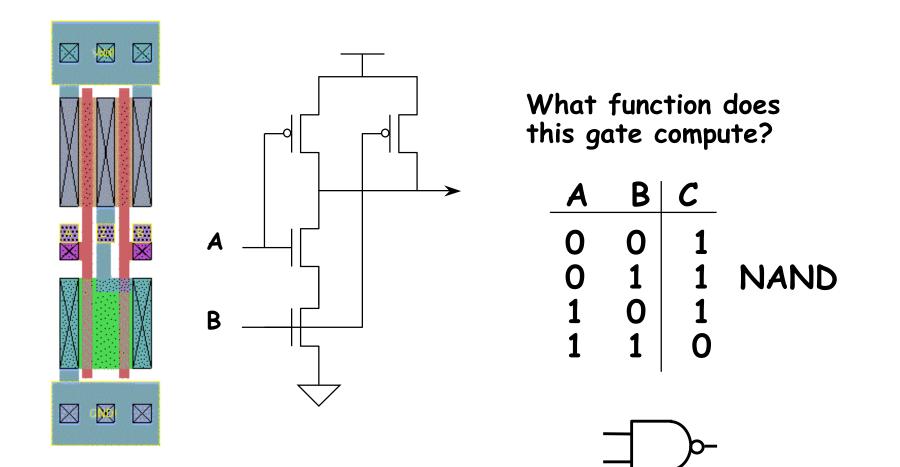

# A pop quiz!

#### Here's another...

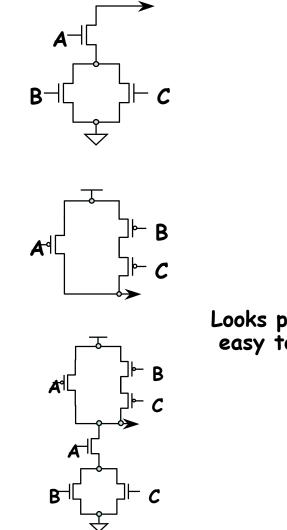

### General CMOS gate recipe

Step 1. Figure out pulldown network that does what you want,  $e.q., F = \overline{A^*(B+C)}$ (What combination of inputs generates a low output?)

Step 2. Walk the hierarchy replacing nfets with pfets, series subnets with parallel subnets, and parallel subnets with series subnets

Step 3. Combine pfet pullup network from Step 2 with nfet pulldown network from Step 1 to form fully-complementary CMOS gate.

Looks pretty easy to do!

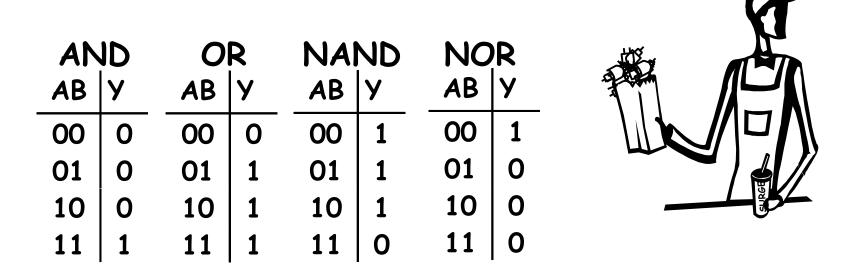

#### **Basic Gate Repertoire**

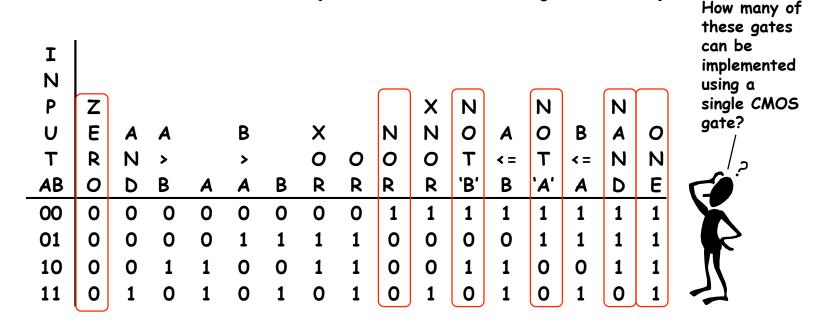

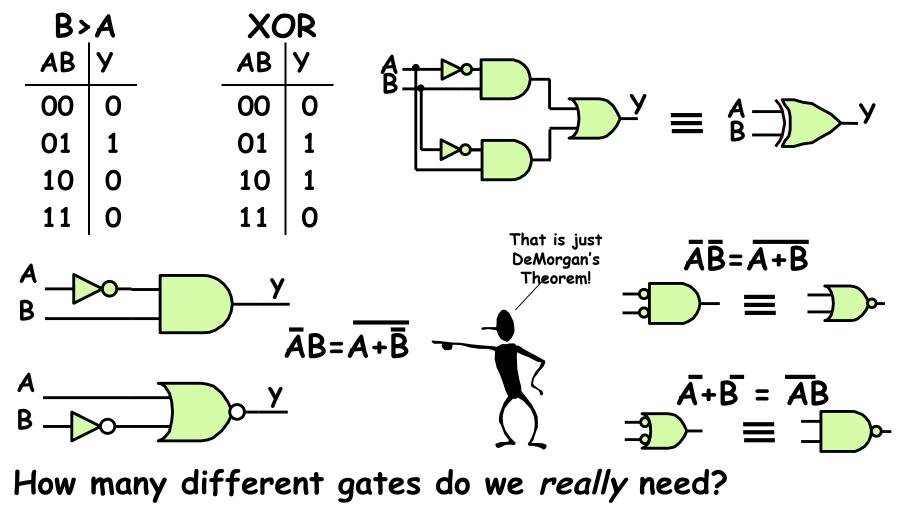

Are we sure we have all the gates we need? Just how many two-input gates are there?

Hmmmm... all of these have 2-inputs (no surprise) ... each with 4 combinations, giving 2<sup>2</sup> output cases

How many ways are there of assigning 4 outputs?  $2^2 = 2^4 = 16$

#### There are only so many gates

#### There are only 16 possible 2-input gates ... some we know already, others are just silly

CMOS gates are inverting; we can always respond positively to positive transitions by cascaded gates. But suppose our logic yielded cheap *positive* functions, while inverters were expensive... Fortunately, we can get by with a few basic gates...

AND, OR, and NOT are sufficient... (cf Boolean Expressions):

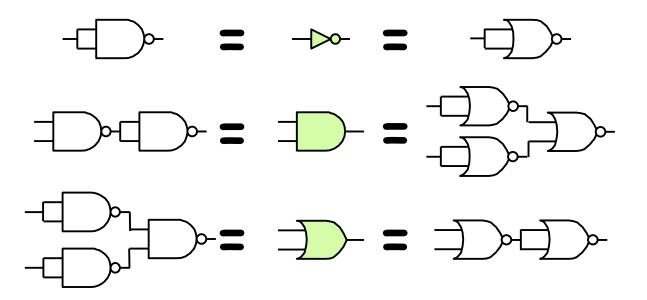

#### One will do!

NANDs and NORs are <u>universal</u>:

Ah!, but what if we want more than 2 inputs?

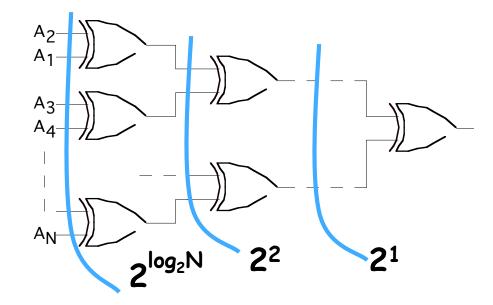

#### I think that I shall never see a circuit lovely as...

N-input TREE has O( <u>log N</u> ) levels...

Signal propagation takes O(  $\log N$  ) gate delays.

Question: Can EVERY N-Input Boolean function be implemented as a tree of 2-input gates?

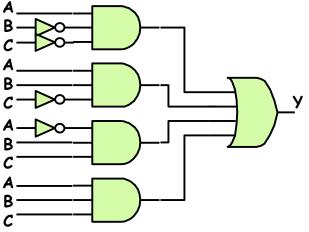

# Here's a Design Approach

Truth Table

| С | В | A | У |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 |

-it's systematic! -it works! -it's easy! -are we done yet??? Write out our functional spec as a truth table

Write down a Boolean expression for every '1' in the output

$$Y = CBA + CBA + CBA + CBA$$

3) Wire up the gates, call it a day, and declare success!

This approach will always give us Boolean expressions in a particular form:

SUM-OF-PRODUCTS

6.111 Fall 2007

## Straightforward Synthesis

We can implement SUM-OF-PRODUCTS with just three levels of logic.

INVERTERS/AND/OR

Propagation delay --No more than "3" gate delays (well, it's actually O(log N) gate delays)