# Virtual Conducting

## 6.111: Introductory Digital Systems Laboratory

Andy Lin and Brandon Yoshimoto

December 11, 2006

#### Abstract

The purpose of this project was to design and implement an interactive music player which allows the user to control the sound of a composition through hand movements. The idea is to emulate the experience of a conductor directing the flow of a musical performance. The design uses a camera to detect hand movements of the user which are then analyzed to adjust musical qualities of tempo, dynamics, and articulation in response to these motions.

The volume of high frequency audio content is controlled by the user's right hand, while the volume of low frequency content is controlled by the user's left hand to allow control over the balance of the playback. The design includes a screen which displays a visualization of the hand movements, including colored squares following the path of the conductor's hands. The screen also displays current tempo, volume, and acceleration magnitudes to provide feedback for the user as he conducts.

## Contents

| Overview                                | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Module Description and Implementation   | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 2.1. Video Component Overview (Brandon) | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 2.3. Color Decision Module              | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 2.4. Video Processor                    | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 2.4.1. Color Detection                  | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 2.4.2. Position Calculator              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 2.4.3. Weighted Average Calculator      | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 2.5. Motion Analyzer                    | .14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 2.5.1. Beat Marker Generator            | 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 2.5.2. Qualities Generator              | 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 2.5.3. Find Distance                    | .17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 2.6. Visualization Generator            | 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 2.7. Signal Tamer                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 2.8. Audio Processing (Andy)            | 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 2.9. Rom FSM                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Testing and Debugging                   | 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 3.1. Video Component                    | 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 3.2. Audio Component                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 5                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 5.1. Low Pass Filter Coefficients       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 5.2. High Pass Filter Coefficients      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 5.3. Verilog Code                       | 42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                         | Module Description and Implementation.         2.1. Video Component Overview (Brandon)         2.2. Camera Input Storage and Retrieval.         2.3. Color Decision Module.         2.4. Video Processor         2.4.1. Color Detection.         2.4.2. Position Calculator.         2.4.3. Weighted Average Calculator.         2.5.4.3. Weighted Average Calculator.         2.5.4.3. Weighted Average Calculator.         2.5.4.3. Weighted Average Calculator.         2.5.5.4. Beat Marker Generator.         2.5.2. Qualities Generator.         2.5.3. Find Distance.         2.6. Visualization Generator.         2.7. Signal Tamer.         2.8. Audio Processing (Andy).         2.9. Rom FSM.         2.10. Beat Generator.         2.11. Metronome Programmer.         2.12. ZBT FSM.         2.13. Beat Period Counter.         2.14. Tempo Modulator.         2.15. Volume and Articulation Modulator.         2.16. HP/LP Filters.         2.17. ROM Writer.         Testing and Debugging.         3.1. Video Component.         3.3. Overall System.         Conclusion.         Appendix |

## List of Figures

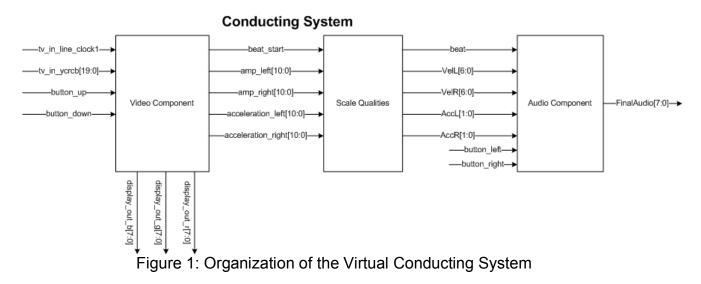

| 1.  | Organization of the Virtual Conducting System                            | 5   |

|-----|--------------------------------------------------------------------------|-----|

| 2.  | The working Virtual Conducting System                                    |     |

| 3.  | A screen capture of the visualization                                    | 6   |

| 4.  | Block diagram overview of Video Component                                | 8   |

| 5.  | Camera Input Storage and Retrieval block diagram                         |     |

| 6.  | Video Processor block diagram                                            | .10 |

| 7.  | Position Calculator block diagram                                        | .12 |

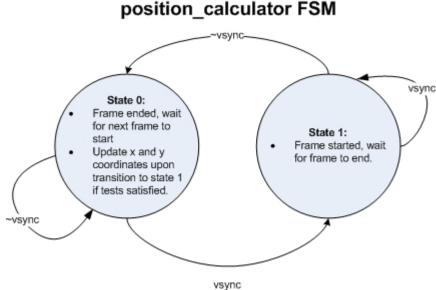

| 8.  | FSM for the Position Calculator module                                   | 13  |

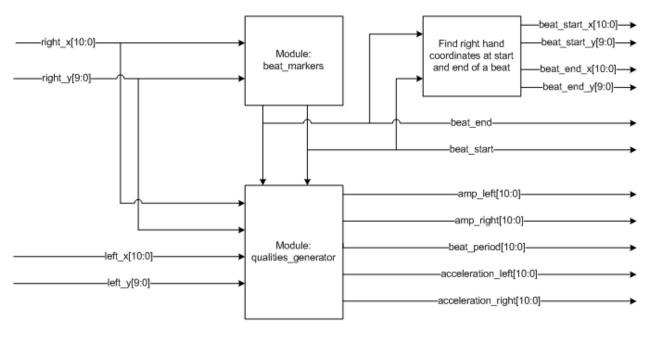

| 9.  | Motion Analyzer block diagram                                            | 14  |

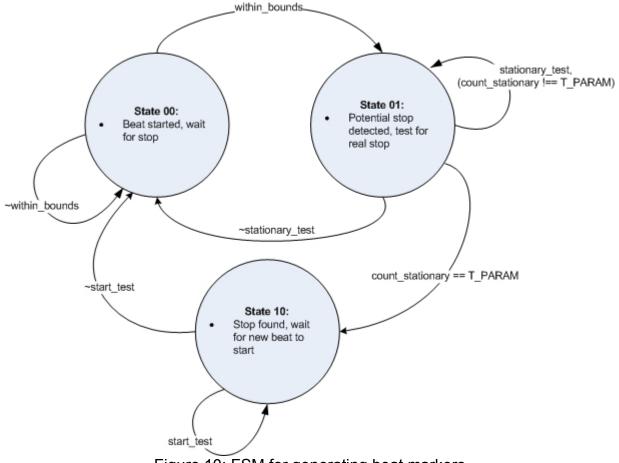

|     | FSM for generating beat markers                                          |     |

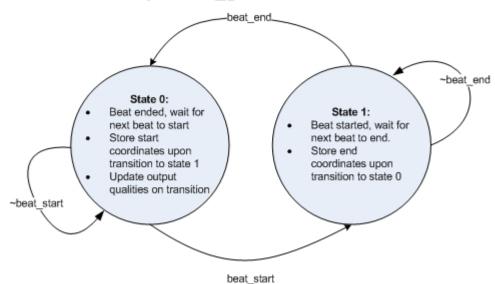

| 11. | FSM for handling the update of beat motion qualities                     | .16 |

| 12. | Description of Screen Components                                         | 18  |

| 13. | The volume fading feature of the signal tamer                            | .20 |

| 14. | The block diagram for the entire audio system                            | 21  |

| 15. | The ROM FSM diagram                                                      | .22 |

|     | The ZBT FSM                                                              |     |

| 17. | Note extend operation                                                    | .24 |

|     | Concept behind the tempo modulator                                       |     |

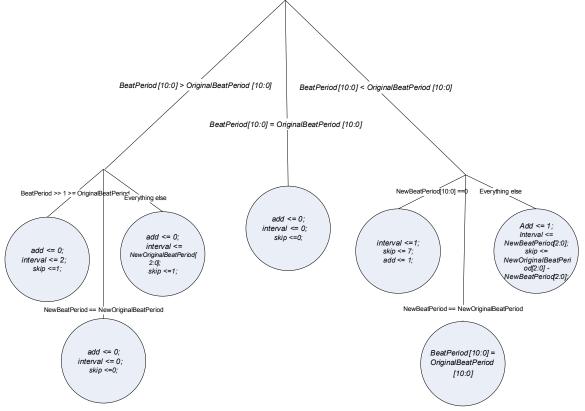

| 19. | The state transition diagram for Division Converter                      | 27  |

| 20. | Different cases for the Division Converter                               | 27  |

| 21. | Block diagram for the Tempo Modulator                                    | .28 |

|     | The concept of articulation modulation                                   |     |

| 23. | Block diagram of the Volume and Articulation Modulator                   | 29  |

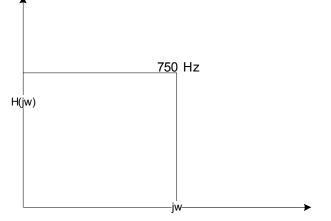

|     | Fourier Transform of high-pass filter with a cut-off frequency of 750 Hz |     |

|     | Fourier Transform of low-pass filter with a cut-off frequency of 750 Hz  |     |

| 26. | ModelSim simulation of Beat Generator Module                             | 34  |

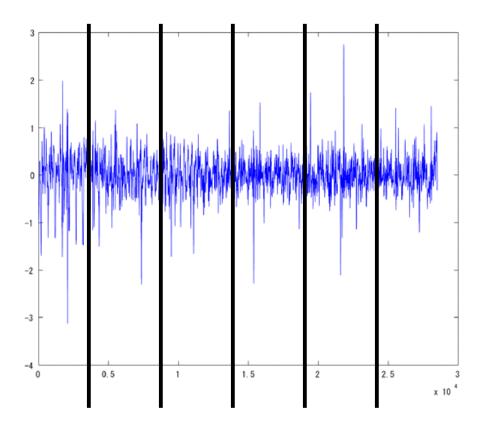

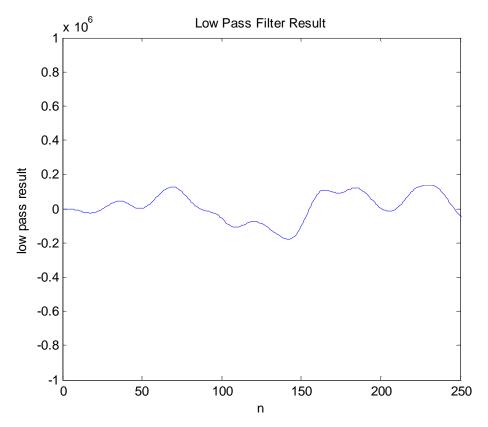

| 27. | Matlab simulation of low-pass filter on a sample of audio                | .35 |

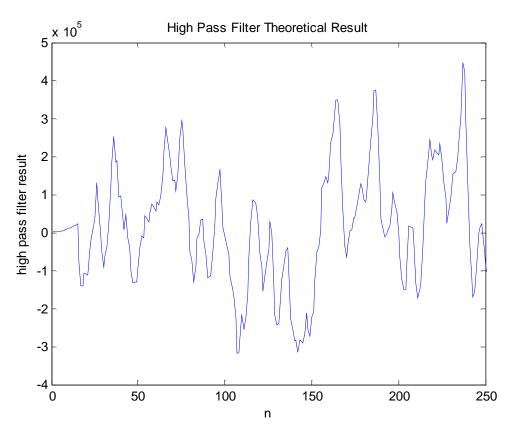

| 28. | Matlab simulation of high-pass filter on a sample of audio               | .36 |

## List of Tables

1. Parameter values used in beat\_markers module for best operation......16

## 1. Overview

The Virtual Conducting system is an interactive music player which allows the user to control the sound of a composition through hand movements. The user stands in front of a camera with two bright blue LEDs, one in each hand. As the user moves his hands, he divides the music into different beats which are matched with the audio to allow control over tempo. Additionally, volume of the high frequency audio is controlled by the size of the right hand's movement, while the volume of low frequencies are controlled by the left hand. The system is divided into two main components: video and audio, as seen in Figure 1.

For video, a camera is used to detect the position of the two bright blue LEDs held by the user. The position of each hand in the 1024x768 VGA coordinate system is determined for each frame of the video display. These coordinates are analyzed over time to determine when a user has started and ended each beat. Beats are determined by the user's right hand only. A beat starts when the current right hand position moves out of a bounded area surrounding the coordinates registered upon a beat end. A beat end is registered if the user's hand remains within certain bounds on the screen for a certain amount of time. This condition essentially examines the speed of the user's motion and detects the end of a beat when the user's motion is too slow. Once the user's motion is divided in to beats, qualities of amplitude, period, and acceleration of each beat are calculated for output to the audio component. While beat period is calculated based on just the right hand, amplitude and acceleration calculations are done for both the left and right hand to control the volume of low and high frequencies respectively.

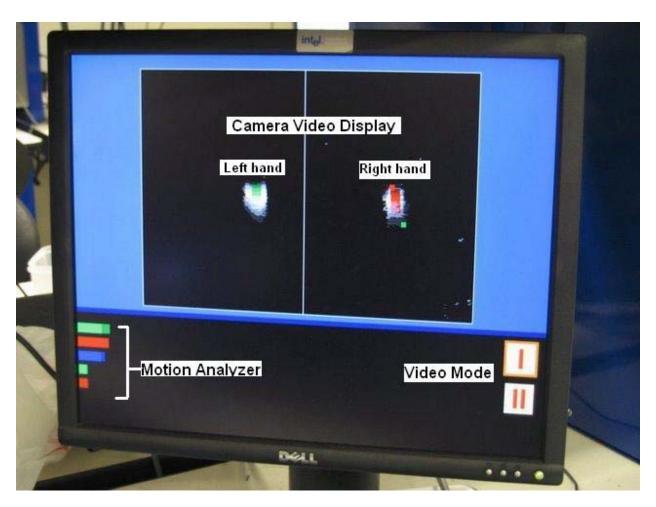

Figure 2: The working Virtual Conducting System

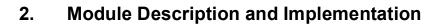

The monitor is used to display the current position of the user's hands, coordinates upon a beat start and end, as well as a motion analyzer display which contains bars that change width in proportion to the magnitude of each motion quality. Figure 3 is a sample image of the visualization. A more detailed description of each part of the display follows in the Module Description section.

Figure 3: A screen capture of the visualization

The audio component uses qualities of the user's motion generated in the video component to adjust the playback of the audio. If a fast beat period is specified by the user through the Video Component, there will be a fast playback; conversely, if a slow

beat period is specified by the user, there will be a slow playback. Moreover, the gesture amplitude of both hands will determine the loudness and articulation of the audio playback. Also, the left hand will control the volume and articulation of the bass, while the right hand will control the treble. Between the video and audio components is a module which translates the values from the video component into valid scaled input values for the audio component.

The audio source is from the flash ROM. The natural beat period of this music can be programmed using the buttons on the FPGA's. In order to program the beat period, button3 must be depressed, while the 8-bit switches are set to their intended positions. In order to program the initial offset, button2 and button3 must be depressed, while the 8-bit switches are set to their are set to their intended positions. To reset the beat period and offset to their default values, button1 is pressed. To reset the audio back to the first sample in the flash ROM, button0 is pressed. The output from the Audio Component is through an AC '97 interface; the audio is 8-bit 24 KHz audio.

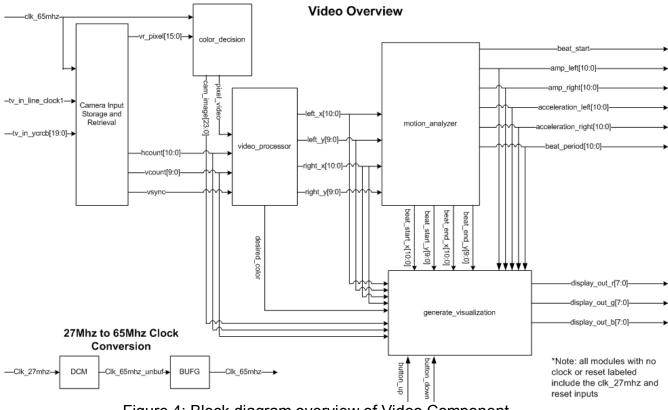

Figure 4: Block diagram overview of Video Component

## 2.1 Video Component Overview (Brandon)

The Video Component of the project consists of five main parts: the camera input storage and retrieval, color\_decision, video\_processor, motion\_analyzer, and generate\_visualization modules, as arranged in Figure 4. On a general level, this portion of the project first analyzes data from the camera input to determine the user's hand positions. Once this information is found in the video\_processor, the motion\_analyzer examines the movement of the hands over time to determine the start and end of a beat. It also determines qualities of the motion for sending to the Audio Component of the project. Finally, the generate\_visualization module takes in information from the other modules to create the video for display on the monitor. Each module is described in further detail below.

## 2.2 Camera Input Storage and Retrieval (Brandon)

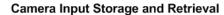

The Camera Input Storage and Retrieval block encompasses the modules which are used for storing the incoming stream of camera data in the ZBT and reading out the contents for use in video processing and visualization. The modules in this component were taken from the sample code on the 6.111 website and modified for this project. The block diagram is outlined in Figure 5.

Figure 5: Camera Input Storage and Retrieval block diagram

Firstly, the ntsc\_decode module uses the *tv\_in\_ycrcb[19:0]* signal to generate the *ycrcb[29:0]* signal. The *ycrcb[29:0]* signal contains a full 30-bit representation of the camera input steam in YCrCb format. The ntsc\_to\_zbt takes this stream of incoming data and stores 16 bits of information for each incoming pixel in the ZBT in the following format: {4'b0, highest 6 Y bits, highest 5 Cr bits, highest 5 Cb bits}. The sample code was modified from four 8-bit pixels per location to handle the storage of two 16-bit blocks of pixel data per location instead. This amount of information is sufficient for color detection and for display of fairly accurate color video. Addresses for storage are generated such that each encodes a pixel's x and y position, allowing for easy lookup of any particular pixel for display on the monitor. Reading and writing from the ZBT is handled by the *ntsc\_we* output from the ntsc\_to\_zbt module.

The xvga module generates the necessary *hcount[10:0]*, *vcount[9:0]*, *vsync*, *hsync*, and *blank* signals for use in the display of 1024x768 video. These signals are used in the vram\_display module which reads raw data from the ZBT and parses it into a stream of 16-bit pixel data in YCrCb format suitable for use in video display. Since two pixels are stored per location, the module holds on to data from the same location for two clock cycles and separates the two pixels' color information to produce the *vr\_pixel[15:0]* output. Another necessary modification of the sample code was to flip the camera image along the y-axis to display the video as if looking into a mirror. This is done in the accessing stage of the pixel data by negating the hcount bits used in

constructing the read address. The flipped image allows for better visual feedback for the user in controlling movement.

All modules used in this storage and retrieval operate on a 65 MHz clock except the ntsc\_decode module, which operates on the clock from the camera, denoted as tv\_in\_line\_clock1. The ntsc\_to\_zbt module handles the interaction between the camera clock and the 65 Mhz clock, ensuring that the correct information from the camera is stored in the ZBT.

## 2.3 Color Decision Module (color\_decision.v) (Brandon)

The color\_decision module determines whether or not a pixel from the camera is of the desired blue color. It also outputs a 24-bit RGB representation of the current pixel.

To determine if a pixel is of the desired blue color, the module does threshold tests on the stored Cb and Cr data. If *Cb[4:0]* is greater than or equal to 18 and *Cr[4:0]* is less than or equal to 16, the *color\_found* signal will go high. Otherwise, the signal will be low, indicating the blue color is not detected. This threshold was tested to be the best for filtering out dark blues and optimizing detection of the bright blue lights held by the user. The *color\_found* signal is tied to the output *pixel\_video* for use in the video\_processing module to display detected blue areas on the monitor.

Additionally, the color\_decision module uses the YCrCb2RGB module provided by Xilinx to convert from the YCrCb color space to the RGB color space. Since the VGA display requires RGB content, this component was necessary for displaying color video. This information is encoded in the *cam\_image* output as {8 bits of R, 8 bits of G, 8 bits of B}.

## video\_processor

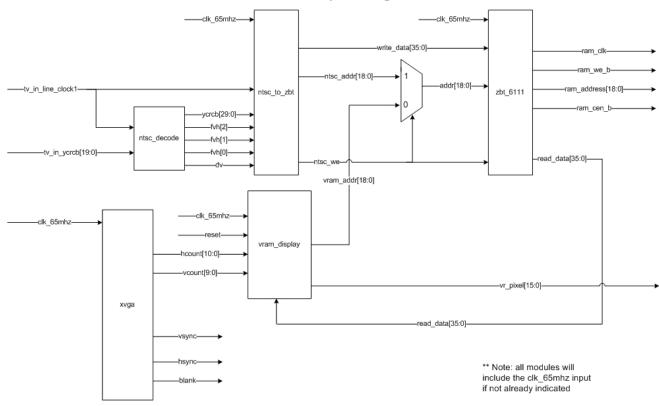

Figure 6: Video Processor block diagram

## 2.4 Video Processor Module (video\_processor.v) (Brandon)

The video\_processor module takes in the *pixel\_video* input from the color\_decision module and outputs the average coordinates of each hand as 11-bit x and 10-bit y coordinates. The outputs are defined as *left\_x[10:0]* for the x-position of the left hand and *left\_y[9:0]* for the y-position of the left hand. This same notation is used for the right hand. Calculation of these positions is divided into two modules: color\_detection and position\_calculator. The organization of this module is described in Figure 6.

## 2.4.1 Color Detection Module (color\_detection.v) (Brandon)

The color\_detection module determines if a pixel should be used in the calculation of a hand's position. This module has two main functions: one is to decide which half of the screen the detected pixel is in, and the other is to reduce the noise of random pixels detected by the color\_decision module that should not be included as part of the hand.

The error reduction function is implemented using shift registers to compare the *pixel\_video* values across three consecutive samples. The temporary wire *desired\_color\_temp* will be high only if *pixel\_video* is high for two consecutive pixels. This method detects the user's blue lights quite well while reducing the amount of noisy pixels which could affect average position calculations.

Additionally, *left\_side* and *right\_side* signals are used to determine if the current pixel is inside the left or right half of the region of display, divided along its center. The display region includes only the camera display window as defined in Figure 12. Combining these two tests, the *left\_en* output is high only if both *left\_side* and *desired\_color\_temp* are high, corresponding to a pixel which withstands the error correction test and is in the left hand plane of the screen. The *right\_en* output is generated in the same way, but uses the *right\_side* signal. The *desired\_color* output is tied to the *desired\_color\_temp* signal for use in displaying the detected pixels in the visualization module.

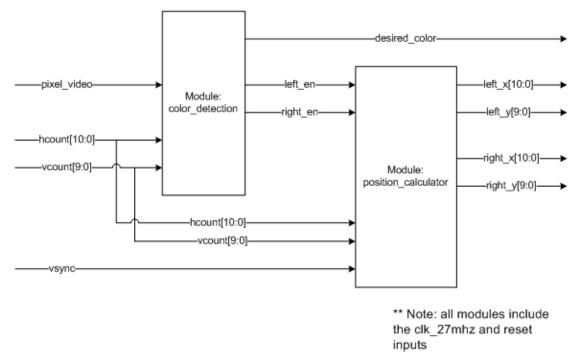

## 2.4.2 Position Calculator (position\_calculator.v) (Brandon)

The position\_calculator module uses the *left\_en* and *right\_en* signals from the color\_detection module to calculate of the weighted average hand positions. On a basic level, the module uses four weighted\_average modules to compute the average x and y positions for each hand, as seen in Figure 7. However, the position\_calculator first applies some tests to the averages calculated by the weighted\_average modules before updating the positions for output.

#### position\_calculator

Figure 7: Position Calculator block diagram

The *left\_in\_left\_side*, and *right\_in\_right\_side* signals are used to prevent the left and right hand positions from going out of their respective halves of the camera display. The *left\_in\_left\_side* signal is high when the calculated weighted average coordinates for the left hand are within the appropriate bounds for the left half. The *right\_side* signal is similarly high when the right hand is within the appropriate bounds for the right side.

A second test checks if the new coordinates are sufficiently close to the currently stored coordinates. This test prevents large jumps in the coordinate positions to provide smoother motion. If the new coordinates are within a 150 x 150 pixel square centered at the current left hand coordinates, *no\_left\_jump* will be high. The same applies for *no\_right\_jump* on the right hand.

The third test detects if the current pixels are outside of the camera video frame. The coordinates upon starting the system are all initialized to 0, so both *outside\_frame\_left* and *outside\_frame\_right* will start off high.

Using these three test signals, the coordinates for the registers holding the output coordinates for the left hand will only update if the new coordinates are in the left hand plane and there is either no large jump in position or the current coordinates are outside of the frame. This is summarized as the condition: (left\_in\_left\_side && (no\_left\_jump ||

outside\_frame\_left)). The same applies to the equivalent right hand signals for updating the right hand coordinates.

The potential coordinate update occurs only when a new frame starts at the rising edge of the *vsync* signal. Figure 8 shows the two-state FSM used for coordinating the update of coordinates.

Figure 8: FSM for the Position Calculator module

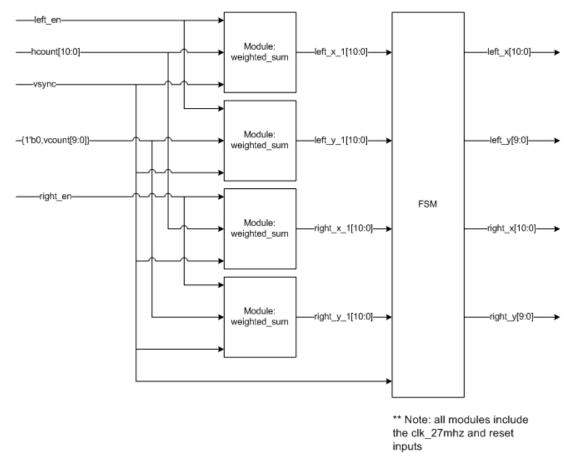

## 2.4.3 Weighted Average Calculator (weighted\_sum.v) (Brandon)

The weighted\_average module takes signals *enable* and *count[10:0]* as inputs to calculate the average of the count values received when *enable* is high. The *sum[27:0]* registers are used to hold a running sum of the count values, only adding new value if *enable* is high. This running sum calculation begins as soon as *vsync* goes high. *Pixel\_count[17:0]* keeps track of how many times *enable* goes high.

To calculate the average, *sum/pixel\_count* is calculated using the Xilinx Pipelined Divider v3.0. The lower 11 bits of the divider result are tied to the output *avg*.

Since divider module requires 28 clock cycles to compute, the module is enabled as soon as the current *vcount* is beyond the lower border of the camera image, defined as when *vcount* > BOTTOM\_BORDER. The clear is done through changing the *sclr* input to the divider. This timing provides more than enough clocks at 27 MHz to complete the divide calculation before a new frame starts.

## motion\_analyzer

\*\* Note: all modules include the clk\_27mhz and reset inputs

Figure 9: Motion Analyzer block diagram

## 2.5 Motion Analyzer Module (motion\_analyzer.v) (Brandon)

The motion\_analyzer module generates the qualities of beat amplitude, period, and acceleration by analyzing the movement of each hand's x and y hand coordinates over time. The computations are divided into two submodules: the beat\_markers and qualities\_generator modules, as seen in Figure 9.

The beat\_markers module decides when a beat starts and end. The qualities\_generator uses this beat marker information to determine the amplitude, period, and acceleration calculations for each beat. More detailed descriptions of these modules are in their respective sections that follow.

The other outputs of the motion\_analyzer module are the x and y coordinates of each hand at the start and end of a beat. These coordinates are used for displaying the beat start and end points in the generate\_visualization module. The beat start coordinates are stored in registers that are updated whenever *beat\_start* goes high. Similarly, the end coordinates are held in registers updated when *beat\_end* goes high.

## 2.5.1 Beat Marker Generator (beat\_markers.v) (Brandon)

The beat\_markers module determines the start and end of a beat based on the movement of the right hand over time. Since beats are only formed by the motion of the right hand, *right\_x[10:0]* and *right\_y[9:0]* are the only inputs to this module. There are two outputs: *beat\_start*, and *beat\_end*. *Beat\_start* will go high for one clock cycle upon detection of the start of a beat, while *beat\_end* will go high for one clock cycle at the end of a beat.

## beat\_markers FSM

Figure 10: FSM for generating beat markers

Management of the start and end states of a beat is handled by a three state FSM diagrammed in Figure 10. State 00 is when a beat already started and the system is waiting for a stop signal. The stop signal is called *within\_bounds*. This signal goes high when the current pixel coordinates are within a centered box of 2\*TOLERANCE\_X and 2\*TOLERANCE\_Y of the previous pixel. Assertion high indicates a potential beat stop and changes the FSM to state 01.

In state 01, the module tests if the potential beat stop should be registered as an actual stop. Upon transition to this state, the FSM stored the x and y coordinates of the right hand in registers for use in the next test called *stationary\_test*. *Stationary\_test* goes high if the current frame's coordinates remain for several clocks within a centered box of 2\*TOLERANCE\_END\_X and 2\*TOLERANCE\_END\_Y of the coordinates stored upon transition. The length in time that this wait test must remain active is a parameter which affects sensitivity towards how long the hand must remain within appropriate bounds to be registered as a beat end. In this implementation, *stationary\_test* must be valid for 1,048,575 clock cycles at 27 MHz to move to state 10 and detect a beat end. This corresponds to a wait of about 0.039 seconds. If the coordinates go outside of this bound within that time frame, the FSM will return to state 00 to wait for the next potential

beat end. If the test holds, the *beat\_end* output will go high for one clock cycle upon transition to state 10.

In state 10, a stop has already been detected, so the FSM will remain in this state until a new beat is detected. A new beat is detected if the *start\_test* signal goes low. *Start\_test* goes low when the current coordinates are outside an area bounded by the centered box of 2\*TOLERANCE\_START\_X by 2\*TOLERANCE\_START\_Y around the stored coordinates upon leaving state 01. The coordinates leaving this bound means the hand has moved enough to be considered the start of a new beat. Upon *start\_test*, the FSM will transition to state 00 and the *beat\_start* output will go high for one clock cycle.

The parameters in this module were tested and set for the user to have best control over generating beats while conducting. The values used in the final implementation are listed in Table 1.

| Parameter:        | Value: |

|-------------------|--------|

| TOLERANCE_X       | 2      |

| TOLERANCE_Y       | 2      |

| TOLERANCE_END_X   | 5      |

| TOLERANCE_END_Y   | 5      |

| TOLERANCE_START_X | 25     |

| TOLERANCE_START_Y | 25     |

| Table 1: Parameter values used in beat markers module for best operation |

|--------------------------------------------------------------------------|

|--------------------------------------------------------------------------|

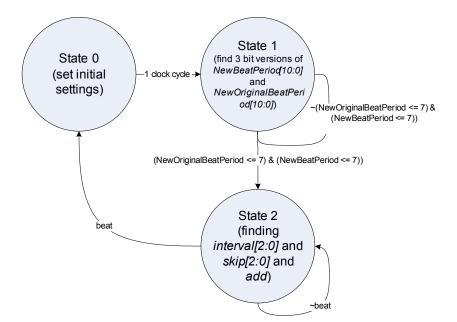

## qualities\_generator FSM

Figure 11: FSM for handling the update of beat motion qualities

#### 2.5.2 Qualities Generator Module (qualities\_generator.v) (Brandon)

The qualities\_generator module uses the *beat\_start* and *beat\_end* signals determined by the beat\_markers module to calculate amplitude, time duration, and acceleration values of the motion every beat. A two-state FSM is used in this module to coordinate the update of these qualities with the video display as seen in Figure 11.

In state 0, a beat has ended and the system is waiting for a new beat to start, corresponding to when *beat\_start* goes high. Upon receiving a beat start signal, FSM transitions to state 1 and stores the start coordinates of each hand in registers. In state 1, the system is now waiting for a beat to end. When *beat\_end* goes high, the FSM transitions back to state 0 and stores the coordinates upon transition into registers. These registers are used to calculate the distance in pixels between the start and end of a beat. This calculation is done for each hand. The left hand distance is used for updating the *amp\_left[10:0]* output, while the right hand distance is used for updating the *amp\_right[10:0]* output. Distance calculation is done in the find\_distance module described in the section that follows.

For beat period and acceleration calculation, a signal called *count[18:0]* is used to divide the clock into roughly 0.02 second divisions, or 2^19 clock cycles at 27 Mhz. Every time this time period passes, the *time\_count[10:0]* registers will increment by one to count the time spent in state 1 waiting for a beat to end.

For acceleration calculation, shift registers are used to compute the difference of distances between three successive coordinate samples. These three coordinate points are roughly 0.02 seconds apart from each other and are stored only when the *time\_count[10:0]* signal is less than or equal to 6. This means that only coordinates at the beginning of a new beat are used for calculations of a single beat's acceleration. The stored values in the shift registers are used to find the difference in distances for each hand using a total of four find\_distance modules (two for each hand). The results are rough acceleration approximations for each hand.

Each of these calculated qualities are only updated for output upon the start of a new beat, as detected in the FSM when *beat\_start* goes high while in state 0.

### 2.5.3 Find Distance Module (find\_distance.v) (Brandon)

The find\_distance module takes in two coordinates and outputs the distance in pixels between the two points. This calculation is done by first calculating the difference in x coordinates and y coordinates between the two points, ensuring that the difference is positive. Next, each difference is multiplied by itself to get the squared values. The two results are added together to form the *sum\_of\_squares[19:0]* wire. The Xilinx square root Core module is used to calculate the square root of this value to produce the *distance[10:0]* output.

Figure 12: Description of Screen Components

## 2.6 Generate Visualization Module (generate\_visualization.v) (Brandon)

The generate\_visualization module takes in number of signals from the color\_decision, video\_processor, and motion\_analyzer modules to output three signals of R, G, and B data for display on the monitor. Figure 12 is a sample display generated by this module.

The *cam\_image[23:0]* signal from the color\_decision module is used to display the raw camera input video in RGB format. The *desired\_color* input from the video\_processor module is used to display a pixel as white if high and black if low. Switching between these two display modes for the camera image area is handled by an FSM which keeps track of the current display mode. Mode 0 is the default that corresponds to the black and white *desired\_color* display. Mode 1 is entered after pressing the down button on the lab kit and corresponds to color display of the camera input.

Additionally, the *left\_x[10:0]*, *left\_y[9:0]*, *right\_x[10:0]*, and *right\_y[9:0]* signals are used as inputs to centered\_block modules to display squares at each hand's current coordinates. The centered\_block module is a sprite which generates a color block on screen with its center at the input coordinates. For example, the block following the left hand will have input coordinates at *left\_x[10:0]* and *left\_y[9:0]*, with width and height of

20 pixels. The right hand has similar structure but with  $right_x[10:0]$  and  $right_y[9:0]$  as inputs. For color, the left hand block is green, while the right hand block is red to differentiate between the two. To add to the visualization, two sprites of darker hue for each hand follow the path of the hand blocks at positions delayed by around 0.2 second intervals. This is accomplished using the *count*[18:0] registers to count clock cycles at 27 Mhz such that each time *count* == 0 the current hand coordinates are stored in registers. These blocks are displayed on screen to add a slight trailing effect to the hand motion.

Another set of sprites is used to display the coordinates at which a beat begins and ends. Since beats are dictated by just the right hand, only two sprites are needed: one to remain at the start coordinates, and the other to remain at the end coordinates. These blocks are smaller in size, with a height and width of 10 pixels. The block at the start of a beat is green, while the block at the end of a beat is red.

Since all the above display signals are within the same area on screen, logic is used to determine which pixel data should be displayed over others. This layering is important to prevent odd colors from arising when adding together two different pixel streams. The order of precedence as described by the logic is as follows, from the uppermost to lower layer: hand position blocks, hand trailing blocks, beat start and beat end blocks, then finally the *cam\_image[23:0]* or *desired\_color* display depending on the current mode.

Other features of the display include the 1-pixel wide white border around the camera video, as well as the white line dividing the two halves of the screen. Around the thin white border is a blue border to fill the space of the upper half of the screen. These colored areas are generated using logic to divide up the screen into parts using the *hcount[10:0]* and *vcount[9:0]* inputs.

Below the camera display are motion analyzer bars which indicate relative amplitude, beat period, and acceleration values from the motion\_analyzer over time. There are two of each the amplitude and acceleration values (one for each hand) and one beat period value, for a total of five bars on the screen.

The magnitude of each motion quality scales with the width of its respective bar on screen. These sprites were generated using the analyzer\_bar module which takes the bar width and upper left hand corner coordinates as parameters. The positioning of the five bars are, in order from top to bottom of the screen: left hand amplitude, right hand amplitude, beat period, left hand acceleration, and right hand acceleration. All qualities for the right hand are colored red to match the block following the right hand, while qualities for the left hand are colored green to match the block following the left hand. This display allows the user to clearly see how his motions are affecting the playback of the music.

The button display on the bottom right of the screen is used to keep track of what display to show in the camera video frame. The upper button with the "I" label is the default mode for display of detected blue areas. The lower button with the "II" label is the mode for viewing a dimmed version of the camera input video.

### 2.7 Signal Tamer (Andy)

The Signal Tamer module is placed between the Video and Audio Processing parts of the system. The basic function of this module is to take the raw inputs of

velocity and acceleration, and to scale them and/or bit-shift them to make them compatible and within the range needed for the Audio Processing Module. Moreover, the module also "tames" the signals, meaning it low-pass filters the acceleration signals and allows for gradual volume transitions.

The low-pass filter for the acceleration signals is merely an average of the acceleration values of the last two beats. To achieve a gradual volume transition between two beats, interpolation is required. An audio beat is divided into 32 sections, each of which has a different volume value. Division 0 will have the volume of the previous beat and Division's 15-31 will have the volume of the new beat. There will be a linear transition between divisions 0 and 15. Figure 13 illustrates this point. See Verilog code in the Appendix for details.

Figure 13: The volume fading feature of the signal tamer steps the volume between the previous and new volumes by using linear interpolation of the first 16 divisions of the new beat.

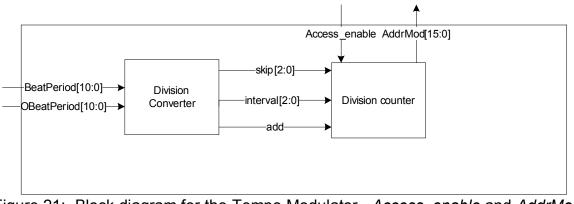

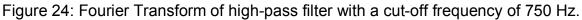

## 2.8 Audio Processing (Andy)

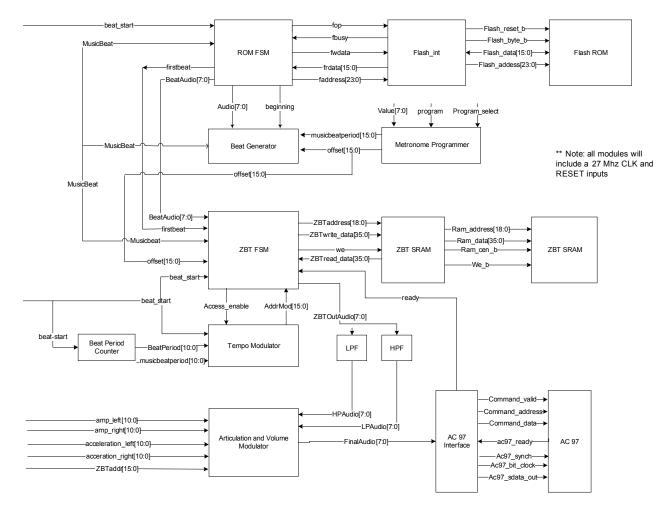

The Audio Processing Unit of the Virtual Conducting Project interprets the signals, *acceleration\_left\_fixed[1:0], acceleration\_right\_fixed[1:0], VelL\_fixed[6:0]*, and *VelR\_fixed[6:0]* to produce audio, stored in the flash ROM, to correspond to these characteristics. The Audio Processing Component takes audio stored from the flash ROM, and outputs it one beat at a time. The audio is also modulated in tempo, volume, and articulation.

The data flow begins at the ROM FSM. Interacting with the ZBT FSM and Beat Generator, the ROM FSM reads audio data from the flash ROM at 4 clock cycles per address (6.75 MHz). The ROM FSM will read data and pass it onto the ZBT FSM one beat at a time with help from Beat Generator. The data read in from the ROM FSM will be written into the ZBT SRAM at 4 clock cycles per address.

This is performed by reading in data from flash ROM and storing it into the ZBT RAM until a *musicbeat* signal is declared, demarking the end of a beat. After the *musicbeat* signal is declared, the ZBT FSM will allow the same beat of music stored in

the RAM to be read out at 24 KHz to the AC '97 interface. Since the writing in to ZBT RAM is done at 6.75 MHz, the pause in between beats is barely noticeable by human ear.

The ZBT RAM allows for the writing and reading of different addresses in the ZBT RAM. During the writing cycle, it gives access only to the ROM FSM to write data into the RAM. After the write cycle, the read cycle begins, and the ZBT RAM with help from the Tempo Modulator reads data from the ZBT RAM.

The Tempo Modulator takes in the original beat period (from the music), and the user specified beat period and helps change the audio output speed. The main output from the Tempo Modulator will be addrmod[15:0] which will interact with the ZBT FSM to change the address accessed from the ZBT SRAM at the right times to change the tempo. If the user specified tempo is greater than the original tempo, addresses are added, if the specified tempo is slower, then addresses are subtracted.

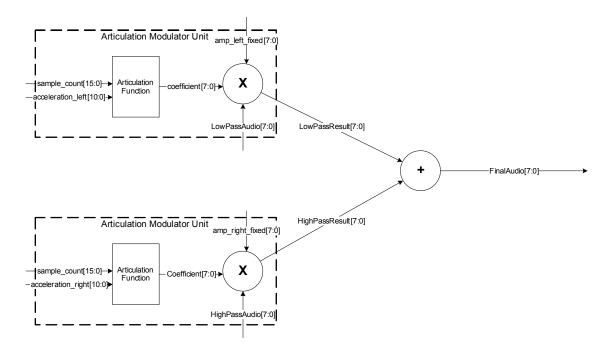

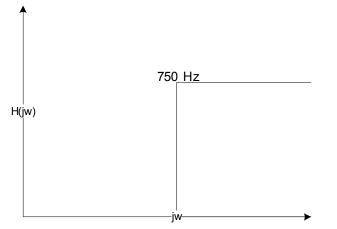

The output from the ZBT FSM will be 24 KHz 8-bit PCM data. This audio data is fed to low pass and high pass filters. The outputs from the filters are the inputs for the Volume and Articulation Modulator.

Figure 14: The block diagram for the entire audio system. User inputs are *Value*[7:0], *program*, and *program\_select* in order to reprogram *musicbeatperiod*[15:0] and *offset*[15:0]

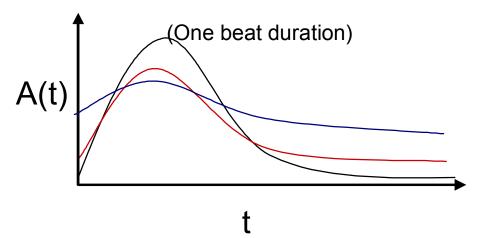

The Volume and Articulation Modulator simply multiplies the existing audio by a preset function. If the articulation is weak (the acceleration is weak), the function to be multiplied is simply a constant throughout the beat. However, if the articulation is strong, the function is low initially, quickly climbs to a maximum, and slowly decays. The output from the Volume and Articulation Modulator is finally fed into the AC '97 interface for audio output. See Figure 14 for the overall Audio Component block diagram.

### 2.9 ROM FSM (Andy)

The ROM FSM reads from the flash ROM and interacts with the ZBT FSM, and beat generator to allow output of one musical beat at one time. Initially starting at zero, an address counter increments in order to read from ROM sequentially. In this implementation, it takes four clock cycles to read from ROM. The first clock cycle declares a write operation. It was chosen to wait three more clock cycles to insure that the FPGA has correctly read one word of data from the flash RAM.

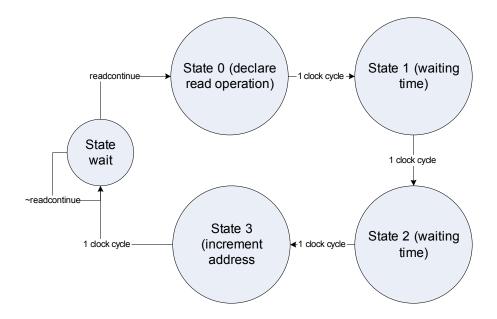

The ROM FSM has 4 states. The first state declares a read operation; the next two states are dedicated to allow for a delay before actually reading data. The last state reads the data from the flash, increments the address to read from, and returns the state to *state 0*. If the address to read from exceeds the number of addresses stored in ROM, the address will loop to 0. This cycle will not occur unless if *readcontinue* is true. *Readcontinue* turns high when *beat* is declared, and remains high until *musicbeat* is declared. Since *beat* represents when the user wants another beat to be played, and *musicbeat* declares the end of this beat, this allows audio data to be read out one beat at a time. See Figure 15 for details.

Moreover, the ROM FSM is responsible for letting the rest of the system know when the first beat occurs. The first beat contains a different beat period, and a different note extension technique, and is a signal other modules must use. Refer to the Appendix for details.

Figure 15: The ROM FSM has 4 real states, and one "wait state." The FSM is used to read data from the ROM at 6.75 MHz (4 clock cycles per address). *Readcontinue* turns high when *beat* is declared, and remains high until *musicbeat* is declared.

## 2.10 Beat Generator (Andy)

The Beat Generator module generates *musicbeat* signals that indicate the division between beats. This module uses a set beat period – given by the user- in order to generate this signal. The *sample\_count[15:0]* register counts the number of times that the ROM FSM accesses memory. The number of times a different address in flash memory is accessed will be the unit of measure for the Beat Generator. When *sample\_count[15:0]* reaches the beat period of the audio data, *musicbeat* will go high and *sample\_count[15:0]* will reset to zero.

The Beat Generator interacts with the Metronome Programmer, which stores the value of *musicbeatperiod*[15:0] and *offset*[15:0]. *Musicbeatperiod*[15:0] specifies the regular beat period in flash ROM address accesses, and *offset*[15:0] specifies the offset to initially assign *sample\_count*[15:0]. The use of Metronome Programmer allows *musicbeatperiod*[15:0] and *offset*[15:0] to be reprogrammed by the user if desired.

## 2.11 Metronome Programmer (Andy)

Metronome Programmer is a small reprogrammable ROM that stores the constant values for *musicbeatperiod*[15:0] and *offset*[15:0]. *Musicbeatperiod*[15:0] represents the time period between musical beats in the audio that is loaded in the ROM. This time period will vary from song to song. By keeping *program* high, selecting which value to program with *program\_select*, and setting the FPGA buttons to the intended value, *musicbeatperiod*[15:0] and *offset*[15:0] can be reprogrammed. Note that since the FPGA only has 8 buttons, the input will be an 8-bit number, but the needed value is a 16-bit number. The input is multiplied by 100 to solve this problem.

## 2.12 ZBT FSM (Andy)

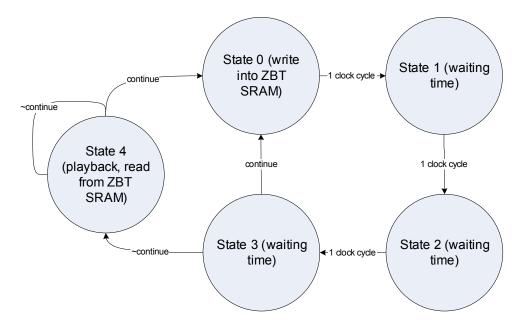

The ZBT FSM interacts with the ROM FSM, the ZBT SRAM, and the Tempo Modulator. Inputs for the ZBT FSM are *musicbeat*, *first*, *beataudio[15:0]*, *offset[15:0]*, *beat\_start*, *addr\_mod[15:0]*, *ZBTreaddata[35:0]*, and *ready*. Outputs for this module are *access\_enable*, *ZBTaddress[18:0]*, *ZBTwrite\_data[35:0]*, we, and *ZBTOutAudio[7:0]*. The ZBT FSM interacts closely with the ROM FSM; when the ROM FSM is reading out data, the ZBT FSM fetches the data from *beataudio[15:0]* and writes it into the ZBT SRAM simultaneously. Like the ROM FSM, the ZBT FSM writes a sample once every 4 clock cycles. When the ROM FSM is not reading out data, the ZBT FSM reads out the data that was just stored at 24 KHz. See Figure 16 for the state transition diagram.