# **GPS Tracking System**

Design Report Final Project 6.111 / Massachusetts Institute of Technology December 12, 2006

Alexander Valys

## Abstract

A mobile GPS data logger and visualization system was implemented on a Digilent Nexys board, and the 6.111 labkit. Position data is read from a third-party GPS receiver, stored on a third-party Flash ROM, and then rendered in 2D and 3D on a VGA display through a generalized coordinate transformation and rendering system.

Most of the implementation goals were achieved. However, due to unexpected difficulties in a variety of areas, notably debugging the 3D transformation module, the final user interface is not as polished as was originally intended.

# Contents

| 1                    | 1 Overview                                                                                                                                                                                                                                                                                                                                                   | 5                                                                                                                                                                                                                                                                               |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                      | 1.0.1 Defaults                                                                                                                                                                                                                                                                                                                                               | 55                                                                                                                                                                                                                                                                              |

|                      | 1.1 Mobile Data Logger                                                                                                                                                                                                                                                                                                                                       | 55                                                                                                                                                                                                                                                                              |

|                      | 1.1.1 Connections an                                                                                                                                                                                                                                                                                                                                         | d Power                                                                                                                                                                                                                                                                         |

|                      | 1.2 Visualization System                                                                                                                                                                                                                                                                                                                                     | 6                                                                                                                                                                                                                                                                               |

| <b>2</b>             | 2 Mobile Data Logger Imp                                                                                                                                                                                                                                                                                                                                     | plementation 7                                                                                                                                                                                                                                                                  |

|                      |                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                 |

|                      | 2.1.1 RS232 Protoco                                                                                                                                                                                                                                                                                                                                          | 1                                                                                                                                                                                                                                                                               |

|                      |                                                                                                                                                                                                                                                                                                                                                              | 1 Overview                                                                                                                                                                                                                                                                      |

|                      | 2.1.3 FSM                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                 |

|                      | 2.2 SiRF Message Parser                                                                                                                                                                                                                                                                                                                                      | Module                                                                                                                                                                                                                                                                          |

|                      |                                                                                                                                                                                                                                                                                                                                                              | Format                                                                                                                                                                                                                                                                          |

|                      |                                                                                                                                                                                                                                                                                                                                                              | 10 Overview                                                                                                                                                                                                                                                                     |

|                      |                                                                                                                                                                                                                                                                                                                                                              | 10                                                                                                                                                                                                                                                                              |

|                      |                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                 |

|                      |                                                                                                                                                                                                                                                                                                                                                              | 12                                                                                                                                                                                                                                                                              |

|                      |                                                                                                                                                                                                                                                                                                                                                              | 12                                                                                                                                                                                                                                                                              |

|                      | 2.4.1 Serial Flash Pr                                                                                                                                                                                                                                                                                                                                        | otocol                                                                                                                                                                                                                                                                          |

|                      |                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                 |

| 3                    | 3 Visualization System Im                                                                                                                                                                                                                                                                                                                                    | plementation Overview 15                                                                                                                                                                                                                                                        |

|                      |                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                 |

| 4                    | 4 ROM Reader / Log Dec                                                                                                                                                                                                                                                                                                                                       | oder 15                                                                                                                                                                                                                                                                         |

| 4                    | /8                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                 |

| 4                    | 4.1 Clock Speeds                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                 |

| 4                    | <ul><li>4.1 Clock Speeds</li><li>4.2 Determining the end of</li></ul>                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                 |

|                      | <ul><li>4.1 Clock Speeds</li><li>4.2 Determining the end of</li><li>4.3 Resetting</li></ul>                                                                                                                                                                                                                                                                  | f the log $\dots \dots \dots$                                                                                                                                                   |

| <b>4</b><br><b>5</b> | <ul> <li>4.1 Clock Speeds</li> <li>4.2 Determining the end of 4.3 Resetting</li> <li>5 Video RAM</li> </ul>                                                                                                                                                                                                                                                  | f the log                                                                                                                                                                                                                                                                       |

|                      | <ul> <li>4.1 Clock Speeds</li> <li>4.2 Determining the end of 4.3 Resetting</li> <li>5 Video RAM 5.1 VRAM Module</li> </ul>                                                                                                                                                                                                                                  | f the log                                                                                                                                                                                                                                                                       |

|                      | <ul> <li>4.1 Clock Speeds</li> <li>4.2 Determining the end of 4.3 Resetting</li> <li>5 Video RAM</li> <li>5.1 VRAM Module</li> <li>5.2 VGA Module</li> </ul>                                                                                                                                                                                                 | f the log                                                                                                                                                                                                                                                                       |

|                      | <ul> <li>4.1 Clock Speeds</li> <li>4.2 Determining the end of 4.3 Resetting</li> <li>5 Video RAM 5.1 VRAM Module 5.2 VGA Module</li> <li>6 Rendering Pipeline</li> </ul>                                                                                                                                                                                     | f the log                                                                                                                                                                                                                                                                       |

| 5                    | <ul> <li>4.1 Clock Speeds</li> <li>4.2 Determining the end of 4.3 Resetting</li> <li>5 Video RAM</li> <li>5.1 VRAM Module</li> <li>5.2 VGA Module</li> <li>6 Rendering Pipeline</li> <li>6.1 Commands and Module</li> </ul>                                                                                                                                  | $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                            |

| 5                    | <ul> <li>4.1 Clock Speeds</li> <li>4.2 Determining the end of 4.3 Resetting</li> <li>5 Video RAM 5.1 VRAM Module</li> <li>5.2 VGA Module</li> <li>6 Rendering Pipeline 6.1 Commands and Modu 6.2 Command Widths and</li></ul>                                                                                                                                | f the log       16         f the log       17         i       17         i       17         i       17         i       17         i       17         i       18         i       19         i       19         i       19         i       20         i       21                  |

| 5                    | <ul> <li>4.1 Clock Speeds</li> <li>4.2 Determining the end of 4.3 Resetting</li> <li>5 Video RAM 5.1 VRAM Module</li> <li>5.2 VGA Module</li> <li>6 Rendering Pipeline 6.1 Commands and Modu 6.2 Command Widths and 6.3 The Advance Signal</li> </ul>                                                                                                        | f the log       16         f the log       17         i       17         i       17         i       18         i       18         i       19         les       20         l Serialized Commands       21         i       21                                                     |

| 5                    | <ul> <li>4.1 Clock Speeds</li> <li>4.2 Determining the end of 4.3 Resetting</li> <li>5 Video RAM 5.1 VRAM Module</li> <li>5.2 VGA Module</li> <li>6 Rendering Pipeline 6.1 Commands and Modu 6.2 Command Widths and 6.3 The Advance Signal 6.4 An Example Comman</li> </ul>                                                                                  | f the log       16         f the log       17         f the log       17         17       17         18       18         19       19         les       20         l Serialized Commands       21         1       21         d Sequence       21                                 |

| 5                    | <ul> <li>4.1 Clock Speeds</li> <li>4.2 Determining the end of 4.3 Resetting</li> <li>5 Video RAM 5.1 VRAM Module</li> <li>5.2 VGA Module</li> <li>6 Rendering Pipeline 6.1 Commands and Modu 6.2 Command Widths and 6.3 The Advance Signal 6.4 An Example Comman</li> </ul>                                                                                  | f the log       16         f the log       17         i       17         i       17         i       18         i       18         i       19         les       20         l Serialized Commands       21         i       21                                                     |

| 5                    | <ul> <li>4.1 Clock Speeds</li> <li>4.2 Determining the end of 4.3 Resetting</li> <li>5 Video RAM 5.1 VRAM Module</li> <li>5 Video RAM 6.1 VRAM Module</li> <li>6 Rendering Pipeline 6.1 Commands and Modu 6.2 Command Widths and 6.3 The Advance Signal 6.4 An Example Comman 6.5 Extensions and Generar 7 Rendering Pipeline Mode</li> </ul>                | f the log       16         f the log       17         17       17         18       18         19       19         les       20         l Serialized Commands       21                                                                                                           |

| 5                    | <ul> <li>4.1 Clock Speeds</li> <li>4.2 Determining the end of 4.3 Resetting</li> <li>5 Video RAM 5.1 VRAM Module</li> <li>5 Video RAM 6.1 VRAM Module</li> <li>6 Rendering Pipeline 6.1 Commands and Modu 6.2 Command Widths and 6.3 The Advance Signal 6.4 An Example Comman 6.5 Extensions and Generar 7 Rendering Pipeline Mode</li> </ul>                | f the log       16         f the log       17         17       17         18       18         19       19         les       20         l Serialized Commands       21                                                                                                           |

| 5                    | <ul> <li>4.1 Clock Speeds</li> <li>4.2 Determining the end of 4.3 Resetting</li> <li>5 Video RAM 5.1 VRAM Module</li> <li>5 Video RAM 6.1 VRAM Module</li> <li>6 Rendering Pipeline 6.1 Commands and Modu 6.2 Command Widths and 6.3 The Advance Signal 6.4 An Example Comman 6.5 Extensions and Genera 7 Rendering Pipeline Mod 7.1 2D Transform</li> </ul> | f the log       16         f the log       17         17       17         18       18         19       19         les       20         l Serialized Commands       21                                                                                                           |

| 5                    | <ul> <li>4.1 Clock Speeds 4.2 Determining the end of 4.3 Resetting</li></ul>                                                                                                                                                                                                                                                                                 | f the log       16         f the log       17         17       17         18       18         19       19         les       20         l Serialized Commands       21         d Sequence       21         ality       23         lule Descriptions       23         24       24 |

| 5                    | <ul> <li>4.1 Clock Speeds 4.2 Determining the end of 4.3 Resetting</li></ul>                                                                                                                                                                                                                                                                                 | f the log       16         f the log       17         f the log       17         17       17         18       19         les       19         les       20         l Serialized Commands       21                                                                               |

|    | 7.4             | Line Draw                                | 26        |  |  |  |  |  |

|----|-----------------|------------------------------------------|-----------|--|--|--|--|--|

|    |                 | 7.4.1 Command Format                     | 26        |  |  |  |  |  |

|    | 7.5             | Pixel Fill                               | 26        |  |  |  |  |  |

|    |                 | 7.5.1 Command Format                     | 27        |  |  |  |  |  |

| 8  | 3D '            | Transformation Module                    | <b>27</b> |  |  |  |  |  |

|    | 8.1             | Math                                     | 28        |  |  |  |  |  |

|    | 8.2             | Matrices and Matrix Multipliers          | 30        |  |  |  |  |  |

|    |                 | 8.2.1 Matrices                           | 30        |  |  |  |  |  |

|    |                 | 8.2.2 Matrix Multiplier                  | 30        |  |  |  |  |  |

|    | 8.3             | 3D Transformation Module                 | 31        |  |  |  |  |  |

|    |                 | 8.3.1 "Burst" Mode                       | 32        |  |  |  |  |  |

| 9  | Visu            | alization Modules                        | 33        |  |  |  |  |  |

|    | 9.1             | 3D Visualization Module                  | 35        |  |  |  |  |  |

|    | 9.2             | Visualization Module Manager             | 37        |  |  |  |  |  |

| 10 | Imp             | lementation Notes: Testing and Debugging | 37        |  |  |  |  |  |

| 11 | Kno             | wn Bugs                                  | 38        |  |  |  |  |  |

| 12 | 2 Conclusion 39 |                                          |           |  |  |  |  |  |

# List of Figures

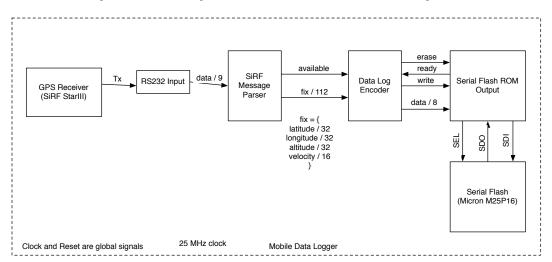

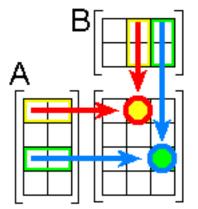

| 1 | Mobile data logger block diagram.                | 7  |

|---|--------------------------------------------------|----|

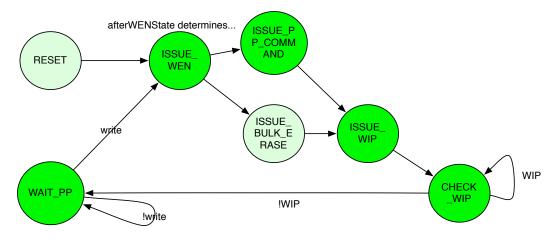

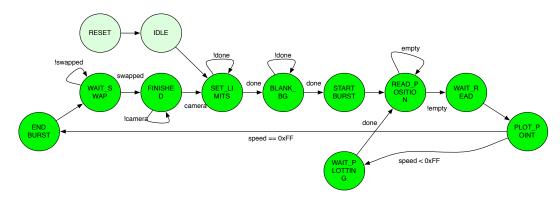

| 2 | Flash writing FSM state transition diagram       | 14 |

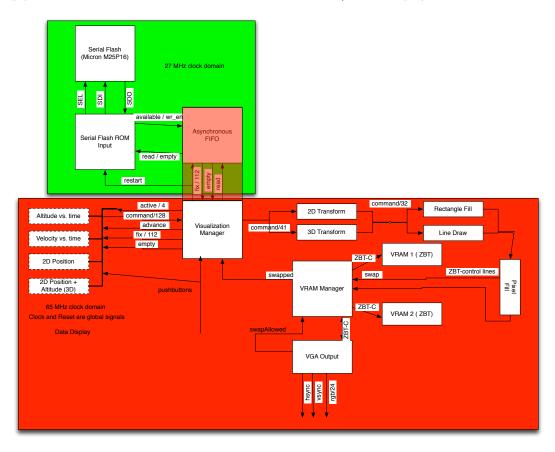

| 3 | Visualization system block diagram.              | 15 |

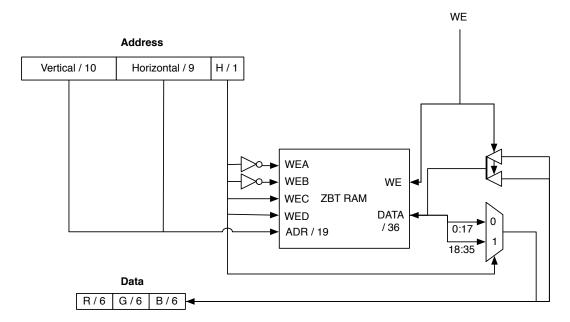

| 4 | Video RAM virtual address decoding               | 18 |

| 5 | Illustration of matrix multiplication.           | 31 |

| 6 | 3D Visualization Module state transition diagram | 35 |

# List of Tables

| 1  | Nexys LED assignments         |  |  | <br> |  |  |  |  |  | 5  |

|----|-------------------------------|--|--|------|--|--|--|--|--|----|

| 2  | RS232 Input Module Ports      |  |  | <br> |  |  |  |  |  | 8  |

| 3  | SiRF Message Parser Ports     |  |  | <br> |  |  |  |  |  | 9  |

| 4  | SiRF Header Format            |  |  | <br> |  |  |  |  |  | 10 |

| 5  | Log Encoder Module Ports      |  |  | <br> |  |  |  |  |  | 12 |

| 6  | Flash ROM Writer Module Ports |  |  | <br> |  |  |  |  |  | 12 |

| 7  | Page program command format.  |  |  | <br> |  |  |  |  |  | 14 |

| 8  | Flash ROM Reader Module Ports |  |  | <br> |  |  |  |  |  | 16 |

| 9  | Position record format        |  |  | <br> |  |  |  |  |  | 16 |

| 10 | VRAM Module Ports             |  |  | <br> |  |  |  |  |  | 19 |

| 11 | Pipeline command format       |  |  | <br> |  |  |  |  |  | 20 |

| 12 | Generalized pipeline module ports           | 3 |

|----|---------------------------------------------|---|

| 13 | 2D Set Limit Command Format                 | 1 |

| 14 | 2D Transform Command Format                 | 5 |

| 15 | Rectangle Draw Command Format - Color       | 5 |

| 16 | Rectangle Draw Command Format - Endpoints   | 5 |

| 17 | Line draw command format - Color            | 3 |

| 18 | Line draw command format - endpoints        | 3 |

| 19 | Pixel Fill Command Format - Location        | 7 |

| 20 | Pixel Fill Command Format - Color           | 7 |

| 21 | VRAM Swap Command Format 27                 | 7 |

| 22 | Matrix Multiplier Module Ports              | 1 |

| 23 | Generalized visualization module ports      | 1 |

| 24 | Visualization module minor FSM module ports | 1 |

|    |                                             |   |

# 1 Overview

The goal of this project was to create a device that is capable of keeping track of where it's been, and displaying that information to the user. Because of the difficulties involved in implementing a GPS chip from scratch, it was decided to use one from a third party, and concentrate on the logging and visualization components for this project.

While the initial plan was to implement the entire system on a Digilent Nexys board, it quickly became apparent that the Nexys did not posses enough resources or I/O capability to permit this. So, the project was implemented in two parts. A Nexys board was used to implement the data logging component, reading data from the GPS chip and storing it on a Flash ROM, and the 6.111 labkit was used to generate the data visualizations.

## 1.0.1 Defaults

Unless specified otherwise, all sequential transitions occur on the rising edge of the clock, and all FSMs are Moore-type.

# 1.1 Mobile Data Logger

The mobile data logger has very little user interface: the user simply powers it on and lets it run. However, the LEDs and four-digit display provide some status information.

|                 | Table 1. Renys LLD assign | mon |

|-----------------|---------------------------|-----|

| Thing           | Purpose                   |     |

| LED $0$         | RS232 Data In             |     |

| LED 1           | Navigation Valid          |     |

| LED $2$         | Flash Write-In-Progress   |     |

| LED 3           | Flash Ready-For-Command   |     |

| LED $7$         | Reset                     |     |

| Numeric Display | Current Speed             |     |

Table 1: Nexys LED assignments

LED 0 illuminates when data is being received from the GPS chip over the RS232 chip. LED 1 illuminates when the GPS chip has obtained a lock on at least four satellites, and is now providing valid position information. LED 2 illuminates when data is being written to the flash, and when it is being erased. LED 3, somewhat redundantly, illuminates when the Flash ROM is idle. Finally, the four-digit numeric display displays the current speed of the data logger, as meters per 100 seconds, in hex.

This means that, after power-up, the user observes the following behavior from the Nexys:

1. The RS232 data in light flashes continuously, one per second, as long as the connection with the GPS chip is intact.

- 2. For the first 17 seconds after initial power-up, the write-in-progress LED is illuminated as the ROM is erased, and the ready-for-command LED is dark.

- 3. At some point, approximately 45-60 seconds after power-up, the navigation valid LED illuminates as the GPS chip obtains a position fix. Subsequently to this, the write-in-progress begins to illuminate once per second, immediately following the pulses of the RS232 data-in light, indicating that the position history is being written to the ROM.

Pushbutton seven on the Nexys board is the user reset: pressing it resets all logic on the board to its default state. As a consequence, the Flash ROM is erased as well. However, the GPS chip is not affected, and thus will not lose its position fix.

# 1.1.1 Connections and Power

The Flash ROM connects to the Nexys through one of the board's 6-pin accessory headers, and is powered from the board's internal 3.3v power regulator. The GPS chip is connected via another of the headers, but receives power directly from the source the board is connected to.

While the GPS chip uses the RS232 protocol, the TX and RX lines are TTL-level, which means that they can be connected directly to pins on the FPGA.

*Warning:* the Nexys can be powered via wall adapter, USB, or battery, and can handle any voltage in the range 4V-10V. The GPS chip is driven directly from the power input to the Nexys, but its input range is much more limited: 4.5V to 6.5V.

# 1.2 Visualization System

The visualization system was originally intended to have a fairly elaborate interface, displaying labeled axes, summary information for the data set (max speed, max altitude, etc.), and allowing the user to use the mouse to switch between visualizations, pan, scroll, zoom and rotate within them, and so forth. Though its implementation would be straightforward, this functionality could not be completed in time, and thus the systems's displays are rather bare, and interaction with the user is accomplished using the labkit pushbuttons. However, the primary functionality has been completed.

The visualization system allows the user to choose between several different views of the data. Three are rendered in 2D: altitude vs. time, velocity vs. time, and latitude vs. longitude. One is rendered in 3D: latitude, longitude and altitude.

The user can zoom, pan, and (for 3D) rotate these visualizations using the buttons the labkit. For the 2D position display, the directional buttons (up,

down, left and right) move the view to the north, south, east and west, respectively, and by holding the third pushbutton and either the up or down button, the view can be zoomed in and out.

For the 2D altitude and velocity displays, the left and right buttons scroll through the time axis, and the up and down buttons adjust the scale of the y-axis. Holding the third pushbutton and the up/down buttons adjusts the scale of the x-axis.

For the 3D displays, the pushbuttons adjust the latitude and longitude coordinates of the camera. Holding the third pushbutton and the up/down buttons adjusts the altitude of the camera. Holding the second and first pushbuttons, in combination with the directional buttons, adjusts the rotation of the camera around the appropriate axes.

# 2 Mobile Data Logger Implementation

The mobile data logger's implementation is fairly simple: it reads data from the SiRF StarIII GPS receiver over RS232, decodes the appropriate messages, formats them for storage, and then writes them to the Flash ROM.

The entire system is driven by the built-in 25 MHz clock of the Nexys.

Figure 1: Mobile data logger block diagram.

# 2.1 RS232 Input Module

The RS232 module is responsible for decoding RS232 data coming from the GPS receiver. Before we go into its implementation details, it will help to discuss how the RS232 protocol itself works.

Table 2: RS232 Input Module Ports

| Signal    | Width | I/O | Description                    |

|-----------|-------|-----|--------------------------------|

| clk       | 1     | Ι   | Clock signal                   |

| reset     | 1     | Ι   | Reset                          |

| baud16    | 1     | I   | Enable signal at 16x baud rate |

| rx        | 1     | Ι   | RS232 RX signal                |

| data      | 8     | Ο   | Byte of serial data            |

| available | 1     | 0   | High when $data$ is valid      |

## 2.1.1 RS232 Protocol

RS232 is a serial protocol for data transmission: data is transmitted one bit at a time over a single line. The "baud rate" of an RS232 connection defines how many bits may be transmitted per second. Each line is unidirectional, but most RS232 connections are bidirectional, using two lines, one in each direction.

When the line is idle, it is held at a logical 1. When a byte is to be transmitted, a 0 (the "start bit") is transmitted by pulling the line low for a single baud unit. Following the start bit, a byte of data is transmitted, MSB first. After the LSB of the byte is transmitted, a 1 (the "stop bit") is transmitted, after which the line is idle again, a single byte having been sent.

Beyond baud rate, there are a number of different parameters that result in variations to this description: there may be a parity bits, more than one stop bit, and so forth. Both devices communicating over RS232 must agree in advance on the protocol they will be using. The SiRF StarIII chip used here transmits at 57600 baud, with one start bit, one stop bit, and no parity bits.

### 2.1.2 Implementation Overview

The RS232 input module uses a technique called oversampling to ensure that it receives data accurately. It samples the RX line at a frequency sixteen times the baud rate (thus, 57600 \* 100 = 921600 times per second). When it detects a start bit, it waits until 24 16x-baud ticks have gone by (indicating that it is now 8 16x-baud-ticks into the transmission of the MSB), and then starts a counter that samples the eight data bits at 1-baud intervals. In this way, it ensures that it is sampling each bit approximately in the middle of the baud period, thus (hopefully) minimizing the effects of interference and capacitance on the value received. It also reduces the chance of a slightly out-of-frequency baud generator (as ours is) causing problems, by ensuring maximum margins on both "sides" of the bit being transmitted.

### 2.1.3 FSM

The RS232 module is a simple Moore FSM, with four states. All state transitions occur on the baud16 clock enable.

**WAITING** In the waiting state, the RX line is idle (logical 1), and the module is simply waiting for a start bit. Once a start bit is found (the line goes low), the module transitions to the SYNCHRONIZE state.

**SYNCHRONIZE** In the synchronize state, the module waits 24 baud16ticks, until the start bit has been transmitted, and the MSB is halfway through being transmitted. At this point, the modules enters the SAMPLE state.

**SAMPLE** In the sample state, the module reads eight samples from the RX line, sampling the first the immediately and waiting one baud-tick for the next seven, reading them into a shift register that will contain the received byte at the end of the process.

Once the full byte has been read, the module transitions to the STOP\_BIT state.

**STOP\_BIT** In the stop bit state, the module simply waits another 24 baud16-ticks until the stop bit has passed, and then returns to the WAITING state.

# 2.2 SiRF Message Parser Module

| Signal    | Width | I/O | Description                                          |

|-----------|-------|-----|------------------------------------------------------|

| clk       | 1     | Ι   | Clock signal                                         |

| reset     | 1     | Ι   | Reset                                                |

| data      | 8     | Ι   | RS232 byte in                                        |

| dataAvail | 1     | Ι   | High when <i>data</i> valid                          |

| fix       | 112   | Ο   | Current position                                     |

| fixAvail  | 1     | Ο   | High when $fix$ valid                                |

| messageID | 16    | Ο   | ID of the last SiRF message received                 |

| navValid  | 1     | 0   | High when the GPS chip has obtained a position lock. |

Table 3: SiRF Message Parser Ports

The SiRF message parser is responsible for reading data coming from the GPS chip through the RS232 receiver module, one byte at a time, parsing the SiRF messages that the data contains, and extracting the relevant position information from them.

As outputs, it supplies position information via the *fix* output as it is received, as well as the ID of the last message received, and a signal indicating whether the GPS chip has obtained a satellite lock (*navValid*).

# 2.2.1 SiRF Message Format

The GPS chip transmits messages in the SiRF binary message format. This defines a number of different message types, identified by a 2-byte ID, all sharing a commond header structure.

| Table 4: | CDE  | Haadan | Farmat |

|----------|------|--------|--------|

| Table 4: | SILL | пеацег | rormat |

| Start Sequence | Payload Length | Payload    | Checksum | End Sequence |

|----------------|----------------|------------|----------|--------------|

| 0xA0, 0xA2     | 2 bytes        | 1023 bytes | 2 bytes  | 0xB0, 0xB3   |

We are interested in messages with ID 0x41 ("Geodetic Navigation Data") in the SiRF specification), and don't care about the rest. These messages are 91 bytes long, and contain a variety of data fields, including the ones we are interested in: latitude, longitude, altitude, and velocity.

### 2.2.2 Implementation Overview

The message parser module was implemented with two FSMs, one "major', one "minor'.

### 2.2.3 Major FSM

The major FSM is responsible for parsing all incoming message headers, identifying when a message with ID 0x41 is being received, and alerting the minor FSM when this is the case.

It consists of seven states.

**RESET** The reset state simply clears all outputs and prepares to enter the IDLE state once *reset* goes low.

**IDLE** In the idle state, no message is currently being received. When we read the first start bit (0xA0) of the SirF message header, we transition to READ\_S2.

**READ\_S2** In the READ\_S2 state, we verify that the next byte in the stream is the second start bit (0xA2). If so, we continue to the READ\_LENGTH\_1 state. If not, we return to IDLE, confused.

**READ\_LENGTH** In the two READ\_LENGTH states, we read the next two bytes in the stream, representing the message length, and store their value for later use. The READ\_ID state always follows.

**READ\_ID** In the READ\_ID state, we read the next byte in the stream (the message ID field of the binary protocol header). If the message ID equals 0x41, we alert the minor FSM by raising the internal *parserStart* signal high.

Regardless of the value of the message ID, the next state is WAIT\_MESSAGE.

The last message ID received is stored in a register, and is one of the outputs of the module as a whole.

**WAIT\_MESSAGE** In this state, we simply read bytes and increment a counter, until the number of bytes we've read equals the message length (cached earlier). At which point, we know that this message is over, so we return to the IDLE state, and await another.

Explicitly waiting until the exact number of bytes have been read ensures that we will not get confused if the start and/or stop sequences ever occur in the data stream.

### 2.2.4 Minor FSM

The minor FSM is responsible for parsing the payload of a "Geodetic Navigation Data" SiRF message. The *parserStart* signal, controlled by the major FSM, indicates when one of these messages is being received.

The minor FSM generates values for the *fix*, *fixAvail*, and *navValid* outputs of this entire module.

It consists of nine states.

**RESET** Reset simply initializes the FSM's internal values, and prepares it to enter the IDLE state once *reset* falls.

**IDLE** In the IDLE state, no message is being received. If the *parserStart* signal goes high, it enters the READ\_VALID state.

**READ\_VALID** This state is responsible for reading a two-byte indicator at the beginning of the message, indicating the type of position information the GPS is supplying. It uses a two-byte shift register and a counter to read this field, and then transitions to the READ\_LATITUDE state, after discarding the next 20 bytes in WAIT.

**WAIT** The WAIT state is used by several other FSM states to wait until a certain number of bytes have arrived (discarding them), and then transition to another state.

This is useful, because the message we're reading contains a large amount of information, and we need only a small subset of it.

The *afterWaitState* register is used to store the state to transition to after this one.

### READ\_LATITUDE, READ\_LONGITUDE, READ\_ALTITUDE, READ\_SPEED

These states read their respective values from the message, and store them in a register. After the final value in the message is read (in READ\_SPEED), we return to IDLE.

| Signal   | Width | I/O | Description                                 |

|----------|-------|-----|---------------------------------------------|

| clk      | 1     | Ι   | Clock signal                                |

| reset    | 1     | Ι   | Reset                                       |

| fix      | 112   | Ι   | Current position                            |

| fixAvail | 1     | Ι   | High when $fix$ valid                       |

| data     | 8     | Ο   | Data to write.                              |

| write    | 1     | Ο   | High when <i>data</i> is valid for writing. |

| ready    | 1     | Ι   | High when the flash is accepting data.      |

Table 5: Log Encoder Module Ports

# 2.3 Log Encoder Module

The log encoder module is responsible for taking the 112-bit position fixes produced by the SiRF message parser, and serializing them into a sequence of 8-bit values to be stored on the flash.

It uses an internal counter and a shift register to write out the position values - a simple implementation.

# 2.4 Flash ROM Writer

| Signal | Width | I/O | Description                             |

|--------|-------|-----|-----------------------------------------|

| clk    | 1     | Ι   | Clock signal                            |

| reset  | 1     | I   | Reset                                   |

| memCE  | 1     | 0   | Flash chip enable                       |

| memIn  | 1     | I   | Flash serial data in                    |

| memOut | 1     | 0   | Flash serial data out                   |

| memClk | 1     | 0   | Flash serial clock                      |

| data   | 8     | I   | Data to write                           |

| write  | 1     | I   | High when $data$ should be written      |

| ready  | 1     | 0   | High when the flash is idle             |

| wip    | 1     | 0   | High when the flash is being written to |

Table 6: Flash ROM Writer Module Ports

The Flash ROM writer is responsible for interfacing with the ST Microelectronics serial flash: erasing it, and writing bytes to it. It raises *ready* high when it is able to accept data for writing. When *write* is high, it writes the byte found on *data* to the next available address on the Flash, starting at zero and automatically incrementing with each write.

The amount of time the erase and write operations take is not fixed, so after performing one of these operations we must constantly poll the chip until it indicates that the operation has completed.

# 2.4.1 Serial Flash Protocol

Communication with the flash chip occurs using a four-line bidirectional serial protocol. The serial clock, chip enable, and data input are driven by the FPGA, and the data output line is driven by the flash chip.

The protocol is based on commands. Each command is initiated by bringing the chip enable low, followed by the transmission of an 8-bit command ID on the input line, followed by (depending on the command) a sequence of additional data such as an address, or data to write. Some commands produce a response from the chip on the output line. Raising the chip enable high ends the command. Some commands will not be recognized if the chip enable is not driven high at precisely the right moment: e.g. after the command ID, after the address, etc.

Once a byte has been written to, it cannot be changed again until the entire sector its in (or the entire chip itself) is erased. Erasing sets every bit on the chip to 1.

Before issuing any command that writes or erases part of the ROM, the write enable command must be issued. The write-enable latch inside the ROM is reset after every write, and thus the command must be re-issued before every write.

The commands we need to worry about, then, are: write enable, page program (to write data), bulk erase (to erase the entire chip), and check writein-progress (to let us know when the page program and erase commands have finished executing).

### 2.4.2 FSM

The module uses one major and two minor FSMs to interact with the serial flash. The minor FSMs are responsible for shifting data in and out on the I/O lines, and quite simple. The major FSM is more complicated: it consists of six states.

**RESET** The RESET state initializes all values to their defaults. The next state is always ISSUE\_WEN, followed by ISSUE\_BULK\_ERASE;

**ISSUE\_WEN** The ISSUE\_WEN state issues a write-enable command, allowing subsequent commands to modify the data stored on the ROM, and then transitions to the state stored in the *afterWENState* register.

**ISSUE\_BULK\_ERASE** This state issues a bulk erase command, initializing the contents of the entire ROM to 0xFF and allowing it to be rewritten, then transitions to ISSUE\_WIP, in order to wait out the erase cycle.

**ISSUE\_WIP** This state issues a command that asks the ROM to return its status register. This state merely issues the command - the returned value is read in the CHECK\_WIP state, which always immediately follows this one.

Figure 2: Flash writing FSM state transition diagram.

| Command ID | Address | Dummy Byte | Bytes to write  |

|------------|---------|------------|-----------------|

| 1 byte     | 3 bytes | 1 byte     | up to 256 bytes |

**CHECK\_WIP** This state reads the value returned by the ROM in response to the status register check issued by the previous state. One of the bits in the status register indicates whether the ROM is currently being written to (in the middle of an erase or write cycle).

The status register is a single byte, but it is continuously repeated on the output line as long as the chip enable is held low. So, this state continually reads the value coming in from the ROM until the WIP bit goes low, at which point it raises the chip enable high, and transitions to the WAIT\_PP state.

**WAIT\_PP** In the WAIT\_PP state, the module is idle - waiting for *write* to go high so that it can issue a page program (PP) command.

When write goes high, we transition to ISSUE\_PP\_COMMAND.

**ISSUE\_PP\_COMMAND** In this state, we issue a page program command that writes a single byte to the currently active address. We then raise the chip enable high, increment the active address by one, and transition to the ISSUE\_WIP state to wait for the write to finish.

Once the write has finished, we will be back at the WAIT\_PP state, awaiting another byte to write.

The page program command takes the following form:

The dummy byte can take on any value. Up to 256 bytes (a single sector of the ROM) can be written any time, but given the low throughput requirements, we write one byte at a time for simplicity.

# 3 Visualization System Implementation Overview

The visualization system takes the position/velocity values stored on the ROM. It can be broken into four major subsystems: the ROM reader, the rendering pipeline, the visualization modules, and the video RAM / VGA display.

Figure 3: Visualization system block diagram.

# 4 ROM Reader / Log Decoder

The ROM reader subsystem is responsible for reading logged position/velocity information from the Flash ROM, and making it available to the rest of the system.

This is essentially the inverse of the mobile data logger, described above, and so in the interest of spending more time on the interesting topics, we will not describe its component modules in detail. As a whole, the ROM reader component can be considered a module with the following ports:

| Signal    | Width | I/O | Description                                   |

|-----------|-------|-----|-----------------------------------------------|

| clk_flash | 1     | Ι   | 27 MHz clock signal                           |

| clk_rest  | 1     | Ι   | 65 MHz clock signal                           |

| reset     | 1     | Ι   | Reset                                         |

| memCE     | 1     | Ο   | Flash chip enable                             |

| memIn     | 1     | Ι   | Flash serial data in                          |

| memOut    | 1     | Ο   | Flash serial data out                         |

| memClk    | 1     | Ο   | Flash serial clock                            |

| position  | 112   | Ο   | Position fix                                  |

| read_en   | 1     | Ι   | Read the next position, if ! <i>empty</i>     |

| empty     | 1     | 0   | Low if no positions are available to be read. |

Table 8: Flash ROM Reader Module Ports

Because reading each logged position takes approximately 152 clock cycles, the positions are stored in a 512-location FIFO queue, to ensure that there is always a constant supply of them ready for the rest of the system ton consume. The *empty* signal is low when this queue has values in it. Raising *read\_en* high for one clock when *empty* is low places the next stored position on the *position* output.

The *position* signal contains the following values:

|          | r         | Table 9: Po | sition reco | rd format |

|----------|-----------|-------------|-------------|-----------|

| Latitude | Longitude | Altitude    | Velocity    |           |

| 32-bit   | 32-bit    | 32-bit      | 16-bit      |           |

All values are integers. The latitude and longitude values are in degrees  $*10^7$ , the altitude value is in meters \*100, and the velocity value is in meters/second \*100.

# 4.1 Clock Speeds

One problem that arose while implementing this component was that, while the rest of the systems run off the same 65 MHz clock that the VGA module requires, the Flash ROM's maximum rated clock speed is 50 MHz. The solution was to make the FIFO that connects this component to the rest of the system asynchronous: the write ports are driven at 27 MHz along with the rest of the ROM reader subsystem, and the read ports at 65 MHz, along with everything else.

# 4.2 Determining the end of the log

Another issue was how to determine where the last logged position is. Because of the imprecision of the Flash chip's erase functionality, it is not practical to write an integer somewhere with every record indicating how many positions have been stored.

An easy solution was to make note of the fact that erasing the chip sets every bit to 1. Considering that a speed or altitude of 0xFFFF will never be recorded, we know we have reached the end of the log when we see a speed with that value.

However, because doing so makes the visualization modules' implementations simpler, the ROM reader does not stop reading after it finds a speed of 0xFFFF - it will continue on, filling up the FIFO with 1s. It is up to the visualization modules to recognize that this means the end of the data, and stop reading.

# 4.3 Resetting

The *reset* signal is used both at power-on to initialize the module, and by the visualization modules to tell the ROM reader to start reading from the beginning of the logged data: raising it high clears the FIFO and restarts the flash reader from address zero.

This is perhaps somewhat sloppy - it would be cleaner to have a distinct *restart* signal, and use *reset* solely for power-on initialization, or a user reset of the entire system. On the other hand, one could also call it more efficient to use *reset* for both purposes.

# 5 Video RAM

In order to support the (regrettably unfinished) advanced graphics functionality that was planned for this project (such as transparency, anti-aliasing, and so forth), it was decided to use 18-bit color, and a 1024x768 display resolution. Also, because the visualizations will be drawing figures of arbitrary complexity, it was decided to use video RAM instead of sprites. To avoid the hassle of having to perform the calculations only in the horizontal and vertical blanking periods of the VGA rendering, a double-buffered memory system was deemed necessary as well.

Since the labkit possesses two ZBT rams, the obvious choice was to use each of them as a separate video buffer. The addressing scheme posed a minor challenge, since the system needed to be able to store and address 768k values of 18 bits each, while the ZBTs were organized as 512k values of 36 bits each. While the storage capacity was there, the ZBTs are not laid out in the optimal pattern.

The solution was to use a virtual memory address for reads and writes, and implement circuitry to decode it into a physical address. The virtual address was 20 bits long, with the high-order 10 bits corresponding to the y pixel coordinate, and the low-order 10 corresponding to the x pixel coordinate.

The video RAM circuitry uses the high-order 19 bits of this virtual address as the physical address passed to the RAMs themselves, and uses the LSB to determine whether the upper or lower 18 bits of the memory location are being read from/written to. This is illustrated in the diagram below.

Figure 4: Video RAM virtual address decoding

# 5.1 VRAM Module

The VRAM module is the gateway between the rest of the system, and the ZBT RAMS. It converts the virtual addresses and read/write signals into physical addresses going out to the ZBTs.

At any given point, one of the RAMs is designated as 'active', and the other as 'inactive'. The 'active' RAM is the one that is driving the display, and the 'inactive' one is either idle, or being written to by the the rendering subsystem.

Internally, the VRAM uses two instances of a submodule ("addrDecoder") to convert between vritual and physical addresses, and a series of muxes to determine which address decoder the incoming 'active' and 'inactive' signals are connected to.

When the *swap* input goes high, the module waits until the *swapAllowed* input goes high, and then switches the roles of the active and inactive VRAMs, raising *swapped* high for one cycle once this occurs. The *swapAllowed* signal

| Signal        | Width | I/O | Description                                        |  |

|---------------|-------|-----|----------------------------------------------------|--|

| clk           | 1     | Ι   | 27 MHz clock signal                                |  |

| reset         | 1     | I   | Reset                                              |  |

| activeAddr    | 20    | I   | Virtual active VRAM address                        |  |

| activeRead    | 18    | 0   | Virtual active VRAM data                           |  |

| activeWE      | 1     | I   | Virtual active VRAM write enable                   |  |

| activeWrite   | 18    | I   | Virtual active VRAM data write                     |  |

| inactiveAddr  | 20    | I   | Virtual inactive VRAM address                      |  |

| inactiveRead  | 18    | 0   | Virtual inactive VRAM data                         |  |

| inactiveWE    | 1     | I   | Virtual inactive VRAM write enable                 |  |

| inactiveWrite | 18    | I   | Virtual inactive VRAM data write                   |  |

| swap          | 1     | I   | Request to swap active/inactive VRAMs              |  |

| swapped       | 1     | 0   | High for one clock when a swap has occurred        |  |

| swapAllowed   | 1     | I   | High when a VRAM swap is allowed by the VGA module |  |

| ZBT 0         | N/A   | N/A | Control signals for ZBT zero                       |  |

| ZBT 1         | N/A   | N/A | Control signals for ZBT one                        |  |

is generated by the VGA module, and is asserted in the middle of the vertical blanking interval.

Table 10: VRAM Module Ports

# 5.2 VGA Module

The VGA module was taken directly from the lab five assignment, and minimal modifications were made. Primarily, it was modified to read pixel data from the active ZBT RAM, and to generate the *swapAllowed* output during the vertical blanking interval (when vocunt equals 790, specifically).

# 6 Rendering Pipeline

The rendering pipeline is the core of the project. It is responsible for taking real-world coordinates from the visualization modules, transforming them into pixel (1024x768) coordinates, and then drawing the appropriate shapes on the screen.

It is divided into three basic stages: transformation, drawing, and pixel coloring, illustrated in figure 3. Note that the first two stages consist of multiple modules, each implementing a subset of the functionality that the stage performs.

The pipeline is controlled through rendering commands, which are 40-bit values somewhat similar to bytecode in a processor. Each command specifies a single operation for the pipeline to perform. They move through the pipeline from 'left' to 'right', entering the transformation stage first, then progressing through the drawing stage, and ending their journey at the pixel coloring stage. Example commands include "draw 2D line", "transform 2D point", "set 3D camera parameters", and so forth.

Commands entering the pipeline take the following format:

| Table 11: Pipeline command forma |         |          |              |  |  |  |

|----------------------------------|---------|----------|--------------|--|--|--|

| Transform Op                     | Draw Op | Pixel Op | Data Segment |  |  |  |

| 3  bits                          | 3 bits  | 3  bits  | 32 bits      |  |  |  |

----

The first 9 bits of every command is the command header, which contains opcodes for each stage in the pipeline. 0b000 is a NOOP opcode: its presence in any of the 3-bit stage opcode fields indicates that the corresponding stage should not perform any operation, and merely pass the command along to the next stage.

The specific other commands that each module (and, by extension, the pipeline) supports are listed in the module descriptions below. Those sections also explain the details of the 2D and 3D transforms.

#### 6.1**Commands and Modules**

Note that each stage of the pipeline consists of multiple modules, and, to allow for maximum flexibility, the output of every module in a stage is fed to the modules in the next stage. For example, this allows the 2D transform module to be used to transform coordinates and supply them as input to either of the drawing modules with equal flexibility. Similarly, it allows the drawing modules to receive their points from either the 2D or 3D transform modules (or, for that matter, from outside the pipeline, with no transformation at all) through the exact same mechanism.

The implementation of these inter-stage connections was a minor challenge: how to determine which module in each stage provided the output for the whole stage? A number of solutions were considered, among them muxes and tristate buses. The final solution consisted of the following rules:

- 1. The output command of every stage is the logical OR of the output command of each individual module within it.

- 2. Every stage opcode is recognized by exactly *one* module within the stage.

- 3. When a module sees an opcode that it does not recognize, it outputs an all-zero command.

- 4. When a module sees a NOOP opcode, it outputs the input command verbatim on its output.

So, when a command enters a stage, only one module recognizes it, and outputs a non-zero command - the others output zeros. The logical OR means that the output of the stage is the output of the module that recognized the opcode. This avoids the delays and additional hairy logic of muxes, and the potential bus fights of tristate drivers.

# 6.2 Command Widths and Serialized Commands

The initial plan was for every command to be 128 bits long: this would allow for most common pipeline operations to be fully described in a single command. However, based on advice that this may lead to routing problems, and would be difficult to debug on the logic analyzer, this was reduced to 41 bits for the transform-stage commands, and 32 bits for the drawing- and pixel-stage commands.<sup>1</sup> This means that most common operations are described by a sequence of commands: for instance, the "set 3D camera limits" operation consists of six commands, one for each 3D camera parameter.

# 6.3 The Advance Signal

In the execution of a command, a stage may issue multiple subcommands of its own. For instance, a command to draw a line from point (100, 100) to (100, 200) will result in 200 pixel fill commands being executed.

Here, one notices a bit of a timing issue: commands like "draw line" can take a variable number of clock cycles, depending on the length of the line being drawn. The solution is to allow every stage in the pipeline to halt the execution of all stages before it, until it has completed whatever operation it is performing. The signal used to implement this is called *advance*: every stage in the pipeline takes as input the logical AND of all the advance signals of the stages following it. When the *advance* input to a given stage is low, that means that the next stage will ignore any commands it receives, until *advance* goes high again.

The *advance* signal is also provided to components outside the pipeline (i.e. the visualization modules), to let them know when the pipeline is accepting commands.

As-implemented, the handling of *advance* in the various pipeline stages is sub-optimal. For optimal performance, each stage should only wait for the *advance* signal to go high when it needs to send a command to the next stage. If a stage is performing a lengthy calculation, it need not worry about *advance* until the calculation is over, and it needs to pass on the results.

In practice, however, this is not how I implemented things: I used *advance* as sort of a clock enable: if it goes low, everything in the pipeline preceding the stage that de-asserted it will grind to a halt. This makes the implementation and debugging much simpler, but would have to be changed if optimum performance was required, as it results in wasted clock cycles.

# 6.4 An Example Command Sequence

My explanations are likely rather poor, so just to illustrate how all this stuff works, let's go through a simple example. We want to blank out the screen, set the 2D view limits to  $x_0 = 0, y_0 = 0, x_1 = 100, y_1 = 100$ , and then draw

$<sup>^{1}</sup>$ The transform-stage commands must be 41 bits long to allow room for the 9-bit header and 32-bit input value - the input values of the other stages need not be as large

a line from (20, 20) to (80, 80). All these values are in our pre-transform, 2D coordinate system.

First, we issue a command to the rectangle drawing module directly by setting the transformation stage opcode to NOOP, and the draw stage opcode to 0b010 (the opcode for "draw rectangle"). For the pixel stage opcode, we use 0b001 (normal pixel fill, the only pixel operation implemented). In the data segment of this command, we specify the color of the rectangle we wish to draw: black. The rectangle drawing module will store the pixel fill opcode and color value we specify, and use them in the pixel fill subcommands it issues on our behalf.

Following this command, we issue two more with the same opcode pattern, but different data: the data segment of the first command contains the x and y coordinates of our rectangle's upper-left corner [(0,0)], and the second the x and y coordinates of it's bottom-right corner [(1023,767)].

advance will go low for a while as the rectangle drawing module does its work. Once it finishes, we issue a command that sets the 2D transform view limits. In this command, we set the transform stage opcode to 0b100, and the other opcodes to NOOP. The data of the first command contains the 32-bit value we desire for x0 (0). We issue three more commands identical to this one, containg the values for y0, x1 and y1, respectively.

*advance* will once again go low as the 2D transform performs preliminary calculations on these values. Once it goes high, we want to draw our line. So, we issue a line-draw command, identical in structure to our rectangle-draw command except for the opcode. We specify the color as red.

But now, instead of supplying the points to draw *ourselves* by passing them in directly, we will get the 2D transform module to do it. We send out two sets of two commands each. The transform opcode of these commands is set to 0b101, the appropriate opcode for a 2D transform, and the draw opcode is set to 0b010. The data segments of these four commands are 20, 20, 80 and 80, corresponding to starting and ending pre-transform coordinates of the lines we wish to draw. The 2D transform module performs the appropriate calulcations, and issues two commands: the first containing the transformed version of our starting point, and the second the transformed version of our ending point. It sets the draw opcode of its output commands to the draw opcode we provided on the input, and so these commands are picked up by the line drawing module, and it draws a line from pixel (204,153) to (818, 613).

Note the flexibility that this allows: let's say we wanted to draw a line from the center of the screen, to a certain point in our pre-transform coordinate system. We would simply issue our same line-drawing command, provide the first point ourself [(511,383)], and then issue a 2D transform command to provide the second point.

# 6.5 Extensions and Generality

A cool thing about this design is that the rendering system is completely nonspecific, and knows nothing whatsoever about geographical coordinates<sup>2</sup>. It can be used to render visualizations of *any* data set. Note that the *only* difference between the the three 2D visualizations are the view limits on the 2D transformation, and the data being sent to it.

In addition, the rendering pipeline as implemented here is really quite generalpurpose, and can be extended quite easily to include essentially arbitrarily complex graphical techniques, moreso than you might infer based on the limited functionality implemented within it thus far.

For instance, the initial implementation plan was to allow text to be drawn to the screen: this would be implemented as just another module and set of opcodes in the drawing stage. Additionally, 8-bit alpha transparency was planned as an additional mode for the pixel fill stage: it was to be enabled simply by changing the pixel fill opcode on the commands being issued. <sup>3</sup>

In addition, one can imagine a 3D engine operating on polygons, in which the coordinates of their vertices are transformed and then passed to a generalied polygon-fill module. Clipping, lighting, texturing, and so forth could easily be implemented through additional modules and stages. Implementing an advanced rendering system such as this was one of the early 'if time permits' goals of this project, albeit one that proved ludicrously out of reach.

# 7 Rendering Pipeline Module Descriptions

This section contains detailed descriptions of the implementations of the various modules that make up the rendering pipeline.

All pipeline modules share the same set of input and output ports, except the pixel fill module, which has no *commandOut* port, replacing it with video RAM control lines.

|            | 10010 12.  | Gonor | anzea pipenne module por |

|------------|------------|-------|--------------------------|

| Signal     | Width      | I/O   | Description              |

| clk        | 1          | Ι     | 27 MHz clock signal      |

| reset      | 1          | I     | Reset                    |

| commandIn  | 41  or  32 | I     | Pipeline command in      |

| commandOut | 32         | 0     | Pipeline command out     |

| advanceIn  | 1          | I     | Pipeline advance input   |

| advanceOut | 1          | 0     | Pipeline advance output  |

Table 12: Generalized pipeline module ports

$<sup>^{2}</sup>$ Actually, there are some hardcoded scaling factors in the 3D module, but these could be removed and made settable quite easily.

<sup>&</sup>lt;sup>3</sup>The remnants of this plan can still be found throughout the system.

# 7.1 2D Transform

As you might expect, the 2D transform module is responsible for performing two-dimensional coordinate transformations. Its operation is defined by four parameters: x0, y0, x1, and y1. These define the area in the source coordinate system that will be mapped onto screen coordinates: x0 represents the left edge of the screen, y0 the top edge. These values are 32-bit signed integers.

As input for transformation, the module accepts a single pair of 32-bit x and y values, and transforms them into 10-bit pixel coordinates. The module assumes that the input values fall within the view boundaries: if not, the module's behavior is undefined.

Mathematically, this means that given a point to transform (a, b) within the view boundaries, the output point will be given by:

$$x = (a - x_0) \frac{1023}{x_1 - x_0}$$

$$y = (b - y_0) \frac{767}{y_1 - y_0}$$

Note that this involves a division, something that is very expensive to perform on an FPGA. Fortunately however, this division does not need to involve the point being transformed: it is a function only of the view limits. So, what we can do is calculate  $\frac{1023}{x_1-x_0}$  and  $\frac{767}{y_1-y_0}$  when the view limits are set (which is presumably not very often, only once per frame), and then transform each point simply by multiplying the stored results of those calculations by  $(a - x_0)$  and  $(b - y_0)$ .

And in fact, that is exactly what this module does. It uses a Coregen pipelined divider to calculate the appropriate view limit multiplication factors, and a Coregen multiplier to perform the actual point multiplications.

All operations are performed in signed, 11.20 fixed-point values, which was chosen to be on the conservative side: such precision is not likely necessary.

The implementation of this module is as a pair of state machines: the primary state machine performs the standard point transformations, but defers to the secondary state machine to carry out the view-limit factor divisions.

### 7.1.1 Command Formats

0b001

2D Set Limit The 2D set limit operation takes the following form.

| Table 13: 2D Set Limit Command Format |             |              |                      |  |  |  |

|---------------------------------------|-------------|--------------|----------------------|--|--|--|

| Transform Opcode                      | Draw Opcode | Pixel Opcode | $x_0, y_0, x_1, y_1$ |  |  |  |

| 01.004                                | 01 0 0 0    | 01 000       |                      |  |  |  |

0b000

Four commands are required to complete the operation: the first with  $x_0$  as the data, the second with  $x_1$ , the third with  $y_0$ , the fourth with  $y_1$ .

0b000

32-bit signed

2D Transform The 2D transform operation takes the following form.

| Table 14: 2D Transform Command Format |             |              |               |  |  |  |

|---------------------------------------|-------------|--------------|---------------|--|--|--|

| Transform Opcode                      | Draw Opcode | Pixel Opcode | x,y           |  |  |  |

| 0b011                                 | 0b000       | 0b000        | 32-bit signed |  |  |  |

Two commands are required to complete the operation: the first with the x-coordinate in the data segment, the second with the y-coordinate.

# 7.2 3D Transform

Please see section 8 for a discussion of the 3D transformation module.

# 7.3 Rectangle Draw