# MASSACHUSETTS INSTITUTE OF TECHNOLOGY DEPARTMENT OF ELECTRICAL ENGINEERING AND COMPUTER SCIENCE

## **6.111 Introductory Digital Systems Laboratory**Fall 2004

**Quiz #1: October 1, 2004**

| Name | Score        |

|------|--------------|

|      | (out of 100) |

|      |              |

#### Problem 1. (10 points)

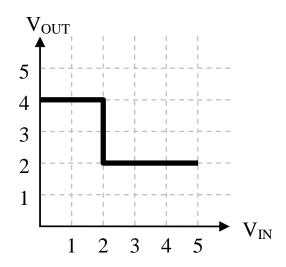

Incredible Inverters Inc. (III) manufactures a line of inverters they are hoping to sell as combinational devices that obey the static discipline. Incredibly, the voltage transfer curve for every device they make is exactly the same:

III would like for their devices to have the largest possible noise margins. Please specify choices for  $V_{OL}$ ,  $V_{IL}$ ,  $V_{IH}$  and  $V_{OH}$  that meet this goal, or briefly explain why devices with the given voltage transfer curve can't be used as combinational devices with positive noise margins.

| Briefly explain why device can't be used or specify voltage levels: $V_{\rm OL}$ |  |  |

|----------------------------------------------------------------------------------|--|--|

| $ m V_{IL}$ _                                                                    |  |  |

| ${f V_{IH}}_{\perp}$                                                             |  |  |

| $ m V_{OH}$ _                                                                    |  |  |

6.111 Fall 2004 - 1 of 5 - Quiz #1

#### Problem 2. (20 points)

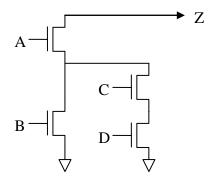

The following circuit diagram shows the pulldown circuitry for a particular CMOS gate.

(A) (10 points) Please draw the schematic for the pullup circuitry that correctly completes the implementation of the CMOS gate.

(Draw pullup schematic)

(B) (10 points) Assuming the pullup circuitry is designed correctly what is the function implemented by this gate?

Function implemented by gate: Z = \_\_\_\_\_

#### Problem 3. (20 points)

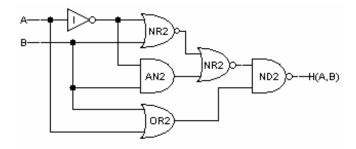

Consider the following circuit that implements the 2-input function H(A,B):

(A) (12 points) Fill in the following truth table for H:

(Fill in truth table)

| A | В | Н |

|---|---|---|

| 0 | 0 |   |

| 0 | 1 |   |

| 1 | 0 |   |

| 1 | 1 |   |

(B) (4 points) Give a sum-of-products expression that corresponds to the truth table above. (Your expression does not have to be the minimal sum-of-products.)

Sum-of-products expression: H = \_\_\_\_\_

(C) (4 points) Using the following table of timing specifications for each component, what are  $t_{CD}$  and  $t_{PD}$  for the circuit shown above?

| gate | $t_{CD}$ | $t_{PD}$ |

|------|----------|----------|

| guie |          |          |

| 1    | 3ps      | 15ps     |

| ND2  | 5ps      | 30ps     |

| AN2  | 12ps     | 50ps     |

| NR2  | 5ps      | 30ps     |

| OR2  | 12ps     | 50ps     |

t<sub>CD</sub> for circuit above (ps):\_\_\_\_\_

t<sub>PD</sub> for circuit above (ps):\_\_\_\_\_

#### Problem 4. (20 points)

Consider the following truth table for F(A,B,C):

| Α | В | C | F(A,B,C) |

|---|---|---|----------|

| 0 | 0 | 0 | 0        |

| 0 | 0 | 1 | 1        |

| 0 | 1 | 0 | 0        |

| 0 | 1 | 1 | 1        |

| 1 | 0 | 0 | 0        |

| 1 | 0 | 1 | 1        |

| 1 | 1 | 0 | 1        |

| 1 | 1 | 1 | 1        |

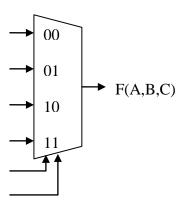

(A) (6 points) Implement F(A,B,C) using only the 4-to-1 multiplexer shown below by labeling each of its six inputs with one of the constants 0 and 1; the inputs A, B, C, or their inversions  $\overline{A}$ ,  $\overline{B}$  and  $\overline{C}$ .

(B) (8 points) Fill in the template below to create a Karnaugh map for F(A,B,C). Be sure to label the rows and columns.

(C) (6 points) Give a minimal sum of products expression for F(A,B,C).

Minimal sum of products expression: F(A,B,C) =

#### Problem 5. (30 points)

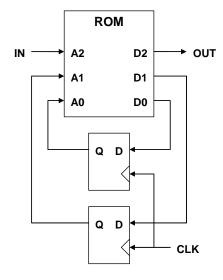

Consider the following diagram of a finite state machine. The table on the right gives the contents of the ROM. You may assume that transitions on IN are timed so as to meet the setup and hold times of the registers.

### **ROM Contents:**

| <i>A2</i> | <i>A1</i> | A0 | D2 | <b>D1</b> | $D\theta$ |

|-----------|-----------|----|----|-----------|-----------|

| 0         | 0         | 0  | 0  | 1         | 1         |

| 0         | 0         | 1  | 1  | 1         | 0         |

| 0         | 1         | 0  | 0  | 1         | 0         |

| 0         | 1         | 1  | 1  | 0         | 1         |

| 1         | 0         | 0  | 0  | 1         | 0         |

| 1         | 0         | 1  | 1  | 1         | 0         |

| 1         | 1         | 0  | 0  | 0         | 0         |

| 1         | 1         | 1  | 1  | 0         | 0         |

Timing info:

ROM:  $T_{PD} = 4ns, T_{CD} = ?$

REG:  $T_{PD} = 1.5 \text{ns}, T_{CD} = 0.5 \text{ns}$

$T_{SETUP} = 3ns, T_{HOLD} = 1.5ns$

(A) (14 points) Draw the state transition diagram for the finite state machine implemented by the circuit above. Be sure to label all the transition arcs and states with the appropriate values for IN and OUT.

(Draw state transition diagram)

(B) (8 points) Using the timing information given above, what are the constraints on the ROM's contamination delay that ensure the circuit operates correctly?

Constraints on T<sub>CD,ROM</sub>:

(C) (8 points) Using the timing information given above, what are the constraints on the period of CLK that ensure the circuit operates correctly?

Constraints on T<sub>CLK</sub>: \_\_\_\_\_