# Game Graphics using Sprites

- Sprite = game object occupying a rectangular region of the screen (it's bounding box).

- Usually it contains both opaque and transparent pixels.

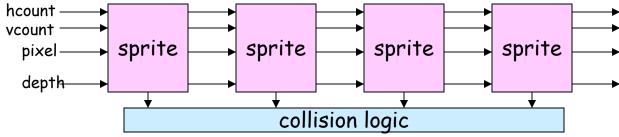

- Given (H,V), sprite returns pixel (0=transparent) and depth

- Pseudo 3D: look at current pixel from all sprites, display the opaque one that's in front (min depth): see sprite pipeline below

- Collision detection: look for opaque pixels from other sprites

- Motion: smoothly change coords of upper left-hand corner

- Pixels can be generated by logic or fetched from a bitmap (memory holding array of pixels).

- Bitmap may have multiple images that can be displayed in rapid succession to achieve animation.

- Mirroring and 90° rotation by fooling with bitmap address, crude scaling by pixel replication, or resizing filter.

6.111 Fall 2006 Lecture 16, Slide 1

### Demo (Pacman: video)

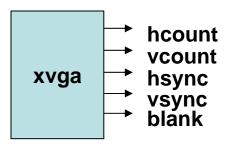

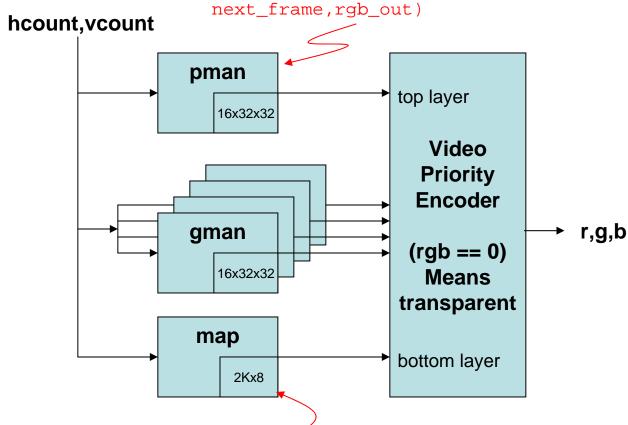

**Sprite: rectangular region of pixels**, position and color set by game logic. 32x32 pixel mono image from BRAM, up to 16 frames displayed in loop for animation:

sprite(clk,reset,hcount,vcount,xpos,ypos,color,

4 board maps, each 512x8 each map is 16x24 tiles (376 tiles)

Each tile has 8 bits: 4 for move direction (==0 for a wall), pills

# Retiming: A very useful transform

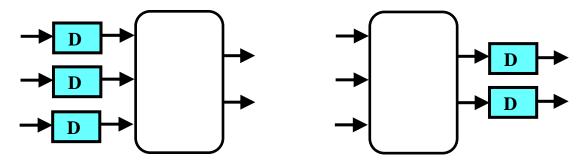

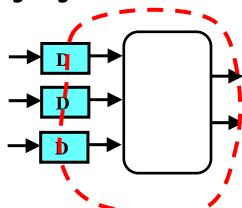

#### Retiming is the action of moving delay around in the systems

Delays have to be moved from ALL inputs to ALL outputs or vice versa

Cutset retiming: A cutset intersects the edges, such that this would result in two disjoint partitions of these edges being cut. To retime, delays are moved from the ingoing to the outgoing edges or vice versa.

#### Benefits of retiming:

- · Modify critical path delay

- · Reduce total number of registers

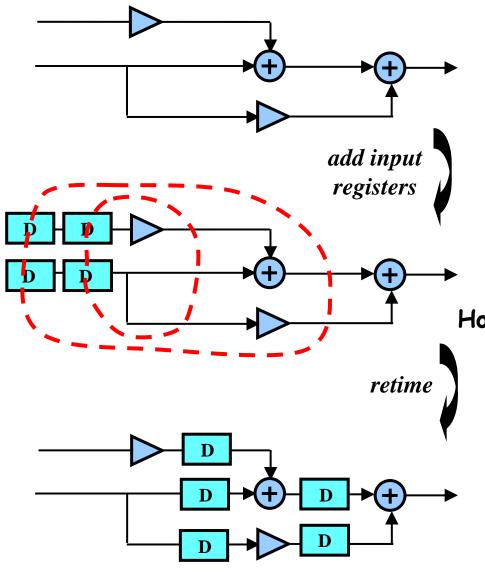

## Pipelining, Just Another Transformation (Pipelining = Adding Delays + Retiming)

Contrary to retiming, pipelining adds extra registers to the system

How to pipeline:

- 1. Add extra registers at all inputs (or, equivalently, all outputs)

- 2. Retime

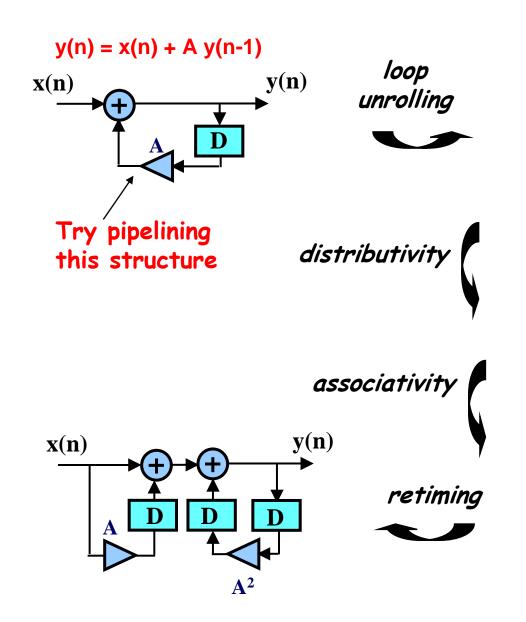

### The Power of Transforms: Lookahead

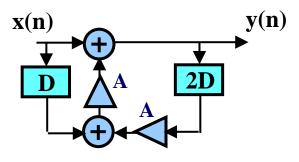

y(n) = x(n) + A[x(n-1) + A y(n-2)]

6.111 Fall 2006 Lecture 16, Slide 5

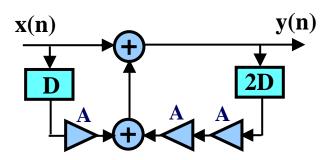

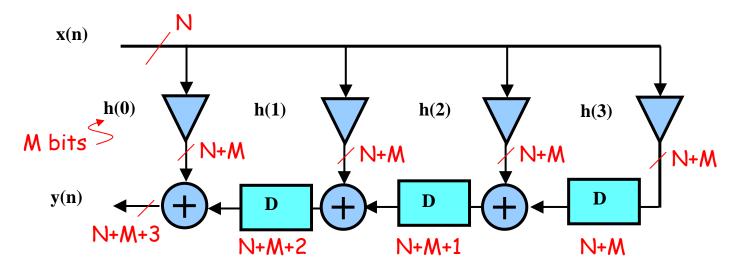

# Retiming Example: FIR Filter

Note: here we use a first cut analysis that assumes the delay of a chain of operators is the sum of their individual delays. This is not accurate.

## FIR design issues

· Keeping track required numeric precision

- · Scale fractional coefficients to integer values by multiplying by  $2^{c}$  to get C-bit coefficients. Remember to divide filter output by same scale factor (division by  $2^{c}$  doesn't require logic, just eliminate the C low order bits).

- · Xilinx IP Core has generators for many different FIR types

# FFT example

```

// Transform length: 16384

// Implementation options: Pipelined, Streaming I/O

// Transform length options: none

// Input data width: 8

// Phase factor width: 8

// Optional pins: CE

// Scaling options: Unscaled

// Rounding mode: Truncation

// Number of stages using Block Ram: 7

// Output ordering: Bit/Digit Reversed Order

fft16384u fft(.clk(clock_27mhz), .ce(reset | ready),

.xn_re(from_ac97_data[7:0]), .xn_im(8'b0),

.start(1'b1), .fwd inv(1'b1), .fwd inv we(reset),

.xk re(xk re[22:0]), .xk im(xk im[22:0]), .xk index(xk index[13:0]));

from _ac97_data[7:0] _XN RE

xk RE __ xk_re[22:0]

O \longrightarrow XN^{-1}M

XK_IM — xk im[22:0]

1 — START

XN INDEX

XK_INDEX - xk_index[13:0]

-UNLOAD

NEFT

RFD

NFFT WE

BUSY

DV

-FWD INV

reset __ FWD_INV_WE

EDONE-

DONE-

-SCALE SCH

-SCALE SCH WE

BLK EXP

-SCLR

ready — CE

```

6.111 Fall 2006 Lecture 16, Slide 8

clk 27mhź — CLK

#### FFT of AC97 data

#### To process AC97 samples:

- use Pipelined mode (input one sample in each cycle, get one sample out each cycle).

- FFT expects one sample each cycle, so hook READY to CE so that FFT only cycles once per AC97 frame

- · use Unscaled mode, do scaling yourself

- Number of output bits = (input width) + NFFT + 1

- NFFT is log<sub>2</sub>(size of FFT)

- · let number of FFT points = P, assume 48kHz sample rate

- there are P frequency bins

- positive freqs in bins 0 to (P/2 1)

- negative freqs in bins (P/2) to (P-1)

- each bin covers (48k/P)Hz

- Use XK\_INDEX to tell which bin's data you're getting out

- Typically you want magnitude = sqrt(xk\_re^2 + xk\_im^2)

# Verilog Event Processing

- · "Active" events

- Continuous assignments

- Statements within active always blocks

- Blocking assignments (=)

- RHS of non-blocking assignments (<=)</li>

- · Active events are evaluated in arbitrary order

- Interleaved execution of statements in different active always blocks or continuous assignments is possible

- Statements are executed sequentially only with respect to other statements within the same always block

- Assignments to LHS of non-blocking assignments happens after all active events have been processed

- Because of interleaved execution, blocking assignments can lead to nondeterministic behavior (this is bad!).

6.111 Fall 2006

#### = vs. <= inside always

```

always @(posedge clk) begin

a = b; // blocking assignment

module main;

b = a; // execute sequentially

req a,b,clk;

end

always @(posedge clk) begin

a <= b; // non-blocking assignment</pre>

b <= a; // eval all RHSs first

end

always @(posedge clk) a = b;

always @(posedge clk) b = a;

initial begin

always @(posedge clk) a <= b;</pre>

clk = 0; a = 0; b = 1;

always @(posedge clk) b <= a;</pre>

#10 clk = 1;

#10 $display("a=%d b=%d\n",a,b);

$finish;

always @(posedge clk) begin

end

a <= b;

endmodule

b = a; // urk! Be consistent!

end

```

Rule: <u>always</u> change state using <= (e.g., inside always @(posedge clk)...)

6.111 Fall 2006 Lecture 16, Slide 11