Virtual Juggling

Chris Wilkens and David Rush 6.111 December 14, 2005

#### Abstract:

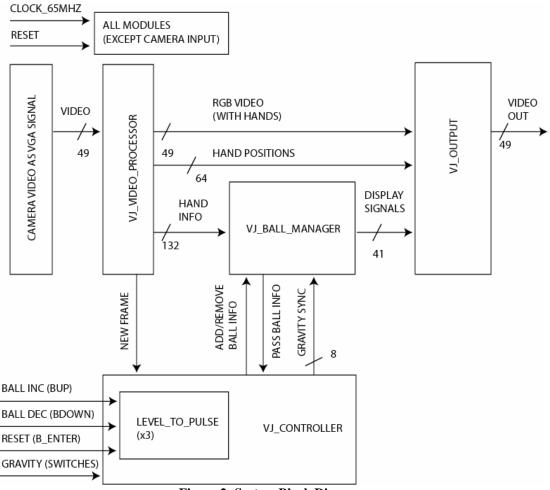

The Virtual Juggling Simulator is designed to allow a user to juggle virtual balls by moving their hands in the air. A camera is focused on a user whose hands are found by using a threshold for the input color. The hand's position, velocity and state (based on past and current velocities) are calculated and passed on to a Ball Manager. The Ball Manager determines each ball's new position, velocity and state determined on by their old states and the current inputs. The Ball Manager then passes on to the Output module if and where to display each of the 31 balls on the next frame and the balls are overlaid onto the raw image passed from the camera and displayed on a monitor. The balls' state includes if it is in play, in a hand, in the right hand or left hand, its direction and what its x and y velocity and position are. The hands can be in a throw or catch state. Button and switch inputs are wired from the labkit to reset system, add to or remove balls from the system and to set the gravity for the system. The functionalities of the system are controlled by the major Video Processor, Ball Manager, Output and Controller modules each with a number of submodules.

# **Table of Contents**

| Table of Contents                 | ii  |

|-----------------------------------|-----|

| List of Figures                   | iii |

| Overview                          |     |

| Module Structure                  |     |

| Camera Input Module               |     |

| Controller                        |     |

| Level to Pulse                    | 5   |

| Video Processor                   | 5   |

| Hand Detector                     | 6   |

| Hand Logic                        | 7   |

| Ball Manager                      |     |

| Block Random Access Memory (BRAM) |     |

| Physics                           |     |

| Display                           |     |

| Output Module                     |     |

| Aggregate Ball Sprite Memory      |     |

| Testing                           |     |

| Conclusion                        |     |

| Appendix: Verilog Source          |     |

|                                   |     |

# List of Figures

| Figure 1: Screenshot of the Simulator       | . 2 |

|---------------------------------------------|-----|

| Figure 2: System Block Diagram              |     |

| Figure 3: Controller Simulation Results     |     |

| Figure 4: Level to Pulse simulation results | . 5 |

| Figure 5: Video Processor Block Diagram     |     |

| Figure 6: Ball Manager Simulation Results   |     |

| Figure 7: Ball Manager Block Diagram        |     |

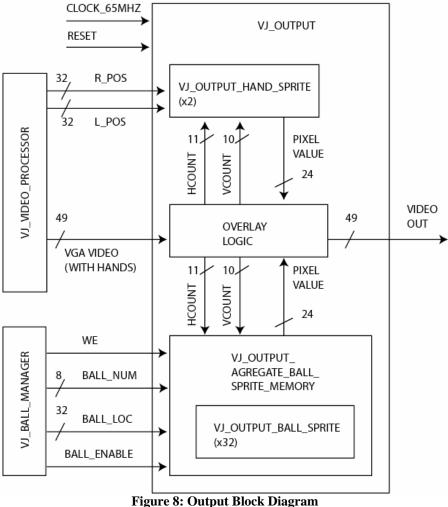

| Figure 8: Output Block Diagram              | 15  |

### Overview

The Juggling Simulator is designed so that a user can juggle virtual balls on a screen by moving their hands in space. The user stands in front of a camera with their hands exposed and they are found by taking the center of mass of the red pixels within the screen. The video assumes that there is one hand on each side of the screen so it finds the center of mass of the red pixels for each side of the screen and displays a small green square where it finds each hand so that their locations can be seen by the user. The pixels that are considered red are found by setting a threshold value to compare to the incoming pixels. Flesh comes up as red as do most warm colors so it is important to have a dark background and all flesh but the hands covered to reduce noise within the system.

As the hands move around their positions are updated each frame which is 60 times per second. From their current position and past positions their velocity and acceleration are calculated and from that throw and catch signals are generated for the hands based on empirically found threshold values. If the hand has accelerated upwards and decelerated beyond a threshold value it is said to be in a throw state for one frame and will release one ball from the hand at its current position and velocity if is holding a ball. If the hand is not moving up it is said to be in a catch state and will catch a ball if the ball is moving down and is in the proximity of the hand. The number of balls a hand can catch is only limited by the number of balls in the system.

Once a ball has been released from the hand it is governed by the laws of virtual physics. The new ball position is calculated each frame by using its current velocity. Each frame the x velocity remains constant unless the ball collides with a side edge of the screen in which case it bounces off with one half of the impact x velocity. If the ball hits the bottom edge of the screen it rebounds with the same y velocity in the opposite direction. If the ball collides the top edge of the screen the new y velocity is set to one pixel per frame in the downward direction. Each frame the y velocity is updated by subtracting the current gravity. This gives the ball acceleration in the downward direction.

The user can modify the juggling experience by pressing buttons and setting switches on the labkit. If the user presses the enter button the system is set to its default setting with three balls in the system- two in the right hand and one in the left. Balls can be added or removed from the system by pressing the up and down buttons. The minimum number of balls is zero and the maximum is 31. When added the balls are placed alternately in the right and left hands. Switches five through zero set the gravity for the system with the high order switches corresponding to the more significant bits. When switch seven is on all the pixels that are determined to be red are displayed as red on the screen otherwise the video output is simply that of the input. With this feature it is easy to identify sources of noise and more easily see where the hand is in relation to the screen. When on, switch six tints each half the screen based on what state each hand is in. If the half of the screen is tinted blue the hand is in a catch state, if gray it is neither in a catch or throw state and when it is tinted green it is in a throw state.

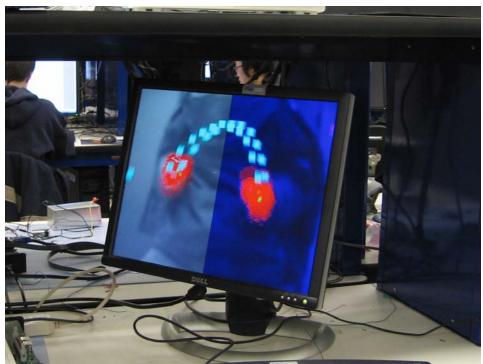

**Figure 1: Screenshot of the Simulator**

This shot shows David juggling 32 balls in the simulator. One can clearly identify his hands (red) and the 32 cyan balls. Based on the tinting of the screen, one can see that the left hand is not in a catch state, while the right hand is.

# **Module Structure**

The main module of the simulator is the VIRTUAL\_JUGGLING module. This model receives the VGA signal of the camera image and performs all necessary processing before the signal is sent to the output. To accomplish this, it contains instantiations of the major blocks of the system.

Within this module are many wires that will henceforth be grouped for simplicity. These wires come in three basic flavors: video signals, 32-bit vectors, and narrow logic signals. The video signals are composed of three 8-bit color channels, four single-bit control signals (sync, blank, hsync, vsync), and 11 and 10 bit *hcount* and *vcount* signals. In general, all position and velocity measurements are carried as 32-bit vectors in which the top 16 bits code the 'x' value and the bottom 16 bits code the 'y' value. Each of these 16 bit values is encoded as a signed, two's-complement value with 5 fractional bits. Finally, there are a few miscellaneous signals that represent their own unique codes. The major modules of the system are shown below.

## Camera Input Module

(by 6.111 staff and Chris Wilkens)

The first block in the video pipeline translates the camera's input signal into a VGA signal. It decodes NTSC video from the camera and buffers it to the ZBT memory, from which it is read out and formed into a VGA signal. This implementation uses the ZBT buffering and output provided by the 6.111 staff with a few small modifications. First, on the output end we downsample the image such that a pixel from the camera occupies four pixels of the 1024x768 XGA display. This allows us to fill the entire output frame with video from the camera. One advantageous result of this fact is that we need not read from the ZBT frame buffer as frequently, which enables the second modification. In order to do color comparisons, we modify the existing implementation to buffer 18 bits of information for each pixel. This gives us 8 bits of the Y and Cr values and 2 bits of the Cb (the Cb is not necessary for our color detection.) Since the Video Processor does color detection based on the Y and Cr signals, we keep these signals intact instead of producing reasonable RGB values at the output of this module. Once this

module has generated the proper video signals, they are subsequently sent to the Video Processor.

# Controller

(by David Rush)

The Controller module takes in a number of signals from the labkit and the video processor and outputs signals synchronized to *new\_frame\_sync* that can be used by the ball manager.

The inputs to the Controller are *clk*, *new\_frame\_raw*, *reset\_raw*, *add\_ball\_raw*, *dec\_ball\_raw* and *gravity\_raw*. The clock runs at 65MHZ and comes from the labkit. The one bit *new\_frame\_raw* signal comes from the Video Processing module and signals that a new frame has started. The *reset\_raw* is a one bit inverted (so pressed is high and depressed is low) and debounced button from the labkit as are the *add\_ball\_raw* and *dec\_ball\_raw* signals. The *gravity\_raw* is an eight bit signal from the debounced switches on the labkit.

The outputs of the Controller are *new\_fram\_sync*, *reset\_sync*, *add\_ball\_sync*, *dec\_ball\_sync* and *gravity\_sync*. They are each one bit except for the eight bit *gravity\_sync* signal and are all sent into the Ball Manager to be used by the Physics module and Display module.

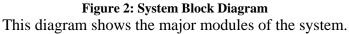

Figure 3: Controller Simulation Results

The controller receives signals at different times during the frame and synchronizes all outputs with *new\_frame\_sync*

Within the Controller each of the output signals are created using the input signals. Within an always block that triggers at each positive edge of the 65 MHZ clock a number of signals are assigned using non blocking assignments. The *new\_frame\_sync* is assigned to *new\_frame\_raw* and *gravity\_sync* is assigned to *gravity\_raw* if *new\_frame\_raw* or it remains *gravity\_sync*. The *reset\_sync* signal is set to one if *new\_frame\_raw* and *reset\_hold* are high otherwise zero. The *reset\_hold* signal is assigned to one if *reset\_raw* is high otherwise it is set to zero if *new\_frame\_raw* is high otherwise it is set to zero if *new\_frame\_raw* is high otherwise it is left *reset\_hold*. The process creates a *reset\_sync* signal that is set to one

for one clock cycle synchronized with *new\_frame\_sync* if the reset button was pressed any time during the preceding frame. The same process was used to create the *add\_ball\_sync* and *dec\_ball\_sync* signals except the \_hold signals were replaced with *add\_ball\_hold* and *dec\_ball\_hold*. Also for the assignment of *add\_ball\_hold* and *dec\_ball\_hold* the analogous *reset\_raw* signal was replaced with an *add\_ball\_pulse* and a *dec\_ball\_pulse* which came from sending the *add\_ball\_raw* and *dec\_ball\_raw* signals into their own Level to Pulse module instances to return the *add\_ball\_pulse* and *dec\_ball\_pulse* signals that are high for only 1 clock cycle regardless of how long the buttons were held down. Registers were created to hold values for each of the signals that were assigned within the always block.

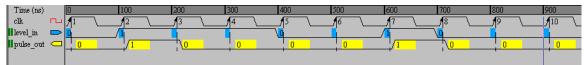

#### Level to Pulse

The level to pulse takes in an input that is high for any number of cycles and outputs a signal that is high for only the first clock edge after the input signal went high.

The inputs are *clk* and *level\_in* and the output is *pulse\_out*. At each positive edge of the clock *level\_hold* is assigned to *level\_in* and pulse out is assigned to the combination of *level\_in* and not *level\_hold*. A register is used to store each *level\_hold* and *pulse\_out*.

**Figure 4: Level to Pulse simulation results** The level to pulse receives a level input and returns a one clock pulse

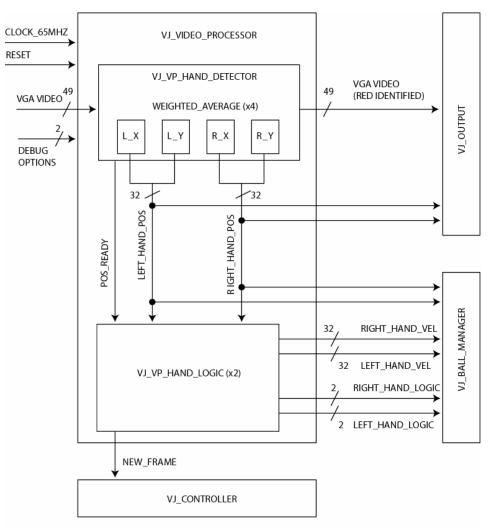

## Video Processor

(by Chris Wilkens)

The VJ\_VIDEO\_PROCESSOR module processes the VGA signal from the camera modules and determines the location and action of the juggler's hands. It determines the position and velocity information and forwards them to the appropriate modules. When the positions are ready for a given frame, it raises the *new\_frame* signal to notify the ball manager that it can begin its physics calculations.

**Figure 5: Video Processor Block Diagram** This diagram shows the modules of the Video Processor.

As seen in the block diagram, the specific implementation of the video processor is composed of two major parts: the hand detector, which locates the hands in the image, and the logic parser, which translates a series of positions into action signals that can be sent to the ball manager. In addition to providing the proper signals to these modules, the video processor modifies the output by tinting the flesh-colored pixels red. Finally, the *new\_frame* signal is simply the AND of the *logic\_ready* signals from the two hand logic modules.

#### Hand Detector

The hand detector module of the video processor watches the streaming VGA signal to calculate the location of the hands. Abstracted as a black box, this module takes the VGA color signal as input and returns the positions of the hands in the frame when the frame has been completely streamed. For each pixel, it also raises the *hand\_pixel*

signal whenever the current pixel belongs to the hand (to allow the video processor to change its color.) In order to signal other components of the video processor, a *pos\_ready* pulse is raised for one clock cycle when the hand positions are ready.

For our implementation, we define the position of the left hand to be the center of mass of all flesh-colored pixels in the left half of the screen (or right half for the right hand.) Each coordinate of each hand is calculated by keeping a running sum of the appropriate coordinate values along with a count of the number of elements in the sum. Once the frame has passed, these two numbers in the sums are divided and the result becomes the appropriate coordinate of the hand. This is accomplished with four instances of a weighted average module (one for each coordinate to be calculated.) Due to timing delays through the divide module, it takes 32 cycles after the end of the frame in order to perform the division. Thus, in order to ensure that the process has ample time to complete, we wait many clock cycles until the vertical scan reaches line 770 before raising the *pos\_ready* signal. The output position is registered when *pos\_ready* is raised, and the internal sums are reset on the vertical sync signal.

#### Hand Logic

Two instances of the Hand Logic module sit beside the hand detector in the video processor. They watch the hand positions to determine whether or not the hand is throwing or catching. Abstracted, each module takes the new position and *pos\_ready* signal and produces the hand velocity and logic signals. The hand logic signals consist of two bits, a catch bit and a throw bit (*hand\_logic*[1] is throw, *hand\_logic*[0] is catch.) The catch bit will be high whenever the hand is in a state in which the system deems that the hand could be catching, leaving the details of the catch timing up to the ball manager. In contrast, the throw signal is a pulse held high for only a single frame. When these values are computed, the module raises a *logic\_ready* signal to notify others that the logic has been calculated.

This is, perhaps, the most interesting part of the video processor because it has the most room for modifications. There are an infinite number of ways one could determine a throw or a catch, but we chose a fairly simple implementation. First, we decided that if the hand was moving up, then it wasn't catching a ball. This seemed reasonable, though we realized that it isn't entirely true in real life. That said, we set a threshold (slightly positive to accommodate noise) for which the hand would be considered catching if its velocity was under that value. Another aspect we noted was that the positions tended to fluctuate due to noise. To compensate for this, we maintained a history of the last four velocities and took the average in order to compute the "actual" velocity of the juggler's hand.

The throw signal was more complicated. If we assumed that the juggler was not holding the balls, then a throw would occur by conservation of momentum whenever the hand decelerated. Thus, we decided to locate throws based on the acceleration of the hand. As with the velocity, we buffered the last four accelerations to get an average and then put a threshold on that average. Our final dilemma was that the throws would tend to "bounce," just like a metal button. For this, we effectively debounced the throw signal by specifying that the hand couldn't throw again until it had been out of the acceleration region for six consecutive frames. This effectively ensured that we only signaled one throw per movement from the juggler, and the appropriate output signal was raised for a single frame.

Ultimately, these values required one clock cycle to produce, so the hand logic module introduces a one cycle delay after the *pos\_ready* signal before all the hand information is ready.

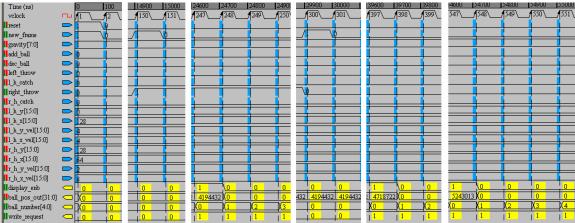

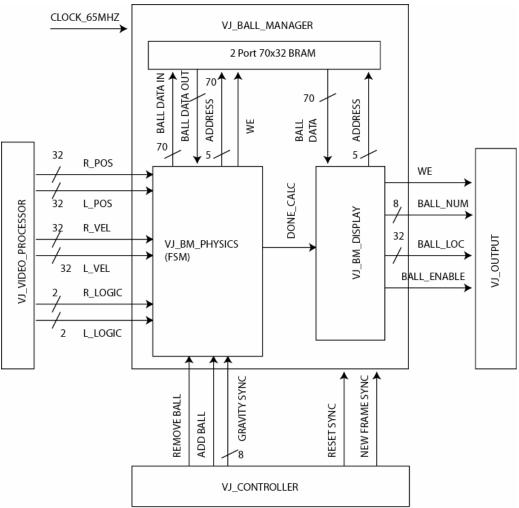

#### **Ball Manager**

The Ball Manager takes in signals from the Video Processor and Controller and based on those signals and the balls' current states determines what to do next with the balls and then it sends to the output module if and where to display the balls. The ball manager is composed of three submodules and a dual port 70 bit by 32 address Block RAM (BRAM).

The inputs to the Ball Manager are a 65 MHZ clock from the labkit, a reset, an  $add\_ball$ , a  $dec\_ball$ , and an eight bit gravity signal from the Controller all synchronized to a *new\_frame* signal which also comes from the controller. There are also signals from the video processor which are *left\_throw*, *right\_throw*, *l\_h\_catch*, *r\_h\_catch*, *l\_h\_y*, *l\_h\_x*, *l\_h\_y\_vel*, *l\_h\_x\_vel*, *r\_h\_y*, *r\_h\_x*, *r\_h\_y\_vel*, and *r\_h\_x\_vel*. The clock determines the cycles per second of the system. The one bit reset signal returns the ball manager to its default state. The one bit *add\_ball* and *dec\_ball* signals add and remove balls from the system with a minimum of zero and a maximum of 31 balls. The eight bit gravity signal determines how fast to balls accelerate in the downward direction. The one bit *new\_frame* signals to the system that a new frame is starting and all the balls' states need to be recalculated. The *left\_throw*, *right\_throw*, *l\_h\_catch* and *r\_h\_catch* are each one bit signals indicating that the left and right hands are in a throw or catch state for that frame. The signals *l\_h\_y*, *l\_h\_x*, *l\_h\_y\_vel*, *l\_h\_x\_vel*, *r\_h\_y*, *r\_h\_x*, *r\_h\_y\_vel*, and *r\_h\_x\_vel* are each 16 bit signed values and give the left and right hand's y position, x position, y velocity and x velocity with new values being supplied each frame.

The outputs of the Ball Manager are all sent to the output module and are *display\_enb*, *ball\_pos\_out*, *ball\_number*, and *write\_request*. The one bit *display\_enb* signal indicates that the ball for which information is currently being sent is to be displayed. The *ball\_pos\_out* is a 32 bit signals with the x position in the upper 16 bits and the y position in the lower 16 bits. The *ball\_number* is a 5 bit signal indicates that the ball manager wants the information it is sending to be taken by the output module. The output module can be thought of as a memory with the *write\_request* signal equivalent to the write enable and the other signals the values that are to be stored in the memory.

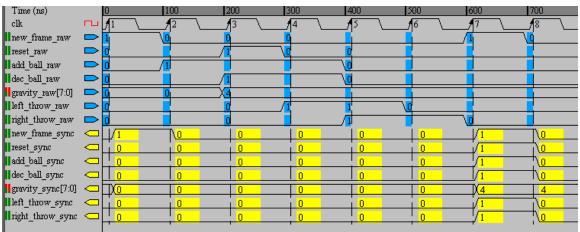

Figure 6: Ball Manager Simulation Results

The ball manager takes in all its inputs and sends values to the output module at the appropriate times. After a throw between clock cycles 150 and 300 the outputs *write\_request* as well as display enable and a ball position are given at clock number 397 for ball number zero since it was thrown from the right hand and is in the air and thus needs to be displayed by the display module

Within the Ball Manager the Physics and Display modules are instantiated and wired together. The *clock*, *reset*, *add\_ball*, *dec\_ball*, *gravity*, *new\_frame*, *left\_throw*, *right\_throw*, *l\_h\_catch*, *r\_h\_catch*, *l\_h\_y*, *l\_h\_x*, *l\_h\_y\_vel*, *l\_h\_x\_vel*, *r\_h\_y*, *r\_h\_x*, *r\_h\_y\_vel*, and *r\_h\_x\_vel* signals are all wire directly to up as inputs to the Physics module. The 70 bit *ball\_info\_in* from the output of the BRAM is also wired as an input of the Physics module. The outputs of the Physics module are the 70 bit *ball\_info\_out*, five bit *count\_addr* and one bit *wea*, which are wired up to the BRAM, and the one bit *done\_calc* which is sent as an input to the Display module.

The inputs of the Display module are wired up to the 65 MHZ clock. The one bit reset and *new\_frame* are taken directly from the inputs to the Ball Manager and the one bit *done\_calc* is wired from the output of the Physics module and 70 bit *info\_from\_bram* is wired to the b port of the dual port BRAM. The outputs of the Display module are the five bit *bram\_addr\_b* which is wired to the "b" port address of the BRAM, the 32 bit *ball\_pos\_out* which is wire directly to the Ball Manager output as are the one bit *display\_enb*, five bit *ball\_number*, and one bit *write\_request*.

The 70 bit wide by 32 address deep Block RAM (BRAM) is wired within the Ball Manager as well. Both the "a" and "b" clocks are wired to the 65 MHZ clock. The a port address is wired to five bit *count\_addr* from the Physics module and the 70 bit data input is wired to the *ball\_info\_out* (out of the Physics module). The 70 bit "a" output is wired to *ball\_info\_out* and sent to the Physics module. The five bit "b" address is wired to the *bram\_addr\_b* from the Display module and the 70 bit "b" output is wired to the *info\_from\_bram* that is given to the Display module.

**Figure 7: Ball Manager Block Diagram** This diagram shows the smaller modules of the ball manager.

#### **Block Random Access Memory (BRAM)**

The dual port Block Random Access Memory stores the state of each ball in its 70 bit wide by 32 location memory. The "a" port is read/write and is used by the Physics module to retrieve ball data from the BRAM and store the new ball data back into it. The "b" port is read only and is used by the Display module to take the ball data and extract the current position and state and send it onto the output module.

#### Physics

The Physics module is the biggest and most complex part of the ball controller. The calculations for each ball's position, velocity and state are done within this module and results are stored in a dual port 70 bit by 32 location BRAM. The Physics module takes in inputs from the Controller, the Video Processor and the BRAM and it outputs data to the BRAM and a signal indicating the calculations for that frame are done. The Controller inputs (wired in through the Ball Manager) control whether the system should be reset, a new frame should be processed whether a ball should be added or removed from the system and what gravity is. Video Processor inputs (also wired in through the Ball Manager) give the left and right hand's x and y positions and velocities as well as the left and right hand throw and catch signals. The input from the BRAM gives each ball's current state, position and velocity. The outputs determine if, what and where in the BRAM the ball data should be stored as well as indicate if the Physics module is done with its calculations and storage for the frame.

The inputs to the Physics module are a 65 MHZ clock from the labkit, a *reset*, an add\_ball, a dec\_ball, and an eight bit gravity signal from the Controller all synchronized to a *new\_frame* signal which also comes from the controller. There are also signals from the video processor which are *left\_throw*, *right\_throw*, *l\_h\_catch*, *r\_h\_catch*, *l\_h\_y*,  $l_h_x$ ,  $l_h_y_vel$ ,  $l_h_x_vel$ ,  $r_h_y$ ,  $r_h_x$ ,  $r_h_y_vel$ , and  $r_h_x_vel$ . The final input is *ball\_info\_in* from the BRAM. The clock determines the cycles per second of the system. The one bit reset signal returns the Physics module to its default state. The one bit add ball and dec ball signals add and remove balls from the system with a minimum of zero and a maximum of 31 balls. The eight bit gravity signal determines how fast to balls accelerate in the downward direction. The one bit *new\_frame* signals to the system that a new frame is starting and all the balls' states need to be recalculated. The *left\_throw*, *right\_throw*, *l\_h\_catch* and *r\_h\_catch* are each one bit signals indicating that the left and right hands are in a throw or catch state for that frame. The signals l h y, l h x,  $l_h_y_vel$ ,  $l_h_x_vel$ ,  $r_h_y$ ,  $r_h_x$ ,  $r_h_y_vel$ , and  $r_h_x_vel$  are each 16 bit signed values and give the left and right hand's y position, x position, y velocity and x velocity with new values being supplied each frame. The 70 bit *ball\_info\_in* from the BRAM is contains each balls' state, position and velocity and is used to determine the new state, position and velocity in combination with the inputs.

The outputs for the Physics module are *ball\_info\_out, count\_addr, done\_calc* and *wea*. The 70 bit *ball\_info\_out* signal is the new position, velocity and state of each ball and the *count\_addr* is the current ball that is being updated and written back into memory at the address corresponding to it's ball number. The *done\_calc* signal is a one bit signal to indicate to the display module that all the physics for the frame has been calculated. The *wea* is the write enable for the BRAM.

A number of parameters were used to simplify expressions and keep the code from being cluttered with numbers. They are *ball\_w*, *ball\_h*, *hand\_h*, *hand\_w*, *screenw*, *screenh*, *ball\_right*, *ball\_left*, *ball\_down*, *ball\_up*, *read\_state* and *write\_state*. The first six are just the sizes of the balls, hands and screen and can be changed to optimize the system. Bigger hands made it easier to catch. Bigger balls meant they hit walls sooner an different screen sizes would have affected the display. The *ball\_* parameters are the states of the balls when moving around when in play and not in the hands. The *\_states* signal if the system is in a read state (reading from BRAM) or write state (writing to BRAM).

The first thing the system does is parse the incoming 70 bit *ball\_info\_in* and assign *in\_play\_in*, *in\_hand\_in*, *in\_left\_in*, *in\_right\_in*, *y\_dir\_in*, *x\_dir\_in*, *ball\_y\_in*, *ball\_x\_in*, *y\_vel\_in*, and *x\_vel\_in* based on those signals. The first six signals are each one bit and are stored in the high six bits of the incoming signal. The remaining signals

are each 16 bits and are stored in the given order within the *ball\_info\_in*. The Physics module takes these signals as input and creates new values for each *in\_play\_out*, *in\_hand\_out* and so on and appends them together in a 70 bit *ball\_info\_out* that is stored back into the BRAM for each ball.

On the positive edge of the 65 MHZ clock the always block is evaluated. If there is a *new\_frame*, *done\_calc*, *count\_addr*, *wea* and *read\_hold* are set to zero. The read hold signal holds the system in the read state for two cycles so the data is retrieved and assigned to the ball input values before going into the write state. On new\_frame *count divider* is set to three. Count divider is a signal that counts to 2 and each time it reaches two it is set back to zero and the *count\_addr* is incremented (each ball takes three clock cycles in the Physics module and this ensures that each ball gets three cycles). Setting the *count\_divider* to three here means that when the first time it incremented after a reset it will return to the zero count that it needs to start with after its initial increment. Also on the new frame, reset level is set to the reset input, left throw level is set to *left\_throw, right\_throw\_level* is set to *right\_throw, add\_ball\_level* is set to *add\_ball,* and dec\_ball\_level is set to dec\_ball, this ensures that each of those signals values are valid for the entire frame. The *which* hand is also flipped if the *add* ball signal is high. This signal determines which hand each new ball is placed into (alternating each time a ball is added). If it's not a *new\_frame* then if the *count\_addr* signal has reached 31 then the *done\_calc* signal is set high and no more physics is calculated that frame. Else if *done\_calc* is not high the *count\_divider* is incremented or set back to zero if it equals two, the *count addr* is incremented if *count divider* is equal to two or it remains unchanged and the *read\_or\_write* case statement is evaluated. If the system is in the read state the read hold bit is flipped, wea is set to zero and read or write is set to read\_hold. This means that after two cycles in the read state it will enter the write state.

In the write state the state *read\_or\_write* is set back to the *read\_state* and *wea* is set to one since at the rising edge of the next clock there will be new data ready to write into the BRAM.

The rest of the write state within the Physics module is a large if else block that assigns the output values that are put assigned into *ball\_info\_out* and stored back into the BRAM. The overview is that if the system is being reset put balls zero and one in the right hand and ball two in the left and leave the rest out of the system. If the ball is in play then if the *dec\_ball\_level* is high take the ball out of play and set *dec\_ball\_level* back to zero so no more balls get removed. Otherwise if the ball is in a hand if it's in the right hand is in a throw state and a fall hasn't already been thrown (*right\_thrown* signal is low) then have the ball in play, don't have it in a hand, assign it the hand's current position, velocity and direction and raise the *right\_thrown* signal so no more balls are thrown this frame out of the right hand. The analogous case is true for the left hand. Otherwise if the ball is in a hand and no hand is throwing, assign all the outputs to the original inputs since nothing is changing for them this frame.

If the ball is not in a hand but is in play and is not removed leave it in play and check to see if it has been caught. It is caught if the right or left hand is in a catch state, the y direction of the ball is down and the ball is within a given rectangle area above the center of the hand that can be set by the hand width and length. It is placed in the hand that it is caught in if it is caught otherwise the new position velocity and direction of ball are

calculated. In the in play, not removed, not caught state the x and y velocities and positions are calculated separately depending on which direction the ball is moving. If the *x\_dir\_in* is *ball\_right* the balls x postion if it's input position plus it's input velocity. The new x velocity remains the same unless it comes within a distance of two times the velocity of the right wall and then it is halved and the x direction is also switched. If the ball is moving left the new *ball\_x\_out* is the *ball\_x\_in* minus the *x\_vel\_in* and the velocity and direction remain the same unless the ball is within two times the x vel in in which case the x direction is flipped and the velocity is halved. The y direction and velocity are done similarly except if the ball is moving down the balls position is the old position plus the velocity and the direction is the same unless it comes within two times the y velocity of the bottom of the screen in which case the direction changes and the velocity does not. Otherwise the velocity is updated by adding gravity to it each frame. If the ball is moving up the new position is the input position minus the input velocity. The direction remains the same unless the gravity is greater than the current velocity or the ball comes within two times the velocity of the top of the screen. In the later case the velocity is set to one pixel per frame. The velocity in this state is updated by subtracting gravity from the input velocity.

If the ball is not in play then if a ball is added (*add\_ball\_level*) is high the *in\_play\_out* and *in\_hand\_out* bits are set high and the *in\_left\_out* and *in\_right\_out* are set to *which\_hand and ~which\_hand* respectively. The rest of the outputs. The rest of the output values are set to zero as is *add\_ball\_level* so no more balls are added that frame. If the ball is not in play and no ball is added then all the output signals are set to zero.

#### Display

When triggered to do so the Display module reads through the BRAM memory and extracts the balls' positions and logic to send onto the output module along with which ball that data is for so it can know if and where to display each of the balls.

The inputs to the display are the clock, reset, *new\_frame*, *done\_calc* and *info\_from\_bram* signals. The clock is 65 MHZ from the *labkit*. The reset is synchronized to *new\_frame* and both come from the controller. The *done\_calc* signal comes from the Physics module and signals that the Physics has been calculated and stored for this frame and that the Display module can begin extracting the needed data to give to the output module. The *info\_from\_bram* is a 70 bit signal holding all the information about each ball that the Display module parses and sends to the output module.

The outputs are *bram\_addr\_b*, *ball\_pos\_out*, *display\_enb*, *ball\_number* and *write\_request*. The five bit *bram\_addr\_b* is the address the data is going to come from out of the BRAM. The *ball\_pos\_out* is the 32 bit signal with the x position of the current ball stored in the high 16 bits and the y position in the low 16 bits. The *diplay\_enb* is a one bit signal that determines that particular ball is to be displayed. The five bit *ball\_number* is the number corresponding to the ball for which the current position and display logic are being outputted. The *write\_request* is a one bit signal sent to the Output module which indicates that the data coming in is valid and should be stored.

Registers were created for each of the outputs and three internally used signals since all are assigned in a procedural block. The three internally used signals are a one bit *stop\_calc* that indicates that all 31 of the balls that can be used have been processed and the Display module should wait for a *new\_frame* to do anything. The five bit *ball\_number\_hold* is used to store the *bram\_addr\_b* signal before it is passed onto *ball\_number* to pipeline the process since it takes a clock cycle to retrieve the data and another cycle to do the logic on it. A *write\_request\_hold* register is used for the same reason.

Within the procedural block a number of if statement may be evaluated. If reset it high *stop\_calc*, *bram\_addr\_b*, *write\_request* and *ball\_number* are all set to zero since the system is going to be reset and old values in the BRAM don't matter so we'll wait until they've been rewritten during the reset frame before giving the Output module anything to display. The system will wait until it receives a *done\_calc* from the Physics module before doing anything. Else if the reset isn't high if *stop\_calc* is high the system is in a waiting state for new frame. The *stop\_calc* signal is set back to zero if *new\_frame* is high otherwise it takes on its old value. The same happens for *bram\_addr\_b* and *ball\_number*. The *write request* is set to zero. Else if neither reset or stop calc then if *done calc* is high (signaling the Physics module is completed with calculations and writing into memory for the frame) the following happens: *bram\_addr\_b* is incremented, *stop\_calc* is set to one if *ball\_number* equals 31 (which means all 31 balls have been processed and their data sent on) otherwise it stays zero, *write\_request\_hold* is set to 0 if *ball\_number* equals 30 (which means all 31 balls will have been processed and their data sent on...not 32 balls due to pipelining) otherwise one, write\_request is assigned to write request hold, ball pos out is assigned to the appended bits 47-32 and 63-48 from *info\_from\_bram* (where the x and y positions are stored respectively), *display\_enb* is set to zero if *ball\_number* equals 31 otherwise it is set to the logical value of bits 69 and not 68 or 67 from *info\_from\_bram* (in play, in left hand and in right hand bits respectively) and *ball\_number\_hold* is set to *bram\_addr b*.

#### **Output Module**

(by Chris Wilkens)

The fourth major block of the implementation is the output module. This module sits in the path of the outgoing VGA signal and overlays the hands and balls. In our implementation, this is accomplished by instantiating a sprite for each object to be displayed. For the two hands, we instantiate two separate directly within the output module and connect them to the position signals from the video processor. However, the situation is slightly more complicated for the 32 balls. From the output module's perspective, these are implemented using a single "aggregate sprite" that can be queried for a pixel location and returns the color based on the location of all 32 balls in the system. This requires a set of connections resembling a memory, which are received from the ball manager's display module and passed directly through to the aggregate ball sprite module.

This diagram shows the structure of the output module.

#### Aggregate Ball Sprite Memory

The ball sprite memory module acts like a memory for the 32 output ball sprites. From the perspective of the output module, it behaves like a single sprite that can be queried for a pixel value. However, it also has a set of "memory" signals that can be used to configure the output. The ball manager uses these signals to sequentially set the positions of the 32 balls. On a given cycle, the ball manager can supply a write enable, a ball number (similar to a memory address,) the position in which the specified ball is to be displayed (similar to memory data,) and whether or not the specified ball is actually to appear on the screen (more memory data.) This information is stored internally such that when the output module queries for a certain location on the screen, the sprite memory can check each ball simultaneously to determine whether or not it claims the given pixel.

We implemented this module as an array of sprite modules. The connections to these sprite modules are large arrays of registers that hold the position and enable signals for the balls. On cycles when the write enable bit is high, this module stores the position and enable signals in the registers for the appropriate ball number. As a consequence, the position of that sprite is updated, such that when a pixel request comes, the module can simply OR the outputs of each of its 32 sprites, allowing the output module to see it as one sprite.

# Testing

Our testing strategy for the project consisted of three facets: independent testing of the video modules in hardware, independent testing of the ball manager in simulation, and combined testing of the modules in hardware. For the video modules, we incrementally tested them in hardware because simulation, in general, would be prohibitively difficult. The first step was to demonstrate that we could buffer and display the proper video. Because we were originally using an older module provided by the staff, this process took time. We did not reach our final design until the staff released a new module that buffered video to the ZBT instead of to the BRAM. At this point, what was supposed to be a simple set of modifications to the existing verilog were confounded by what appeared to be issues computing the address. Once these were fixed, however, the video was ready to go.

The next step, though it was started concurrently with testing video input, was to develop the hand detector module that located the hands on the screen. For this, we first tested thresholds for detecting flesh colored pixels. By connecting our thresholds to the switches of the labkit and coloring the selected pixels red, we were able to tweak the parameters and determine good limits for the Y and Cr channels of the input. With the critical pixels selected, it remained to compute the appropriate centers of mass. This was implemented and debugged by connecting the positions of the hands to sprites in order to display them in the video. This process was marginally complicated because the calculations required many clock cycles, but seemed simple enough. However, it proved to be our first major but silly snag. For some inexplicable reason, the positions were not changing, and it wasn't clear why. Simulation testing revealed that the hand detector worked according to specification, so it was unclear why things appeared to break on synthesis. After an exorbitantly large amount of debugging, it was discovered that the clock signal being passed to the hand detector was not in fact a valid signal at all and that the synthesizer had missed it. Once that was fixed, the module worked as promised.

With the position information, it was necessary to compute the hand logic values. Our first attempt was to compute the velocity of the hand by taking the difference with the last data point. This, however, proved to be a torturous task, as early attempts to subtract the two positions simply yielded zero velocities. After days of debugging, it was finally determined that the source of the error was the *pos\_ready* signal. This signal was only supposed to be high for one clock cycle per frame in order to notify the hand logic module to calculate the velocities. Instead, the signal was high for many clock cycles, effectively erasing the memory of the logic calculator. Unfortunately, this took days of debugging to discover. Again, once it was discovered, everything ran smoothly. We then proceeded to hook the throw and catch signals up to simple logic for testing purposes. We also modified the video processor to tint the screen whenever a throw or a catch was detected. This was an extremely simple modification that allowed us to clearly visualize and tune the hand logic. Using this method, we iterated on the original, simple logic to produce more complicated throw and catch algorithms.

Concurrent with development of the video processor was development of the output module. The first stage of testing was to simply wire the hand sprites to the positions generated by the video processor. However, the ball sprites remained untested. For this, we created a test jig that cycled through each ball and modified it for each frame. This allowed us to test the sprite "memory" aspect of the module independent of the ball manager. With this testing complete, the video processor and output modules were ready for integration.

While Chris was developing the video input an output, I (David Rush) was developing the ball manager. The biggest thing I learned during the creation of the juggling simulator is that small modules are much better. Building a big system and trying to test it is a disaster because many things are likely to be wrong. Basic functionality should first be established with each small component before more complexity should be added. The basic inputs should be tested first and only once they are working should more complex inputs be added. I made the mistake of writing a huge Physics module and had no way but to enter a combination of inputs into the simulator and check to see that nothing came out. I ended up wiring every signal I had to an output to check that any of them were correct and try to figure out where along the chain there was a problem. I iterated this process dozens of times because there were dozens of mistakes that were made. Velocities were wired to position outputs, mot all the outputs were assigned in the right places, wires were missing or mismatched, some code didn't do what I thought and many times my timing was off by a clock cycle. After many, many iterations of trying to simulate the Physics module and getting a little more correct each time after hours of debugging I learned that small was better and each of the subsequent modules I wrote were much smaller and easier to debug.

For each of the modules within the Ball Manager testing in simulation was the easiest way to initially see if the desired results were had. The level to pulse module was easiest and it can be seen in it's graph that level signals were put in and pulses came out.

The Controller was similar in that it had a limited number of inputs and the expected outputs could easily be checked against the actual outputs. If the outputs weren't all synchronized it wasn't working right.

Within the display module I (David) found in simulation that my ball addresses weren't matching up with the right data and after drawing out the timing diagrams I realized I needed a two clock cycle delay between sending the input address and having the valid data to give to the output module. I pipelined the process by buffering the ball number and write enable and that way each ball only took one clock cycle even if the first ball data didn't come out for 3 cycles.

After testing in simulation I visually tested the Ball Manager since looking at 32 bits worth of position data can't very well tell you if the ball is being displayed at the right position after many seconds since the frame updates 60 times per second. At first it was noticed that all the balls were in the upper left of the screen and moving only a little bit. After checking the position calculations I noticed that I had wired the output position bits to the velocity which was always much smaller. It was later noticed that one ball was always displayed and never moved and that was due to an off by one error in the display module. The balls were also very jittery at one point and it was found to be because one signal wasn't set for an entire frame when it should have been.

After 100 hours of work there were many more errors and bugs that were worked through and in the end though the system worked. This is just a highlight of some of the more interesting errors.

## Conclusion

Overall, this project provided an excellent demonstration of the principles of system design, including modularity and simplicity. In the end, the project worked fairly well. Though it couldn't truly simulate the experience of juggling real balls, it could reliably simulate simple juggling moves. Moreover, when configured properly, it was simple enough that even those who couldn't juggle in real life could juggle in the simulator. The net result was a pleasantly functional system.

One of the most prominent design principles in the project was the supremacy of simplicity in system design. For example, our method of hand detection was hardly revolutionary, and calculating the center of mass of the pixels on each side of the screen was very straightforward. However, despite the lack of complexity, this method of hand detection was extremely reliable when the proper precautions were taken. Another simple yet innovative idea was displaying the hand logic by tinting the screen. The implementation was simple – only one line of verilog code was modified – but it allowed the untrained user to gain a much better understanding of the system's interpretation of his or her movements. It also greatly facilitated debugging, as it provided insight into what the system was "thinking." Yet another innovation of simplicity was the idea to allow the user to fix the release velocities of the balls when they are thrown. While this may significantly detract from the usefulness of the simulator for an experienced user, it greatly enhances playability for novices and allows them to become acclimated to the system before enabling the more complex mode.

While the simulator performs fairly well, there are a number of things that could be changed. If one were to rebuild the system from scratch, the system should be better modularized, particularly the ball manager. Also, as with any similar system, there are an infinite number of ways to tweak the video processing that could potentially improve the project's operation. In addition to enhancements to the existing foundation, there are many small additions that could be made. For instance, there were many corner cases that we largely ignored, such as balls on the floor and balls flying above the ceiling. The graphics used in the simulation were also fairly basic and could certainly use improvement. Overall, however, the project was successful. None of its shortcomings dramatically affected its functionality, and it was an enjoyable project to build and use.

# Appendix: Verilog Source

This appendix contains the verilog source for our modules. The modules described above are in files as follows:

| System Block    | Associated Files     |

|-----------------|----------------------|

| General Modules | Labkit.v             |

|                 | Debounce.v           |

|                 | Display_16hex.v      |

|                 | Virtual_juggling.v   |

| Camera Input    | Ntsc2zbt.v           |

|                 | Video_decoder.v      |

|                 | Video_zbt.v          |

|                 | 6111zbt.v            |

| Controller      | Vj_controller.v      |

|                 | Vj_level_to_pulse.v  |

| Video Processor | Vj_video_processor.v |

|                 | Divide.v             |

|                 | Yuv_to_rgb.v         |

| Ball Manager    | Vj_ball_manager.v    |

|                 | Vj_bm_physics.v      |

|                 | Vj_bm_display.v      |

|                 | Bram70x32.v          |

| Output          | Vj_output.v          |

```

//

// File: zbt_6111_sample.v

// Date: 26-Nov-05

// Author: I. Chuang <ichuang@mit.edu>

// Sample code for the MIT 6.111 labkit demonstrating use of the ZBT

// memories for video display. Video input from the NTSC digitizer is

// displayed within an XGA 1024x768 window. One ZBT memory (ram0) is used

// as the video frame buffer, with 8 bits used per pixel (black & white).

//

// Since the ZBT is read once for every four pixels, this frees up time for

// data to be stored to the ZBT during other pixel times. The NTSC decoder

// runs at 27 MHz, whereas the XGA runs at 65 MHz, so we synchronize

// signals between the two (see ntsc2zbt.v) and let the NTSC data be

// stored to ZBT memory whenever it is available, during cycles when

// pixel reads are not being performed.

//

// We use a very simple ZBT interface, which does not involve any clock

// generation or hiding of the pipelining. See zbt_6111.v for more info.

// switch[7] selects between display of NTSC video and test bars

// switch[6] is used for testing the NTSC decoder

// switch[1] selects between test bar periods; these are stored to ZBT

during blanking periods

//

// switch[0] selects vertical test bars (hardwired; not stored in ZBT)

```

file:///C//Documents%20and%20Settings/cwilkens/My%20Documents/Colle...1%20Project/Verilog%20Files/Verilog%20Source%20as%20Text/labkit.txt

// 2) Expanded "tv\_in\_ycrcb" to 20 bits.

- // 3) Renamed "tv\_out\_data" to "tv\_out\_i2c\_data" and "tv\_out\_sclk" to

- // "tv\_out\_i2c\_clock".

- // 4) Reversed disp\_data\_in and disp\_data\_out signals, so that "out" is an

- // output of the FPGA, and "in" is an input.

- //

- // CHANGES FOR BOARD REVISION 003

- //

- // 1) Combined flash chip enables into a single signal, flash\_ce\_b.

```

// CHANGES FOR BOARD REVISION 002

```

- //

- // 1) Added SRAM clock feedback path input and output

// Complete change history (including bug fixes)

- // 2) Renamed "mousedata" to "mouse\_data"

- // 3) Renamed some ZBT memory signals. Parity bits are now incorporated into

- // the data bus, and the byte write enables have been combined into the

// 2005-Sep-09: Added missing default assignments to "ac97\_sdata\_out",

// 2005-Jan-23: Reduced flash address bus to 24 bits, to match 128Mb devices

actually populated on the boards. (The boards support up to

// 2004-May-01: Changed "disp\_data\_in" to be an output, and gave it a default

// value. (Previous versions of this file declared this port to

// 2004-Apr-29: Reduced SRAM address busses to 19 bits, to match 18Mb devices

actually populated on the boards. (The boards support up to

"disp\_data\_out", "analyzer[2-3]\_clock" and

256Mb devices, with 25 address lines.)

72Mb devices, with 21 address lines.)

// 2004-Oct-31: Adapted to new revision 004 board.

- // 4-bit ram#\_bwe\_b bus.

- // 4) Removed the "systemace\_clock" net, since the SystemACE clock is now

- // hardwired on the PCB to the oscillator.

"analyzer[2-3]\_data".

be an input.)

// 2004-Apr-29: Change history started

//

//

//

|| ||

//

//

//

//

|| ||

//

//

//

//

file:///Cl/Documents%20and%20Settings/cwilkens/My%20D...rilog%20Files/Verilog%20Source%20as%20Text/labkit.txt (2 of 13)12/13/2005 6:59:23 PM

module labkit(beep, audio\_reset\_b,

ac97\_sdata\_out, ac97\_sdata\_in, ac97\_synch, ac97\_bit\_clock,

vga\_out\_red, vga\_out\_green, vga\_out\_blue, vga\_out\_sync\_b, vga\_out\_blank\_b, vga\_out\_pixel\_clock, vga\_out\_hsync, vga\_out\_vsync,

tv\_out\_ycrcb, tv\_out\_reset\_b, tv\_out\_clock, tv\_out\_i2c\_clock, tv\_out\_i2c\_data, tv\_out\_pal\_ntsc, tv\_out\_hsync\_b, tv\_out\_vsync\_b, tv\_out\_blank\_b, tv\_out\_subcar\_reset,

tv\_in\_ycrcb, tv\_in\_data\_valid, tv\_in\_line\_clock1, tv\_in\_line\_clock2, tv\_in\_aef, tv\_in\_hff, tv\_in\_aff, tv\_in\_i2c\_clock, tv\_in\_i2c\_data, tv\_in\_fifo\_read, tv\_in\_fifo\_clock, tv\_in\_iso, tv\_in\_reset\_b, tv\_in\_clock,

ram0\_data, ram0\_address, ram0\_adv\_ld, ram0\_clk, ram0\_cen\_b, ram0\_ce\_b, ram0\_oe\_b, ram0\_we\_b, ram0\_bwe\_b,

ram1\_data, ram1\_address, ram1\_adv\_ld, ram1\_clk, ram1\_ce\_b, ram1\_ce\_b, ram1\_oe\_b, ram1\_we\_b, ram1\_bwe\_b,

clock\_feedback\_out, clock\_feedback\_in,

flash\_data, flash\_address, flash\_ce\_b, flash\_oe\_b, flash\_we\_b, flash\_reset\_b, flash\_sts, flash\_byte\_b,

rs232\_txd, rs232\_rxd, rs232\_rts, rs232\_cts,

mouse\_clock, mouse\_data, keyboard\_clock, keyboard\_data,

clock\_27mhz, clock1, clock2,

disp\_blank, disp\_data\_out, disp\_clock, disp\_rs, disp\_ce\_b, disp\_reset\_b, disp\_data\_in,

button0, button1, button2, button3, button\_enter, button\_right, button\_left, button\_down, button\_up, file:///Cl/Documents%20and%20Settings/cwilkens/My%20Documents/Colle...l%20Project/Verilog%20Files/Verilog%20Source%20as%20Text/labkit.txt

switch,

led,

user1, user2, user3, user4,

daughtercard,

```

systemace_data, systemace_address, systemace_ce_b,

systemace_we_b, systemace_oe_b, systemace_irq, systemace_mpbrdy,

```

analyzer1\_data, analyzer1\_clock, analyzer2\_data, analyzer2\_clock, analyzer3\_data, analyzer3\_clock, analyzer4\_data, analyzer4\_clock);

```

output beep, audio_reset_b, ac97_synch, ac97_sdata_out; input ac97_bit_clock, ac97_sdata_in;

```

```

output [7:0] vga_out_red, vga_out_green, vga_out_blue;

output vga_out_sync_b, vga_out_blank_b, vga_out_pixel_clock,

vga_out_hsync, vga_out_vsync;

```

```

output [9:0] tv_out_ycrcb;

output tv_out_reset_b, tv_out_clock, tv_out_i2c_clock, tv_out_i2c_data,

tv_out_pal_ntsc, tv_out_hsync_b, tv_out_vsync_b, tv_out_blank_b,

tv_out_subcar_reset;

```

```

input [19:0] tv_in_ycrcb;

input tv_in_data_valid, tv_in_line_clock1, tv_in_line_clock2, tv_in_aef,

tv_in_hff, tv_in_aff;

output tv_in_i2c_clock, tv_in_fifo_read, tv_in_fifo_clock, tv_in_iso,

tv_in_reset_b, tv_in_clock;

inout tv_in_i2c_data;

```

inout [35:0] ram0\_data; output [18:0] ram0\_address; output ram0\_adv\_ld, ram0\_clk, ram0\_cen\_b, ram0\_ce\_b, ram0\_oe\_b, ram0\_we\_b; output [3:0] ram0\_bwe\_b;

inout [35:0] ram1\_data; output [18:0] ram1\_address; output ram1\_adv\_ld, ram1\_clk, ram1\_ce\_b, ram1\_ce\_b, ram1\_oe\_b, ram1\_we\_b; output [3:0] ram1\_bwe\_b;

input clock\_feedback\_in; output clock\_feedback\_out;

inout [15:0] flash\_data; output [23:0] flash\_address; output flash\_ce\_b, flash\_oe\_b, flash\_we\_b, flash\_reset\_b, flash\_byte\_b; input flash\_sts;

output rs232\_txd, rs232\_rts; input rs232\_rxd, rs232\_cts;

input mouse\_clock, mouse\_data, keyboard\_clock, keyboard\_data;

input clock\_27mhz, clock1, clock2;

output disp\_blank, disp\_clock, disp\_rs, disp\_ce\_b, disp\_reset\_b; input disp\_data\_in; output disp\_data\_out;

input button0, button1, button2, button3, button\_enter, button\_right, button\_left, button\_down, button\_up; input [7:0] switch; output [7:0] led;

inout [31:0] user1, user2, user3, user4;

inout [43:0] daughtercard;

inout [15:0] systemace\_data; output [6:0] systemace\_address; output systemace\_ce\_b, systemace\_we\_b, systemace\_oe\_b; input systemace\_irq, systemace\_mpbrdy;

output [15:0] analyzer1\_data, analyzer2\_data, analyzer3\_data, analyzer4\_data; output analyzer1\_clock, analyzer2\_clock, analyzer3\_clock, analyzer4\_clock;

```

// Audio Input and Output

assign beep= 1'b0;

assign audio_reset_b = 1'b0;

assign ac97_synch = 1'b0;

assign ac97_sdata_out = 1'b0;

/*

```

\*/

```

// ac97_sdata_in is an input

```

```

// Video Output

assign tv_out_ycrcb = 10'h0;

assign tv_out_reset_b = 1'b0;

assign tv_out_clock = 1'b0;

assign tv_out_i2c_clock = 1'b0;

assign tv_out_i2c_data = 1'b0;

assign tv_out_pal_ntsc = 1'b0;

assign tv_out_hsync_b = 1'b1;

assign tv_out_blank_b = 1'b1;

assign tv_out_subcar_reset = 1'b0;

```

```

// Video Input

//assign tv_in_i2c_clock = 1'b0;

assign tv_in_fifo_read = 1'b1;

assign tv_in_fifo_clock = 1'b0;

assign tv_in_iso = 1'b1;

//assign tv_in_reset_b = 1'b0;

assign tv_in_clock = clock_27mhz;//1'b0;

//assign tv_in_i2c_data = 1'bZ;

// tv_in_ycrcb, tv_in_data_valid, tv_in_line_clock1, tv_in_line_clock2,

// tv_in_aef, tv_in_hff, and tv_in_aff are inputs

```

// SRAMs

/\* change lines below to enable ZBT RAM bank0 \*/

/\* assign ram0\_data = 36'hZ; assign ram0\_address = 19'h0; assign ram0\_clk = 1'b0; assign ram0\_we\_b = 1'b1; file:///Cl/Documents%20and%20Settings/cwilkens/My%20Documents/Colle...l%20Project/Verilog%20Files/Verilog%20Source%20as%20Text/labkit.txt

```

assign ram0_cen_b = 1'b0; // clock enable */

```

```

/* enable RAM pins */

```

```

assign ram0_ce_b = 1'b0;

assign ram0_oe_b = 1'b0;

assign ram0_adv_ld = 1'b0;

assign ram0_bwe_b = 4'h0;

```

/\*\*\*\*\*\*\*\*/

```

assign ram1_data = 36'hZ;

assign ram1_address = 19'h0;

assign ram1_adv_ld = 1'b0;

assign ram1_clk = 1'b0;

assign ram1_ce_b = 1'b1;

assign ram1_ce_b = 1'b1;

assign ram1_oe_b = 1'b1;

assign ram1_we_b = 1'b1;

assign ram1_bwe_b = 4'hF;

```

```

assign clock_feedback_out = 1'b0;

// clock_feedback_in is an input

```

```

// Flash ROM

assign flash_data = 16'hZ;

assign flash_address = 24'h0;

assign flash_ce_b = 1'b1;

assign flash_oe_b = 1'b1;

assign flash_we_b = 1'b1;

assign flash_reset_b = 1'b0;

assign flash_byte_b = 1'b1;

// flash_sts is an input

```

```

// RS-232 Interface

assign rs232_txd = 1'b1;

assign rs232_rts = 1'b1;

// rs232_rxd and rs232_cts are inputs

```

# // PS/2 Ports // mouse\_clock, mouse\_data, keyboard\_clock, and keyboard\_data are inputs

```

// LED Displays

/*

assign disp_blank = 1'b1;

assign disp_clock = 1'b0;

assign disp_rs = 1'b0;

assign disp_ce_b = 1'b1;

assign disp_reset_b = 1'b0;

assign disp_data_out = 1'b0;

*/

// disp_data_in is an input

// Buttons, Switches, and Individual LEDs

//lab3 assign led = 8'hFF;

// button0, button1, button2, button3, button_enter, button_right,

// button_left, button_down, button_up, and switches are inputs

// User I/Os

assign user1 = 32'hZ;

assign user2 = 32'hZ;

assign user3 = 32'hZ;

assign user4 = 32'hZ;

// Daughtercard Connectors

assign daughtercard = 44'hZ;

// SystemACE Microprocessor Port

assign systemace_data = 16'hZ;

assign systemace_address = 7'h0;

assign systemace_ce_b = 1'b1;

assign systemace_we_b = 1'b1;

assign systemace_oe_b = 1'b1;

// systemace_irq and systemace_mpbrdy are inputs

// Logic Analyzer

assign analyzer1_data = 16'h0;

assign analyzer1_clock = 1'b1;

assign analyzer2_data = 16'h0;

assign analyzer2_clock = 1'b1;

assign analyzer3_data = 16'h0;

assign analyzer3_clock = 1'b1;

assign analyzer4_data = 16'h0;

assign analyzer4_clock = 1'b1;

```

####

// Demonstration of ZBT RAM as video memory

// use FPGA's digital clock manager to produce a // 65MHz clock (actually 64.8MHz) wire clock\_65mhz\_unbuf,clock\_65mhz; DCM vclk1(.CLKIN(clock\_27mhz),.CLKFX(clock\_65mhz\_unbuf)); // synthesis attribute CLKFX\_DIVIDE of vclk1 is 10 // synthesis attribute CLKFX\_MULTIPLY of vclk1 is 24 // synthesis attribute CLK\_FEEDBACK of vclk1 is NONE // synthesis attribute CLKIN\_PERIOD of vclk1 is 37 BUFG vclk2(.O(clock\_65mhz),.I(clock\_65mhz\_unbuf));

wire  $clk = clock_{65mhz}$ ;

// ENTER button is user reset

wire reset,user\_reset;

debounce db1(power\_on\_reset, clk, ~button\_enter, user\_reset);

assign reset = user\_reset | power\_on\_reset;

#### // DEBOUNCE other signals

wire db\_button\_up, db\_button\_down,db\_button\_right,db\_button\_left; debounce incdb(power\_on\_reset, clock\_65mhz, ~button\_up, db\_button\_up); debounce decdb(power\_on\_reset, clock\_65mhz, ~button\_down, db\_button\_down); debounce butdr(power\_on\_reset, clock\_65mhz, ~button\_right, db\_button\_right); debounce butdl(power\_on\_reset, clock\_65mhz, ~button\_left, db\_button\_left); wire [7:0] db\_switch; file:///Cl/Documents%20and%20Settings/cwilkens/My%20Documents/Colle...l%20Project/Verilog%20Files/Verilog%20Source%20as%20Text/labkit.txt

debounce switchdb[7:0](power\_on\_reset, clk, switch, db\_switch); wire db\_button0, db\_button1, db\_button2, db\_button3; debounce b0db(power\_on\_reset, clock\_65mhz, ~button0, db\_button0); debounce b1db(power\_on\_reset, clock\_65mhz, ~button1, db\_button1); debounce b2db(power\_on\_reset, clock\_65mhz, ~button2, db\_button2); debounce b3db(power\_on\_reset, clock\_65mhz, ~button3, db\_button3);

// display module for debugging

reg [63:0] dispdata; display\_16hex hexdisp1(reset, clock\_65mhz, dispdata,// was clk disp\_blank, disp\_clock, disp\_rs, disp\_ce\_b, disp\_reset\_b, disp\_data\_out);

// generate basic XVGA video signals

wire [10:0] hcount;

wire [9:0] vcount;

wire hsync,vsync,blank;

xvga xvga1(clk,hcount,vcount,hsync,vsync,blank);

// wire up to ZBT ram

wire [35:0] vram\_write\_data; wire [35:0] vram\_read\_data; wire [18:0] vram\_addr; wire vram\_we;

```

// generate pixel value from reading ZBT memory

wire [17:0] vr_pixel;

wire [18:0] vram_addr1;

```

.tv\_in\_i2c\_clock(tv\_in\_i2c\_clock), .tv\_in\_i2c\_data(tv\_in\_i2c\_data));

wire [29:0] ycrcb; // video data (luminance, chrominance)

wire [2:0] fvh; // sync for field, vertical, horizontal

wire dv; // data valid

```

ntsc_decode decode (.clk(tv_in_line_clock1), .reset(reset),

.tv_in_ycrcb(tv_in_ycrcb[19:10]),

.ycrcb(ycrcb), .f(fvh[2]),

.v(fvh[1]), .h(fvh[0]), .data_valid(dv));

```

// code to write NTSC data to video memory

```

// code to write pattern to ZBT memory

reg [31:0] count;

always @(posedge clk) count <= reset ? 0 : count + 1;</pre>

```

```

wire [18:0] vram_addr2 = count[0+18:0];

wire [35:0] vpat = ( db_button0 ? {4{count[3+3:3],4'b0}}

: {4{count[3+4:4],4'b0}} );

```

// mux selecting read/write to memory based on which write-enable is chosen

```

wire sw_ntsc = ~db_button3;

wire my_we = sw_ntsc ? (hcount[1:0]==2'd2) : blank;

wire [18:0] write_addr = sw_ntsc ? ntsc_addr : vram_addr2;

wire [35:0] write_data = sw_ntsc ? ntsc_data : vpat;

// wire write enable = sw_ntsc ? (my_we & ntsc_we) : my_we;

```

```

// assign vram_addr = write_enable ? write_addr : vram_addr1;

// assign vram_we = write_enable;

```

```

assign vram_addr = my_we ? write_addr : vram_addr1;

```

```

assign vram_we = my_we;

```

```

assign vram_write_data = write_data;

```

file:///Cl/Documents%20and%20Settings/cwilkens/My%20Documents/Colle...l%20Project/Verilog%20Files/Verilog%20Source%20as%20Text/labkit.txt

// select output pixel data

```

reg [17:0] pixel; // pixel[8:4] are the top five bits of Y, pixel[3:0] are the top 4 bits of U wire b,hs,vs;

```

```

delayN dn1(clk,hsync,hs); // delay by 3 cycles to sync with ZBT read

delayN dn2(clk,vsync,vs);

delayN dn3(clk,blank,b);

```

```

always @(posedge clk)

begin

pixel <= db_button0 ? {hcount[8:6],5'b0,hcount[8:6],5'b0,hcount[8:7]} : vr_pixel;

end</pre>

```

```

// VGA Output. In order to meet the setup and hold times of the // AD7125, we send it ~clock_65mhz.

```

```

wire [63:0] hex_debug;

```

```

assign vga_out_pixel_clock = ~clock_65mhz;

```

```

/*assign vga_out_red = pixel;

assign vga_out_green = pixel;

assign vga_out_blue = pixel;

assign vga_out_sync_b = 1'b1; // not used

assign vga_out_pixel_clock = ~clock_65mhz;

assign vga_out_blank_b = ~b;

assign vga_out_hsync = hs;

assign vga_out_vsync = vs;*/

```

```

// debugging

```

```

assign led = ~{vram_addr[18:13],reset,db_button0};

```

always @(posedge clock\_65mhz)// was clk

// dispdata <= {vram\_read\_data,9'b0,vram\_addr};

dispdata <= hex\_debug;//{ntsc\_data,9'b0,ntsc\_addr};</pre>

endmodule

file:///C//Documents%20and%20Settings/cwilkens/My%20Documents/Colleg...ct/Verilog%20Files/Verilog%20Source%20as%20Text/virtual\_juggling.txt

/\*

This module represents the entire VirtualJuggling simulator.

\*/

module virtual\_juggling(clock\_65mhz, reset,

vga\_in\_sync\_b, vga\_in\_blank\_b, y, u, v, vga\_in\_hsync, vga\_in\_vsync, hcount\_in, vcount\_in,

vga\_out\_sync\_b, vga\_out\_blank\_b, vga\_out\_red, vga\_out\_green, vga\_out\_blue, vga\_out\_hsync, vga\_out\_vsync,

ball\_inc,ball\_dec,left\_throw\_button,right\_throw\_button,db\_switch, hex\_display);

input clock\_65mhz; input reset; input vga\_in\_sync\_b, vga\_in\_blank\_b; input [7:0] y, u, v; input vga\_in\_hsync, vga\_in\_vsync; input [10:0] hcount\_in; input [9:0] vcount\_in;

output vga\_out\_sync\_b, vga\_out\_blank\_b; output [7:0] vga\_out\_red, vga\_out\_green, vga\_out\_blue; output vga\_out\_hsync, vga\_out\_vsync;

input ball\_inc,ball\_dec; input left\_throw\_button,right\_throw\_button; input [7:0] db\_switch; output [63:0] hex\_display;

// PASS THROUGH with delay FOR DEBUGGING

/\*reg vga\_out\_sync\_b, vga\_out\_blank\_b;

reg [7:0] vga\_out\_red, vga\_out\_green, vga\_out\_blue;

reg vga\_out\_hsync, vga\_out\_vsync;

always @ (posedge clock\_65mhz) begin vga\_out\_sync\_b <= vga\_in\_sync\_b;</pre>

```

vga_out_blank_b <= vga_in_blank_b;

{vga_out_red,vga_out_green,vga_out_blue} <= {y,u,v};

vga_out_hsync <= vga_in_hsync;

vga_out_vsync <= vga_in_vsync;

end*/

```

// Logic wires

wire new\_frame;

wire [31:0] left\_hand\_pos, right\_hand\_pos;

wire [31:0] left\_hand\_vel, right\_hand\_vel;

wire [1:0] left\_hand\_logic, right\_hand\_logic;

// Intermediate video wires between video processor and output wire vga\_mid\_sync\_b, vga\_mid\_blank\_b; wire [10:0] hcount\_mid; wire [9:0] vcount\_mid; wire [7:0] vga\_mid\_red, vga\_mid\_green, vga\_mid\_blue; wire vga\_mid\_hsync, vga\_mid\_vsync;

// Video processor module

wire [31:0] VP\_DEBUG;

vj\_video\_processor video\_proc(clock\_65mhz,reset,

vga\_in\_sync\_b,vga\_in\_blank\_b,hcount\_in,vcount\_in, vga\_in\_hsync,vga\_in\_vsync, y,u,v,

db\_switch,

vga\_mid\_red,vga\_mid\_green,vga\_mid\_blue, vga\_mid\_sync\_b,vga\_mid\_blank\_b, hcount\_mid,vcount\_mid, vga\_mid\_hsync,vga\_mid\_vsync, new\_frame, left\_hand\_pos,right\_hand\_pos, left\_hand\_vel,right\_hand\_vel, left\_hand\_logic,right\_hand\_logic, VP\_DEBUG,8'b0);

//Signals from ball manager to output module

wire bm\_we,bm\_be;

wire [4:0] bm\_ball\_number;

wire [31:0] bm\_ball\_pos;

wire [7:0] db\_switch; //added for color debugging

$file:///C|/Documents\%20 and\%20 Settings/cwilkens/My\%20 Documents/Colleg...ct/Verilog\%20 Files/Verilog\%20 Source\%20 as\%20 Text/virtual_juggling.txt$

\*/

// Output module

vj\_output outputmodule(clock\_65mhz,reset,

vga\_mid\_red,vga\_mid\_green,vga\_mid\_blue, hcount\_mid,vcount\_mid, vga\_mid\_sync\_b,vga\_mid\_blank\_b,vga\_mid\_hsync,vga\_mid\_vsync, left\_hand\_pos,right\_hand\_pos, bm\_we,bm\_ball\_number,bm\_ball\_pos,bm\_be, vga\_out\_red,vga\_out\_green,vga\_out\_blue, vga\_out\_sync\_b,vga\_out\_blank\_b, vga\_out\_hsync,vga\_out\_vsync);

// DEBUG OUTPUT

| <pre>//assign hex_display = {left_hand_pos,right_hand_pos};</pre>                               |

|-------------------------------------------------------------------------------------------------|

| <pre>//assign hex_display = {new_frame,29'b0,left_hand_logic,30'b0,right_hand_logic};</pre>     |

| <pre>//assign hex_display = {left_hand_vel,VP_DEBUG};</pre>                                     |

| <pre>//assign hex_display = {left_hand_vel,right_hand_vel};</pre>                               |

| <pre>//assign hex_display = {left_hand_pos,TEST_JIG_DEBUG};</pre>                               |

| <pre>//assign hex_display = {20'hABCDE,2'b0,bm_we,bm_be,3'b0,bm_ball_number,bm_ball_pos};</pre> |

//Controller modual instantiation

wire new\_frame\_sync; wire reset\_sync; wire add\_ball\_sync; wire dec\_ball\_sync; wire [7:0] gravity\_sync; wire left\_throw\_sync,right\_throw\_sync;

vj\_controller vj\_control\_instan(.clk(clock\_65mhz),.new\_frame\_raw(new\_frame),.reset\_raw(reset),. add\_ball\_raw(ball\_inc),

$.dec\_ball\_raw(ball\_dec),.left\_throw\_raw(left\_throw\_button),.right\_throw\_raw(right\_throw\_button),$

.gravity\_raw(db\_switch),.new\_frame\_sync(new\_frame\_sync), .reset\_sync(reset\_sync),.add\_ball\_sync(add\_ball\_sync),.dec\_ball\_sync(dec\_ball\_sync), .left\_throw\_sync(left\_throw\_sync),.right\_throw\_sync(right\_throw\_sync), .gravity\_sync(gravity\_sync));

```

// wire [31:0] left_hand_pos, right_hand_pos;

```

- // wire [31:0] left\_hand\_vel, right\_hand\_vel;

- // wire [1:0] left\_hand\_logic, right\_hand\_logic;

```

wire [15:0] l_h_x, l_h_y, r_h_x, r_h_y;

// wire [15:0] l_h_x_vel, l_h_y_vel, r_h_x_vel, r_h_y_vel;

/* wire left_throw, l_h_catch, right_throw, r_h_catch;

assign left_throw =left_hand_logic[1];

assign l_h_catch =left_hand_logic[0];

assign right_throw =right_hand_logic[1];

assign r_h_catch =right_hand_logic[0];

*/

assign 1 h_x = \text{left} \text{ hand} \text{pos}[31:16];

assign l_h_y = left_hand_pos[15:0];

assign r_h_x = right_hand_pos[31:16];

assign r_h_y = right_hand_pos[15:0];

// assign l_h_x_vel = left_hand_vel[31:16];

// assign l_h_y_vel = left_hand_vel[15:0];

// assign r_h_x_vel = right_hand_vel[31:16];

// assign r_h_y_vel = right_hand_vel[15:0];

```

```

wire signed [16:0] control_left_y_vel;

wire signed [16:0] control_right_y_vel;

wire signed [16:0] control_left_x_vel;

assign control_left_y_vel = (17'b1111111100000000 + {1,left_hand_vel[15:0]});

assign control_right_y_vel = (17'b1111111100000000 + {1,right_hand_vel[15:0]});

assign control_left_x_vel = (17'b11111111100000000 + {1,right_hand_vel[15:0]});

assign control_left_x_vel = (17'b11111111100000001 + {1,right_hand_vel[31:16]});

```

vj\_ball\_manager vj\_bm\_instan(.vclock(clock\_65mhz),.reset(reset\_sync),.new\_frame (new\_frame\_sync),.gravity(gravity\_sync),

.add\_ball(add\_ball\_sync),.dec\_ball(dec\_ball\_sync),

$.left\_throw(left\_hand\_logic[1]), //1'b1), // \ (left\_throw\_force|left\_hand\_logic[1]), //1'b1), //1'b1), // \ (left\_throw\_force|left\_hand$

$.l\_h\_catch(left\_hand\_logic[0]), // |left\_hand\_logic[0]),$

.right\_throw(right\_hand\_logic[1]),//1'b1),// (right\_throw\_force)|right\_hand\_logic[1]),

.r\_h\_catch(right\_hand\_logic[0]),//|right\_hand\_logic[0]),

$.l_h_y(l_h_y),.l_h_x(l_h_x),.l_h_y_vel(left_hand_vel[15:0]),//)16'b1111111100000000,// control_left_y_vel[16:1]),$

file:///C//Documents%20and%20Settings/cwilkens/My%20Documents/Colleg...ct/Verilog%20Files/Verilog%20Source%20as%20Text/virtual\_juggling.txt

.r\_h\_y(r\_h\_y),.r\_h\_x(r\_h\_x),.r\_h\_y\_vel(right\_hand\_vel[15:0]),//),16'b1111111100000000// control\_right\_y\_vel[16:1]),

.r\_h\_x\_vel(control\_right\_x\_vel[16:1]),//right\_hand\_vel[31:16]),16'b1111111110000001

.display\_enb(bm\_be),.ball\_pos\_out(bm\_ball\_pos),.ball\_number(bm\_ball\_number),.write\_request (bm\_we));

assign hex\_display = {bm\_ball\_pos,l\_h\_x,3'b000,new\_frame\_sync,3'b000,add\_ball\_sync,3'b000, bm\_be,3'b000,bm\_we};

/\*

vj\_ball\_manager vj\_bm\_instan(.vclock(clock\_65mhz),.reset(reset\_sync),.new\_frame (new\_frame\_sync),.gravity(gravity\_sync),

.add\_ball(add\_ball\_sync),.dec\_ball(dec\_ball\_sync),

.left\_throw(left\_hand\_logic[1]),//1'b1),// (left\_throw\_force|left\_hand\_logic[1]),

.l\_h\_catch(left\_hand\_logic[0]),//|left\_hand\_logic[0]),

.right\_throw(right\_hand\_logic[1]),//1'b1),// (right\_throw\_force)|right\_hand\_logic[1]),

.r\_h\_catch(right\_hand\_logic[0]),//|right\_hand\_logic[0]),

.l\_h\_y(l\_h\_y),.l\_h\_x(l\_h\_x),.l\_h\_y\_vel(left\_hand\_vel[15:0]),//l16'b1111111100000000),

.l\_h\_x\_vel(left\_hand\_vel[31:16]),//16'b000000001111111),

$.r_h_y(r_h_y), .r_h_x(r_h_x), .r_h_y_vel(right_hand_vel[15:0]), //16'b1111111100000000),$

.r\_h\_x\_vel(right\_hand\_vel[31:16]),//16'b1111111111000000),

.display\_enb(bm\_be),.ball\_pos\_out(bm\_ball\_pos),.ball\_number(bm\_ball\_number),.write\_request (bm\_we));

assign hex\_display = {bm\_ball\_pos,l\_h\_x,3'b000,new\_frame\_sync,3'b000,add\_ball\_sync,3'b000, bm\_be,3'b000,bm\_we}; \*/

$file:///C|/Documents\%20 and\%20 Settings/cwilkens/My\%20 Documents/Colle... Verilog\%20 Files/Verilog\%20 Source\%20 as\%20 Text/vj_video_processor.txt$

```

/*

vj_video_processor

```

This is the main video processing module for the juggling simulator. It receives the raw camera image as a VGA stream (with colors in the YUV space instead of RGB) and locates the hands in the frame. It also converts the signal to RGB video so it can be displayed later.

Notes:

1. This module delays the video by one clock cycle.

2. This module displays the camera image in B&W

```

*/

```

```

module vj_video_processor(clock_65mhz,reset,

```

sync\_in,blank\_in,hcount\_in,vcount\_in, hsync\_in,vsync\_in, y,u,v,

db\_switch,

vga\_red,vga\_green,vga\_blue, sync\_out,blank\_out,hcount\_out,vcount\_out, hsync\_out,vsync\_out, new\_frame, left\_pos,right\_pos, left\_vel,right\_vel, left\_logic,right\_logic, DEBUG\_OUT,DEBUG\_SETTINGS);

// VGA signals for incoming video

input clock\_65mhz;

input reset;

input sync\_in,blank\_in;

input [10:0] hcount\_in;

input [9:0] vcount\_in;

input hsync\_in;

input vsync\_in;

// Incoming color signals are 8-bit YUV values, not RGB

input [7:0] y,u,v;

input [7:0] db\_switch;

$file:///C|/Documents\%20 and\%20 Settings/cwilkens/My\%20 Documents/Colle... Verilog\%20 Files/Verilog\%20 Source\%20 as\%20 Text/vj_video_processor.txt/source\%20 as\%20 as\%2$

// The module converts the YUV signal to RGB and outputs // it to these ports, 8 bits per channel output [7:0] vga\_red,vga\_green,vga\_blue; // Since the module must delay the signal, the output // video signal is sent to the following ports output sync\_out,blank\_out; output [10:0] hcount\_out; output [9:0] vcount\_out; output hsync\_out, vsync\_out; // Output signals // new\_frame is raised on the clock cycle when the hand // information for the current frame has been calculated. // This signals the beginning of the space between the // frame and vsync. output new\_frame; // Hand position/velocity signals // bits [31:16] are for x, [15:0] are for y // the low order bit of each value (e.g. 16 or 0) // corresponds to 2^-5 (i.e. each value has 5 fractional bits) output [31:0] left\_pos,right\_pos; output [31:0] left\_vel,right\_vel; // output [1:0] left\_logic,right\_logic;

output [31:0] DEBUG\_OUT; input [7:0] DEBUG\_SETTINGS;

```

reg [31:0] DEBUG_OUT;

```

// We delay the video by one clock cycle in order to calculate hand information.