# 3D Digital Stereoscope

6.111 Final Project

Joshua Monzon

Tony Ng

Steve Zhou

TA: Javier Castro

#### Abstract

The goal of this project is to design and implement a 3-D rendering system that will generate two images from different points of view to create a stereoscopic effect, generating a 3-D illusion. The system takes perspective projections of a 3-D virtual environment, and then renders, shades, and outputs the images onto a monitor. The user can move around the 3-D virtual world and look at different objects while both of the stereoscopic images are being processed and updated simultaneously in real time. The project will be implemented on a Xilinx Field Programmable Gate Array (FPGA) and the 3-D effect will be aided by the use of a stereoscope viewer.

# **Table of Contents**

| INT   | FRODUCTION AND DESIGN OVERVIEW            | 3  |

|-------|-------------------------------------------|----|

| BL(   | OCK DIAGRAM OF OUR PROJECT                | 4  |

| 1. 31 | D TO 2D PROJECTION AND USER INPUT CONTROL | 4  |

| 1. 31 | D TO 2D PROJECTION AND USER INPUT CONTROL | 5  |

| 1     | 1.1. Triangle Memories                    | 5  |

| 1     | 1.2. PERSPECTIVE PROJECTOR                | 5  |

| 1     | 1.3. Position Controller                  | 8  |

| 2. P  | PROJECTOR SHADER MODULE                   | 10 |

| 2     | 2.1. PIXEL EXTRACTOR MODULE               | 11 |

|       | 2.1.1. Submodules                         |    |

| 2     | 2.2. COLOR LUT                            | 14 |

| 2     | 2.3. PIXELEXTRACTORDELAY MODULE           | 14 |

| 2     | 2.4. SHADING MODULE                       | 14 |

| 3.    | READ AND WRITE OF PIXEL INFORMATION       | 16 |

| 3     | 3.1. MEMORY WRITE                         | 16 |

|       | 3.1.1. Buffer Interface Module            |    |

|       | 3.1.2. Submodules                         |    |

|       | 3.1.3. Top Level Labkit Connections       |    |

| 3     | 3.2. MEMORY READ                          | 20 |

|       | 3.2.2. Displayer Module                   | 20 |

|       | 3.2.3. Top Level Connections              |    |

|       | 3.2.4. XVGA Module                        | 22 |

|       | 3.2.5. DelayN Module                      | 22 |

| 3     | 3.3. READ AND WRITE CONTROL               | 22 |

|       | 3.3.1. Buffer Selector Module             | 22 |

| 4.    | 3D WORLD GENERATION                       | 24 |

| 5.    | TESTING AND DEBUGGING                     | 25 |

| COI   | NCLUSION                                  | 27 |

# **Introduction and Design Overview**

Our project is to design a robust and powerful 3D engine that would process a 3D pixel map of a world and convert it to two 2D images which will be displayed on two screens, each viewed by one eye. The purpose of this is to trick the eye into believing that the person is actually in a 3D environment. The reason why this works is because the human left and right eyes see slightly different images. If we can correctly extract these two images and display them to the corresponding eyes then it is possible to trick the brain into believing that it is seeing a 3D object.

This project is very interesting because it adds another flavor to numerous applications of 3D graphics technology. One such application of this is the virtual manipulation of 2 dimensional objects. For example, imagine a 3D paint program. If one can "hold" a 2D paint brush and virtually paint in the computer screen, then he has more fine control of the brush instead of just using a mouse to paint, for example.

3D imaging is a difficult task because it requires a large amount of computational power and time. Therefore, nowadays, most computers have a specific piece of hardware which is dedicated to rendering and displaying graphics. Our project aims to build a similar type of hardware, although more primitive than what is being used nowadays. We would employ the idea of pipelining and parallel processing to render our images into the screen. Ray casting would be used as a method to project our images. This method is used by classical 3D first person shooter games such as Doom and Wolfenstein. We would also use triangles to create all our images.

To make this complex task less daunting, we divided our 3D engine into 3 stages, each group member in charge of one stage. The first stage involves the processing of user interaction signals which enables the user to move around the world. This stage involves the projection of 3D objects to a 2D plane which corresponds to the field of view of the user. This field of view changes as the user moves and calculating this behavior can be very complicated. The outputs of the first stage are the 3 coordinates of the corners of the triangle and the depth associated with each of these corners. The second stage involves the shading of all the triangles that are projected in the screen. The challenge involved in this stage is being able to extract the pixels which form the triangle given 3 coordinate locations, then somehow use only the depth information of the three corners to extrapolate the depth of all the pixels. After this, it needs to use a shading algorithm which in turn uses the depth of the pixels to shade and render the images. The last stage comprises the memory management of these pixels. The complexity lies in the fact that this stage has to access the memory to check if an incoming pixel is located very deep in the world and is being overlapped by previous pixel. Depending on the result, it decides whether to write the incoming data. Dual buffering is employed to make the display smoother. Designing an effective system which controls the writing and displaying of these two buffers is a very tricky task.

To fully coordinate our stages, we used a precise and elaborate feedback communication system very much like the major and minor FSM concept.

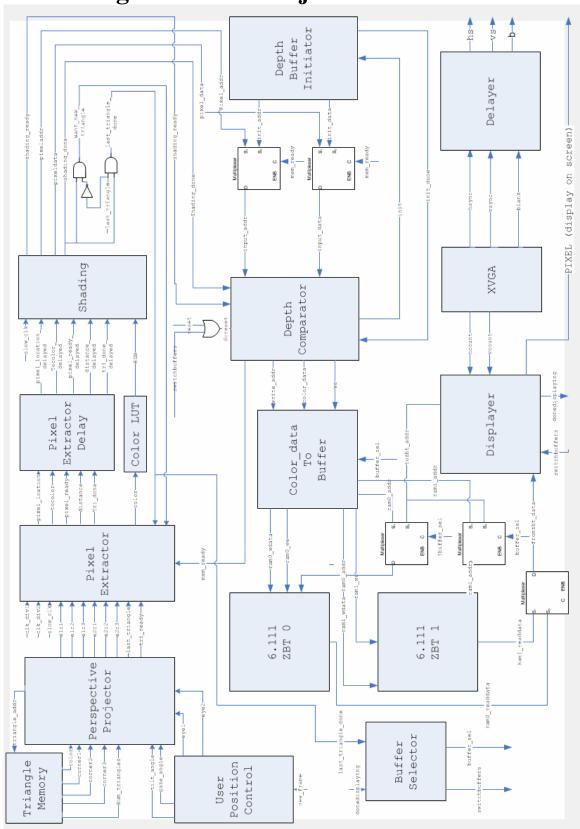

# **Block Diagram of our Project**

# 1. 3D to 2D Projection and User Input Control

# 1.1. Triangle Memories

The triangle memories module is responsible for holding all the information necessary to construct the three dimensional world. The only thing that needs to be stored are triangles, since everything in the three dimensional world is constructed out of triangles. It is inefficient to store all the pixels of the individual triangles, so only an 8-bit color of a triangle and the coordinates of the three corners of the triangle are stored. This contains enough information to reconstruct a triangle perfectly without wasting space on storing extra data. Each corner of a triangle is simply a point in space, so an x, y, and z coordinate needs to be stored. Each x, y, and z coordinate is 12 bits large, so a corner requires 36 bits. So in total, each triangle takes up 116 bits of memory.

The triangle memories are constructed out of BRAMs on the FPGA. Xilinx allows data to be loaded into these BRAMs upon startup, so it is easy to change the contents of the world by loading a different ".coe" file containing different triangle data. The triangle memories module has a signal with the number of triangles stored in it coming out. This signal is used for optimization, because once that number of triangles have been processed, there is no need to look for more triangles because the rest of the memory is empty.

In implementation, the triangle memories made of four pieces of single port block memory. One of the memories contains the color of the triangles. Each of the other three contains the x, y, and z coordinates of one corner. The address inputs of these four blocks of RAM are all wired to the same address input, so each address input will output a specific triangle.

# 1.2. Perspective Projector

The perspective projector is responsible for mapping triangles in three dimensional space onto a two dimensional plane. In the digital stereoscope, the two dimensional plane is the pixels on the monitor. To understand how perspective projection works, let a point in three dimensional space represent the location of an eye. Now place a plane directly in front of the eye in the direction that the eye is looking towards. For each point in every object that is in the three dimensional space, draw a line from that point to the eye. Where the line intersects the plane is where that point would be projected onto. If the plane were represented by a monitor, the point that the line intersects the plane is the pixel that the object should project onto. If the plane is selected such that it represents the eye's field of vision, then lines that do not intersect the plane cannot be seen

Projecting every point of every object in the three dimensional space would be an enormous computational task. It would be impossible to generate images in real time. However, since all objects are constructed out of triangles, it is possible to only project

the three corners of each triangle. The rest of the triangle can be drawn on the two dimensional plane once the projection of the three corners is known.

Even when working with triangles, it is still not easy to draw a line and figure out where it would intersect the plane in front of the eye. There is quite a bit of math involved and it is difficult to do quickly in hardware. Also, considering that there are two eyes at different locations, everything must be processed twice, meaning fast algorithms must be used in order to make movement through the world happen in real time. For further simplification, clipping is ignored. If any corner of a triangle is off the screen, the entire triangle is removed from the screen. This avoids difficult and lengthy calculations required to handle these cases. Many simplifications must be made in order for graphics processing to be done in real time on the FPGA.

The algorithm used in this perspective projector is a ray casting algorithm. A vector is created from an eye to a corner in a triangle. To find out which column of the screen this particular corner belongs on, find the angle between the gaze angle (the direction the eye is looking towards) and the vector on the xy-plane (or the ground). Arctangent can be used to find this angle. If the angle between the gaze and the vector is zero, then the eye is gazing towards the corner, so the corner belongs in the middle column of the screen. By deciding how many radians or degrees are represented by each pixel (in this implementation, each pixel represents 1/160 radians), it is possible to map points onto columns of pixels on the screen. Note that since the height, or z coordinates, is ignored in this calculation, it is impossible to know which row of the screen the point projects onto. In order to figure out the row that the projected point belongs on, a similar calculation can be repeated. By taking distance from the eye to the point on the xy-plane and the difference in height of the eye and the point, arctangent can be used to find this angle, which when compared to the tilt angle in a similar fashion, will determine which row the point should project onto. This algorithm does not exactly project onto a flat plane, because as angles are increased linearly, it sweeps through a round area, not a plane. However, as long as the field of vision is not too large, the algorithm produces a good estimate of where the points belong on a two dimensional plane in front of the eye.

The perspective projector takes as inputs: clk, slow\_clk, corner1, corner2, corner3, inColor, eye1, eye2, gaze\_angle, tilt\_angle, start, num\_triangles, and reset\_last\_triangle. The three corners, the two eyes, gaze angle, and tilt angle are used in the projection calculations, as described above. The normal clock runs fast, which is required for the monitor to function correctly. However, the calculations of arctangent and square root do not always work correctly at speeds this fast, so a slower clock is used to do these calculations. The start signal tells the perspective projector to project the next triangle in memory. The projector also receives the total number of triangles stored in memory, which allows the projector to know that it cannot find more triangles to project after it has completed that many. The reset last triangle signal tells the perspective projector to start projecting all the triangles from the beginning all over again.

As outputs, the perspective projector sends: outColor, triangle\_addr, elc1, elc2, elc3, e2c1, e2c2, e2c3, done, and last\_triangle. The projector sends a triangle

address to the memory to obtain triangle data to perform calculations on. Six points are outputted, three containing information on the projection from the first eye and three containing data from the second eye. This information includes the two dimensional x and y coordinates of the project and the depth of the point. Depth is important in determining what objects should appear in front and what objects should appear in back when multiple objects project to the same area on the screen. The done signal informs other modules that the calculations are done and the projector is ready to do more calculations. The last triangle signal tells other modules that all the triangles in memory have been projected.

The perspective projector contains three small sub-modules. The arctangent estimator sub-module simply takes in the x and y coordinates of two points and then it does the logic necessary to convert the data into a form that the CORDIC algorithm (packaged in Xilinx) can calculate and return the arctangent. The distance finder sub-module takes in two points and applies the distance formula to it, using CORDIC for square root. The angle to screen converter sub-module does some simple math necessary to determine which angles corresponds to which pixels, which is used by the ray casting algorithm described earlier.

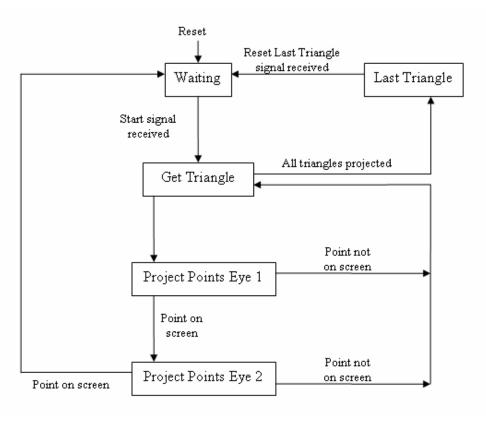

**Figure 1.2.1. FSM Diagram for Perspective Projector.** Controls the functionality of the Perspective Projector

The perspective projector operates as a finite state machine as shown in Figure 1.2.1. Initially, it starts in the waiting state. During this state, when it receives a start signal, the perspective projector requests a triangle from memory and then attempts to project that triangle to the screen from the point of view of the first eye. If the corners are not on

screen, the triangle is thrown out and the perspective projector tries to get a new triangle. If the triangle projects onto the screen, then the projector tries to project the triangle with the second eye. If the triangle is off the screen, then the triangle is thrown out and the projector tries to obtain a new triangle. If the point is on the screen, the perspective projector signals that it is done calculating and that the output data contains valid triangles on the screen and enters the waiting state to allow other modules to use the data. If the perspective projector tries to get a triangle but it has already projected all the triangles in memory, then it enters a last triangle state. In this state, the projector signals other modules that the last triangle has been processed and then enters the wait state. This signal is important because when all the other modules finish using the data, then a frame has just been completely processed.

Testing the perspective projector is difficult because it is a very large module and some things are not very obvious through just observing the outputs, such as whether the projection looks realistic. The signals can be tested through a test bench and by the logic analyzer to make sure they operate correctly. The best way to test whether the projects look nice is to set up the projector so it actually outputs to a monitor and then move around the world to make sure that the three corners of the triangle project correctly.

#### 1.3. Position Controller

The user position controller is responsible for controlling how the user moves around the world. It takes as input the keyboard data and keyboard clock pins from the lab kit. Upon reset, the position controller assigns the user an initial starting position, gaze, and tilt angles. Now in response to the user's inputs, the position controller generates new coordinates for the location of the eyes and the new gaze and tilt angles.

The user's position can be represented by one point. However, one of the eyes should be to the left of this point and the other eye should be to the right. When the user decides to walk around the world, both eyes should follow the movement. Also, when the user turns, the eyes should rotate while keeping the distance between the two eyes the same. This behavior of the eyes is created by constantly updating the location of the eyes based on a small lookup table that calculates sine and cosine values of the gaze angle. At every clock cycle, the two eyes are moved next to the user's position, a point, and placed perpendicular to the gaze angle.

When a user wants to move forward, he probably wants to move towards what he is starting at, or towards the gaze angle. Sine and cosine values are needed to move at specific angles, but fortunately the eyes use sine and cosine of the gaze angle too, so this can be reused. Also, the sine and cosine table does not have to be too accurate as the screen is made of pixels and the world is divided into integer coordinates, so there has to be quite a bit of estimation involved anyways.

One of the sub-modules of the position controller is the keyboard controller. The keyboard controller maps ASCII values from the keyboard into moments. Also, the keyboard controller is responsible for decided when to allow a move. The user should not

be allowed to move unless a frame has finished processing. Otherwise, while some objects are being projected onto the screen, the eyes can move and half one an object may be projected somewhere else. They keyboard controller samples the latest input since the last new frame and uses that as the user's input. Finally, the keyboard controller maps what keys do what actions. Copying the usual keys used by most first person shooter video games, the user controls are summarized in the following table:

#### User Actions and Associated Keystrokes

| Action        | Keyboard input |

|---------------|----------------|

| Move Forward  | W              |

| Move Backward | S              |

| Move Left     | A              |

| Move Right    | D              |

| Turn Left     | Q              |

| Turn Right    | Е              |

| Look Up       | R              |

| Look Down     | F              |

There are two more sub-modules in the position controller, provided courtesy of Professor Terman and Professor Chuang. The first of these is the PS/2 ASCII input module. This module maps all the keyboard inputs into ASCII values. Within this module is the second sub-module, the PS/2 driver. The PS/2 driver reads a stream of one bit data from the PS/2 port and combines the bits into data that can be used by other modules.

Testing the user position controller is difficult to do in simulations because it involves physical keyboard inputs. So, to test all the modules, the lab kit was programmed to display the two eyes on the screen. The screen serves as the x and y coordinates, or the ground, of the world. So when the user moves around, it is easy to see how the eyes move and it is easy to check whether the user is moving in the right direction. Other information such as gaze and tilt angles can be read using the logic analyzer or simply displayed on LEDs on the lab kit.

# 2. Projector Shader Module

The projector shader module acts as a "black box" that encapsulates three major submodules. The purpose of this module is to wire up these three different submodules correctly and, latch the output data from the shading module, and correctly determine the value for want\_new\_triangle and last\_triangle\_shading\_done control signals. The purpose of this module was to process the corner locations of a triangle for both eyes, and output a sequence of pixel addresses and its corresponding data to the ZBT so it can be written to the buffers. In addition, shading\_ready signal must be high for 3 clock cycles before the first valid set of pixel address and data, and shading\_done must be high for 3 clock cycles after the last set of pixels for a triangle. The exact details of how this was made to work will be discussed in the pixel extractor, pixel delay, color LUT, and shading modules, and a couple of additional output signals are discussed below.

Want\_new\_triangle signal is passed to the perspective projector module, and acts as a control signal to inform that module to begin its computations for a new triangle. This signal is only high when shading\_ready is high from the shading module, which means that the rendering of the current triangle has been completed, and the last\_triangle signal is low. If the last\_triangle is high, it means that our system has just completed rendering the last triangle, and the buffer needs to be switched and cleared. Thus, we do not need to wait until the memory of the new buffer is ready to be written to before asking the perspective projector for a new triangle.

Last\_triangle\_shading\_done is used to inform the buffer interface module that the shading of the last triangle has been finished. This means that all of our triangles in our world have been processed, and their information stored in one the ZBTs, and a switch of the ZBTs is required. This signal is held high for three clock cycles at which point shading\_done is high and last\_triangle is high.

This module was tested first using a testbench followed by probing with a logic analyzer. We set the input to our system up as a FSM, which switches between two states, each state outputting a set of triangle inputs along with their control signals that would have otherwise been provided to me by the perspective projector module. Using this setup, we first made sure that the after a shading\_ready signal is high, data for pixel address and pixel data begins to flow, changing once every three clock cycles. Second, we made sure that the shading done signal was high for three clock cycles after the set of pixel address and data was outputted. Third, we checked to see that the want new triangle signal is set high after the first triangle has been processed, which in turn switched the state of our FSM to output the data for the second triangle. Next, we checked to make sure after all of the pixels of the second triangle has been looped through, and a shading ready signal is want new triangle signal is set to low. and last\_triangle\_shading\_done is set to high. Lastly, we made sure that all the pixel addresses for both eyes of both triangles were looped through by the pixel extractor, and each of those addresses corresponded to the correct pixel data, which includes the pixel's distance and color.

### 2.1. Pixel Extractor Module

The pixel extractor module takes as input mem ready signal from buffer interface, tri ready and last triangle signals from perspective projector, as well as the corner locations of the triangle for each eye. Using this information, it needs to control the outputs of pixel\_ready, tri\_done, tocolor, pixel\_location, and distance signals. This module should have the following behavior. When memory is ready, the pixel location, distance and tocolor signals are not of much concern, since nothing is being written to memory. However, we made sure that pixel\_ready and tri\_done signals are both low, since they should only be high when there are valid pixel address and data between them. When memory transitions to ready, we first set tri done high for 3 clock cycles. Then, we wait for the a tri ready signal to be sent from the perspective projector, and once that signal has been obtained, we start processing the triangle, and output a sequence of pixel addresses with their distance and to color signals. After we are done looping through all of the appropriate pixels in a triangle for both eyes, we fire a tri done signal, which is held high for 3 clock cycles, and then proceed to the state when we wait for the next tri ready signal. All of the logic for this module is done once every 3 clock cycles, since the specification is that we must hold each pixel address, and data valid for 3 clock cycles so the buffer interface module would have enough time to determine how to update the ZBTs.

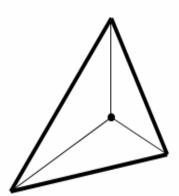

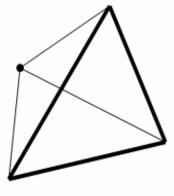

In order to loop through all the appropriate pixels, we first loop through the ones for the triangle seen by the first eye, then loop through the ones for the triangle seen by the second eye. For each eye, we find the minimum and maximum x and y coordinates for the triangle, and loop through all the pixels that has an x value between the min and max x coordinate, and a y value between the min and max y coordinate. The reason why we only loop through these pixel locations is all the other pixels will never be inside the triangle, thus it does not need to be updated. For each of the pixels that we do loop through, we determine if the pixel is inside the triangle or not. To do this, we realized the fact that three lines can be drawn for a pixel location to the locations of the three corners, which would produce three triangles. As seen in the Figure 2.1.1, where the solid lines represent the triangle, and the point represents the pixel in question, we can see that if we

**Figure 2.1.1. Determining if a point is within the triangle or not.** Notice that if a point is in the triangle the sum of the areas of the 3 sub triangles is equal to the area of the bold triangle.

sum up the three areas of the sub triangles made by the pixel and two of the triangle's corners, and that area is equal to the area of the complete triangle, then the pixel must be inside of the triangle. If not, the pixel must be somewhere outside of the triangle. Using this algorithm, we were able to reliably determine whether a point was inside or outside of the triangle

If a point is found to be inside of the triangle, then we would like the pixel to be updated in the buffer, thus we set the tocolor signal to be high. If the point is not inside of the triangle, we set the tocolor signal to be low.

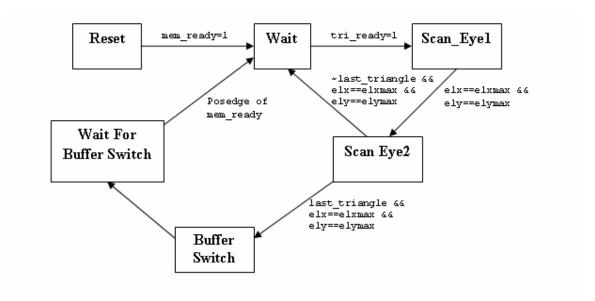

The logic of this process is controlled by a FSM. The transition diagram of the state machine is shown below in Figure 2.1.2:

**Figure 2.1.2. State transition diagram of the pixel extractor FSM.** Regulates the pixel address and pixel data outputs as well as the other control signals

Reset State: When the FSM is in its reset state, it waits for a memory ready signal from the memory informing it that the memory has not been cleared, and is ready for new data. In this state, the outputs of shading ready and done are both zero. When it receives the memory ready signal, the state jumps to the wait state, and triangle done signal is set high which informs the perspective projector module to start work on projecting the next triangle.

Wait State: When the FSM is in its wait state, it knows that the memory is ready. It will stay in this state until a triangle ready signal is high. When the signal is high, which means that the corner locations of the triangle for each eye is valid, the FSM sets the x and y location of the pixel to its minimum values, outputs a tri\_ready signal of 1, and jumps to the scan eye one state.

Scan Eye One State: In this state, the FSM loops through all the pixels with location inside a rectangle that circumscribes the triangle. When it is finished with the last pixel, it jumps to state scan eye 2, and sets the pixel value to the minimum values for eye 2.

Scan Eye Two State: In this state, the FSM loops through all the pixels with location inside a rectangle that circumscribes the triangle for eye 2. When looping is complete, it checks to see if the triangle was the last triangle. If not, it returns to the wait state and fires a tri\_done high signal. If it was the last triangle, it jumps to the buffer switch state.

Buffer Switch State: In this state, the FSM simply fires a tri\_done high signal, and immediately jumps to the wait for buffer switch state.

Wait for Buffer Switch State: This state acts pretty much the same as the reset state. It basically will wait for the memory to be not ready, and then wait until it is ready again before firing a tri\_done high signal, and returning to the wait state.

Testing of the perspective projector was done using the logic analyzer. Once again, we used the FSM input described above, and made sure that the output pixel location is synchronous with the tocolor signal, and the tocolor signal was correct in such a way that pixel locations located outside of the triangle does not have a tocolor signal of 1, and all those pixel locations located inside of the triangle have a tocolor signal of 1. We also checked to make sure that all pixel locations were within a tri\_ready high and a tri\_done high signal.

#### 2.1.1. Submodules

#### Triangle Area Module

The purpose of this module is to calculate twice the area of a triangle, given the (x, y) coordinate of all three of the triangles. This calculation was done by computing the magnitude of the cross product of two vectors, which in effect calculates twice the area of the triangle.

This module was tested using ModelSim testbenches. We tried three coordinates, and arranged them in 6 different combinations and the testbench outputted the correct response for all 6 sets of inputs.

#### Pixel Distance Module

The purpose of this module is to provide distance estimation to the pixel given the area of the three sub triangles and the distance of the three corners. The idea behind our estimation is if a subtriangle's area is large, it means the pixel is located near the corner that is not in the subtriangle. Thus, if we divide the area of the sub triangle by the total area of the triangle, then that ratio should represent how much weight the

distance of the opposite corner will have on the distance of the current pixel. Thus, if we add up all the three rations multiplied by their respective opposite corner distances, then that would give us a rough estimation for the distance of the pixel.

Testing this module was completed through ModelSim testbenches again. We set distance values for each of the three corners, and made up subtriangle areas. We tested it fairly thoroughly with various different values, and the module worked successfully.

### 2.2. Color LUT

The color LUT module converts an eight bit color to a 24 bit RGB value. The eight bit input is divided up into 3 bits for R, 3 bits for G, and 2 bits for B. The smaller the input is for each color component, the smaller the output is, and we tried to keep the relative ratio of the input to its max 2 or 3 bit value and the output to its max 8 bit value to be as similar as possible.

To test this module, we used the 8 switches on the labkit to represent our 8 bit input colors, and viewed the 24 bit color on the screen.

### 2.3. PixelExtractorDelay Module

This module was required because division had a latency of about 30 clock cycles. Thus, in order to match the pixel location with the correct distance values, we had to delay all of the signals coming out of the pixel extractor other than distance by about 30 clock cycles. In order to do so, we used arrays of registers.

We basically tested this module when we tested the Projector\_Shader module as a whole. We made sure that after a shading\_ready signal was high, the next pixel address was correct, and its corresponding data was correct.

# 2.4. Shading Module

This module is the last step in processing and modifying a pixel's attributes. It takes as input the pixel location which is 1 20 bit concatenation of its x and y coordinate, and converts it to the correct pixel address in the ZBT buffers. The correct ZBT address is 640\*y coordinate + x coordinate. It also takes as input the tri\_ready, and tri\_done signals, which it simply latches and passes straight through the module. It also obtains the distance and tocolor signals from the PixelExtractorDelay module, and changes the distance output to max 11 bit number if tocolor signal is low. The reason for this is, if we do not need this pixel colored, it is implied that the pixel is not in the triangle, thus that pixel's address should not be updated to some color in the ZBT.

The way we designed our system is that the person is holding a light source that shines in all directions. Thus, the closer the object is from the eye, the brighter the object gets, and

the further the object is from the eye, the darker the object gets. We set the break point to 1024. If the object is exactly 1024 away from the eye, then the color at that pixel is exactly the color of the triangle that was stored in memory. If the object is closer than 1024, we subtract the 1024 by the distance, and add the top 7 bits of that number to each of the RGB components of the triangle color. Of course, we cap it so that the color can not exceed 8'FF. Similarly, if the object is further than 1024, we subtract that distance by 1024, and subtract each of the RGB components of the triangle color by that number. Again, we cap it so that the minimum value of each color component can't go below 0. Doing so will in effect darken or lighten the object depending on its depth from the viewer.

This module was briefly tested using ModelSim testbenches. We hardwired the inputs to certain values, and observed the behavior at the output. The main thing we wanted to test for here was that the output color seemed correct, such that closer objects are lighter colored, and farther objects are darker colored. We also wanted to make sure that distance was set to 11'h7FF, when the tocolor signal is 0. Other than those two, all of the other output signals were simply latched, and we tested the output behavior of the entire Projector\_Shader module as a whole to ensure their correct behavior.

### 3. Read and Write of Pixel Information

Processed data from the shading module needs to get to the screen somehow. Therefore, our project requires some sort of memory. To efficiently store and display pixel color data, we used a double buffer memory scheme. In this scheme, at any point in time, one of the memory buffers is being refreshed by new pixel information, while the other buffer is being displayed by the screen. Once the buffer that is being refreshed is done refreshing, and if the buffer that displays data on the screen is finished displaying a frame, the buffers switch. This way, the buffer that contains new data is now being displayed on the screen and the old data is now being refreshed.

This process involves three main functions, memory write, memory read and the control and coordination of these two processes.

## 3.1. Memory Write

This section describes how the system stores and handles the processed pixel data.

#### 3.1.1. Buffer Interface Module

The buffer interface module is the heart of the memory write process. It interfaces the shading module with the onboard memory by accepting the pixel information which are processed by the shading module, namely the depth and color of each pixel, and decides whether to store this pixel in the memory or not.

To decide whether to store a pixel in the memory or not, the buffer interface module first checks if the pixel already exists in the memory. One might wonder why the same pixel would be stored twice. Consider the situation, in which there are two overlapping objects in the screen. These two objects have pixels which share the same position. The only difference between them, is that one of these pixels is *deeper* than the other and therefore we do not want to store that pixel anymore because we do not even see it in the screen. Suppose the pixel already exists in the memory, then the existing pixel's depth is compared with the new pixel's depth and whichever pixel is less deep is retained and written to the memory. If the pixel does not exist, we simply store this in memory.

The buffer interface module contains an internal BRAM memory which stores the depth values of the pixels which are being refreshed. It also connects to two onboard SRAM ZBTs to simulate the action of a double buffer.

To test the buffer interface module, the testbench tool using different input values. Tests were run exhaustively ensuring that all possible scenarios were explored. After passing the testbench, we connected the buffer interface module and created a test module which basically stores a green square to the ZBTs and another mini display module which basically displays data from the ZBT. We then compiled this code to the labkit to see if indeed the green square is displayed in the screen. Upon the encounter of bugs, we used

the logic analyzer to debug our code. The final test was to connect this module to the rest of the other modules and ensuring that the correct data is appearing.

#### 3.1.2. Submodules

#### Depth Buffer Module

This module contains the internal memory of the buffer interface module. It consists of two BRAMS connected to each other. Together they form a memory whose entries are 11 bits long and 204800 addresses deep. This module stores the depth value associated with each pixel and is accessed by the depth comparator module to compare the depths incoming pixel data to the depths of previously stored pixel data.

We tested this module using the testbench and ensured that data is properly written and read by the BRAMS.

#### **Buffer Initiator Module**

To be able to store the pixels correctly, the current buffer being written to must be cleared prior to memory write. To do this, we need to initialize the addresses of all the memories used to store pixel information. For this project, the buffer initiator module initializes all the addresses of the ZBT SRAMs (2<sup>19</sup> addresses) to the color black. It also initializes the internal depth buffer BRAM (204800 addresses) to contain the maximum depth (4095).

It takes about 2<sup>19</sup> clock cycles to refresh the memory which is roughly 1/130<sup>th</sup> of a second since we are using a 65 Mhz clock. This design could be further optimized by simply, initializing the first 204800 addresses of the ZBTs since we only use these addresses anyway. However, in an effort to catch unexpected glitches, we decided to clear up the whole ZBT memory every refresh to ensure that if somehow we end up displaying an invalid address (an address greater than 204800), the screen would show the color black.

This module takes in as inputs the signals, <code>clock</code> and <code>init</code>. The clock signal is used to time the flow of the data out of the module. The init signal, on the other hand, is a control signal from the depth comparator module signaling the buffer initiator module to begin initiating the memories. This module sends out the signals <code>pixeldata</code>, <code>pixeladdress</code>, and <code>init\_done</code>. <code>pixeldata</code> is a 35 bit data which is composed of 24 bit black color and 11 bit max address depth. <code>pixeladdress</code> is the address where these data is being written to. This address increments by one each clock cycle during initiation. The <code>init\_done</code> signal is a control signal to inform the depth comparator module that the initiation process is complete.

We simply used testbench to test this module and ensured that the desired behavior is observed.

#### **Depth Comparator Module**

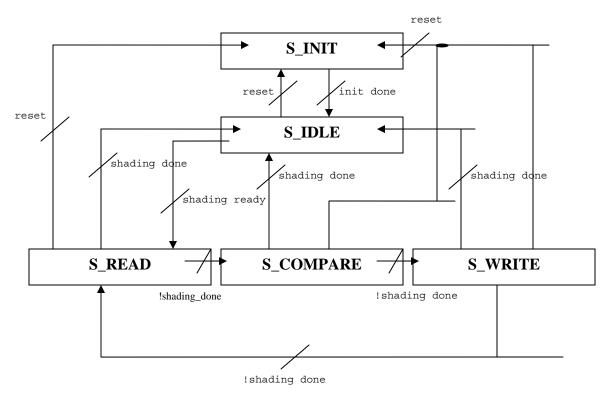

The workhorse of the buffer initiator module, the depth comparator module (DCM) has multiple functions. It acts as a controller to the buffer initiator module, it reads the data coming from the shader module, compare this data by accessing the internal depth buffer, then decide whether to write new incoming data or not. This module is implemented by a 5 state FSM. Refer to Figure 3.1.1 for the FSM state transition diagram.

**Figure 3.1.1.** The depth comparator module FSM state transition diagram. At reset, the depth comparator goes to the initialization state, when initialization is done, it goes to the idle state. Upon receiving a mem\_ready signal it goes to the read, compare, write states loop. This loop comprises the reading of a pixel data, comparing it with the memory, and finally writes the proper data. This loop is interrupted if the shading\_done signal is received, and the depth comparator goes to its idle state.

The DCM's inputs are clock, reset, shading\_ready, shading\_done, init\_done, inputdata and pixeladdr. It's outputs are writeaddr, colordata, we, init, and mem\_ready. The clock signal is used to create a synchronized logic. The reset signal informs the DCM if the system is resetting or if we are switching buffers. If reset is high, the DCM then goes to its init state and sends an init signal to the depth buffer initiator module. The DCM stays in the same state until it receives the init\_done signal from the depth buffer initiator module. Upon receiving this signal, it then goes to its idle state, firing a mem\_ready signal and waiting for the shading ready signal from the shading module.

Interfacing with the shader module can be a bit tricky. The shader module holds the data it sends for 3 clock cycles. Because of this when the DCM receives the shading\_ready signal, it has to delay this ready signal by two clocks to time the state change correctly. After this delay, the DCM enters the read, compare and write state loop. At this loop, it only interacts with a single data from the shader module. At the read state, the DCM accesses the memory element associated with pixeladdr. During the compare state, it compares the depth of the memory element with the depth bits of inputdata. It then decides whether we should write inputdata to memory depending on whether it's deeper or not. Then finally, during the write state, the DCM writes the correct data to the memory or simply leaves the data alone. It keeps on going through this loop for each data passed in, until it receives the shading\_done signal which makes it go to the idle state.

To communicate with the ZBT, the DCM, passes colordata, the 24 bit color signal from inputdata to the colordata\_to\_buffer module for further routing. It also passes writeaddr, the address associated with colordata along with we, the control signal which signifies whether we should write to the ZBT or not.

We tested this module by using both the testbench and logic analyzer to clear the bugs.

#### Colordata to Buffer Module

This module properly routes the pixel address and color data to the correct ZBT. It also assigns the final write enable signals to both ZBTs. Its inputs are clock, reset, buffer\_sel, writeaddr, colordata, and we. Its outputs are ram0\_wdata, ram0\_addr, ram0\_we, ram1\_wdata, ram1\_addr, and ram1\_we.

To route we, colordata and writeaddr to the correct ZBT, this module uses the buffer\_sel signal. The buffer\_sel signal informs the module which buffer is currently being written. For example, if buffer\_sel is equal to 1, then we are writing to ZBT ram 1. Therefore, the colordata to buffer module assigns we, colordata and writeaddr to raml\_we, raml\_wdata, and raml\_addr, respectively. It then assigns the value 0 to the ram 0 pins, namely, ram0\_we, ram0\_wdata, and ram0\_addr since we are not writing to ram 0. If buffer\_sel is equal to 0, it does the opposite thing.

This module was tested using the testbench to see if the desired routing scheme was working.

#### 3.1.3. Top Level Labkit Connections

The color data, address, and write enable signals coming from the buffer interface module get passed to two instances of another ZBT interface module created by one of the staff. This module is called zbt\_6.111. This takes care of the final preparation before the data gets passed to the ZBT. The color data and write enable signals get directly

wired to the zbt\_6.111 modules. The address, however need to pass through a multiplexer since only one type of address needs to be read by each ZBT – either the write address or the read address. The multiplexer is controlled by the buffer select signal.

### 3.2. Memory Read

This section describes how the system reads and displays the pixel data stored in the ZBT memory.

#### 3.2.2. Displayer Module

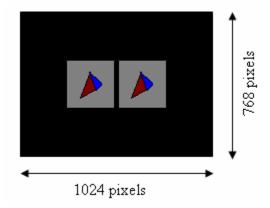

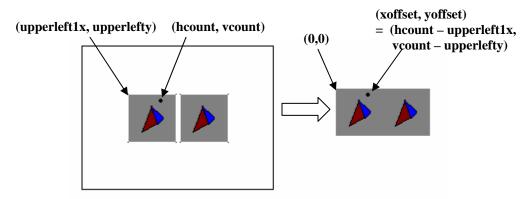

The displayer module controls what appears in the monitor. Takes in vclock, reset, hcount, vcount, and fromzbt\_data as inputs and outputs tozbt\_addr, pixel, and donedisplaying. The hcount and vcount signals inform the displayer module what pixel is currently being refreshed in the screen. The displayer then decides whether the current hcount and vcount signals appear within a set boundary of pixels in which correspond to the viewpoints of the eyes. These boundaries are two 320 by 320 "screens" located in the center of the monitor. Refer to Figure 3.2.1 to see how these two screens are located.

**Figure 3.2.1. Position of the two 320 by 320 screens.** The two screens are the two grey boxes displaying a pyramid. The black rectangle represents the monitor screen.

This module behaves differently depending whether hount and voount are inside these two screens. If hount and voount are not inside these screens or if reset is high, then displayer should be displaying a black screen. In order to this, it assigns tozbt\_addr to a special address in memory which contains the color black. However, if the displayer module is within the two screens, it has to work harder and do more computations to access the correct memory address associated with the given hount and count.

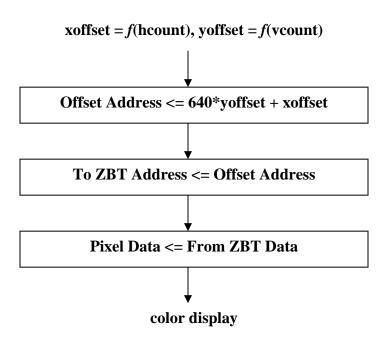

A 3 stage pipeline was used to access the pixel data associated with hount and vount. Figure 3.2.2 shows a schematic of the pipeline used. The first stage involves the computation of the offset address which corresponds to the current hount and vount. The displayer does this by first normalizing the coordinates of hount and vount with respect to the upper leftmost corner of screen one. In effect, the upper leftmost corner

was defined to be 0,0 while hount and vount where defined to be xoffset and yoffset respectively. Figure 3.2.3 shows how xoffset and yoffset are determined. To obtain the offset address we calculate 640\*yoffset + xoffset and we latch this for one clock cycle to avoid glitches. The second stage involves passing this value of offset address to tozbt\_addr which is then sent to the appropriate ZBT to access the color value associated with hount and vount. The third stage involves accessing fromzbt\_data and assign it to the pixel data output. All in all, the total latency time of this pipeline is 5 clock cycles.

**Figure 3.2.2. 3 Stage pipeline of the displayer module.** Takes 5 clock cycles from the time hount and vocunt are generated from the time the corresponding pixel color appears on the screen.

**Figure 3.2.3. Graphical interpretation of xoffset and yoffset.** Left figure shows the absolute position of hount and vocunt vs the upperleft corner of the two screents. Right figure describes the transformation of coordinates by calculating xoffset and yoffset.

Aside from displaying pixels on the screen, the displayer module also communicates with the buffer selector module by informing it that one screen full of data has been displayed. This occurs when hount and vount are equal to 1029 and 767 repectively.

To test the displayer, we first used testbench to check if the delays are correct. We then connected this to the bufferinterface module and check if we can display data which we inputted to the ZBT. We probed the connections using the logic analyzer to debug the circuit.

#### 3.2.3. Top Level Connections

The address coming out of the displayer is multiplexed with the data being written to the ZBT and gets routed to the proper ZBT by the buffer\_sel signal. The displayer module is also clocked by a 65 MHz clock since it uses XVGA graphics.

#### 3.2.4. XVGA Module

This module was provided by the 6.111 staff. It basically generates signals to display pixels on the screen. This module is connected to the displayer module and together they display pixels on the screen.

#### 3.2.5. DelayN Module

A module used to delay hsync, vsync and blank signals by 5 clock cycles to compensate for the 5 clock cycle delay of the displayer pipeline. This was also provided by the 6.111 staff.

#### 3.3. Read and Write Control

#### 3.3.1. Buffer Selector Module

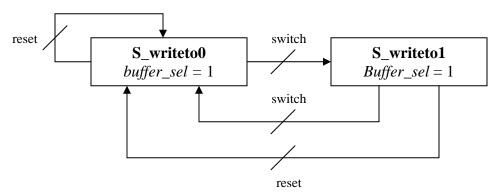

Such an elaborate read and write system, needs some sort of a control and for this system, it is provided by the buffer selector module. This module controls the switching of the buffers and ensures that this is not detected by someone viewing the screen. This module's inputs are clock, reset, donedisplaying, and triangledone while its outputs are switchbuffers and buffer\_sel.

We want our buffers to switch roles every time one frame is finished rendering and if the monitor is finished displaying. In order to achieve this, the buffer selector module listens for the triangledone signal sent by the shader module. It then latches this data in a register called tdreg, since triangledone is a pulse. At the same time, the buffer selector also listens for the donedisplaying signal sent by the displayer module and if tdreg or triangledone and donedisplaying are high. If this combined signal is high, then a signal called switch goes high.

The switching of the buffers is controlled by a two state FSM. Figure 3.3.1 shows the state transition diagram of this FSM. The states of this FSM are called s\_writeto0 and s\_writeto1. At reset, the default state is s\_writeto0. During this state, we are writing to buffer 0, thus, buffer\_sel must be set to 0. When it is time to switch buffers, in other words, switch is high, switchbuffers is set to 1 for one clock cycle, buffer\_sel is set to 1 and we transition to the second state which is s\_writeto1. The behavior of this state is similar to the first state except that buffer\_sel is set to 1 all throughout this state.

**Figure 3.3.1. State transition diagram for the buffer selector.** Note that at reset, the FSM transitions to s\_writeto0, otherwise, the states just switch.

We tested this module by simply using testbench because it is very straightforward and does not involve tricky time constraints. We also tested this module by integrating it with our other modules and displaying a green square and a red triangle which are stored in buffer 0 and buffer 1 respectively. We then connected the buffer\_sel signal to the LEDs. We used switches to freeze the frame and checked if the proper picture appears with respect to the buffer\_sel signal..

# 4. 3D World Generation

The 3D world we implemented consists of a cube, walls, and 3D block letters which spell MIT. We generated the 3D world using triangles. Because of time constraint, we did not have time to generate more complex objects. However, simple objects are enough since this project is testing, not our artistic skills, but the engine we developed to display images.

The system we have developed only needs the coordinates of the triangles which make up the world to generate its 3D image. To find these coordinates, we first drew our objects on paper and then started creating coordinates for the triangles using Excel. We realized that each the objects were merely translations of similar rectangles in the x, y, and z axis. Using this method, it was actually quite easy to finish hand plotting the cube and the MIT block. However, the wall was a tough task. It requires 260 triangles to render – therefore, a total of 780 coordinates. However, we realized that the wall is just made up of shifted triangles so we made a program in MATLAB to automatically generate the wall and store the coordinates in a matrix format.

To create the .coe files required by the triangle ROM we used MATLAB to transform the coordinates we have extracted to a .coe file written in decimal radix. We concatenated the x, y, and z coordinates of each triangle into one 36 bit decimal value.

If we had more time, we could have written more extensive MATLAB scripts to automatically generate specific polygons in the 3D plane. This way we could have made more complex looking objects.

# 5. Testing and Debugging

The testing tools we used were the Xilinx testbench, ModelSim Waveform analyzer, and the Tektronix logic analyzer. Each of these tools has a specific task in the testing and debugging of our project.

Before attempting to integrate, we exhaustively tested each module with either the testbench or the waveform analyzer. The testbench was used for circuits which do not have tight timing constraints. Slightly more complicated logic was then placed and routed then tested using the waveform analyzer which gave a more accurate timing diagram of the modules. It is a better test that the testbench in the sense that it actually maps the device and provides a rough estimate of the timing delays associated with the circuit. After ensuring that each module works independently from each other we finally integrated.

As expected, timing bugs and glitches began to appear. One of the first problems we encountered is the appearance of colored lines at the screen. At first we had absolutely, no idea, why this occurred but after asking Professor Chuang for his opinion, we realized that some of our calculations could not be calculated in one clock. Therefore we have to adjust our code and make our clock run a little bit slower. Particularly, some of our modules gets triggered only once every three clocks. Since we made the clock slower, we have to compensate for the loss in speed by pipelining our modules. This ensured first of all that our data are latched; secondly this is a form of optimization that would produce huge benefits in the long run.

The next types of problems we encountered are communication and mistiming of data signals. One example to characterize this problem is when our screen freezes, and buffer select never changes. This problem occurred because of a miscommunication between three essential modules in our project. We tracked down the cause of this problem by using the logic analyzer. It is a very powerful tool, since you could trigger at specific areas of logic. It immediately pinpointed to us where and what the problem was.

After we fixed our communications and accommodated all our propagation delays, our project was still crashing. More weird lines begin appearing and pixels aren't being shaded. The screen is also flickering hard. At this point, we had absolutely no clue what was going on until Professor Terman informed us that clocks overload. Apparently, these clock signals get routed to a lot of components and he told us that a clock could efficiently drive around a 5000 component load. When we looked at our synthesis report, we found out that our clock is driving almost 13000 components. We then decided to create two more clocks which we use to drive our divider modules which contain the largest amount of clock load. We did this and we got rid of the lines in the screen, however our screen was still flickering. After attempts of optimizing our logic even further, we realized that bitwise operations produce horrendous amounts of flicker, we then decided to multiplex our data before assigning them to wires. This was the last piece of the puzzle, the flicker was gone and we finally saw solid 3D objects appear in the screen.

One thing which made debugging and testing a challenge was the long synthesis time. Due to the large amount of resources we use: 70% of the slices, 99% of the memory, 80% of the bonded IOBs, our project took about 30 to 40 minutes to compile. We were forced to debug smartly because we could only test our new logic once every thirty minutes. Thus, we made sure we gathered enough information from our logic each time we synthesized it. To do this, we used all of our logic analyzer connectors, LEDs, and the 64 Hex Display.

Overall, we believe that we learned a lot of concepts and tricks in the debugging process. We are relieved that after spending hours debugging, we finally got our project to run.

# Conclusion

This project was a huge learning experience for us. We started this project knowing basically nothing about graphics processing but we finished with a primitive yet working 3D engine. The whole process of designing, implementing, and debugging this complex project definitely taught us the challenges of a graphics card designer. As we were working on this project, we happened to read specifications and literature about graphics cards and surprisingly, we understood a lot of terminology that graphics designers use. Terms like overclocking, unlocking pipelines, 256 bit buses, and 256 Megabytes of onboard memory made sense.

This project was very neat in the sense that we got to apply most of the concepts we learned in class to get our project up and running. The previous labs definitely helped prepare us in terms of designing, debugging, and efficient coding, but there are so many things that could arise in such a complex project. We learned that unexpected things occur – even though we thought that our logic was perfect, there always seems to be a problem somewhere. For example, each of our different modules seem to work fine independently, however, when we integrated our modules, we found that insidious problems in the form of data path conflicts, module miscommunications, timing glitches, clock overloading occur. Debugging and tracking down these problems was definitely the most time-consuming part, since for most of the time we do not understand what is making our project fail. However, in the end it was satisfying when we finally got our 3D engine running.

We made several design changes in order for the project to work in the time allotted. Our initial plan was to display two different images into two different screens and integrate two laboratory kits together. However, after realizing that our memory is not enough, we decided on displaying 2 smaller images on one screen. We also had a more elaborate design in our image shading and rendering, however due to the limitations of the math modules, we made simplifications in our shading module. Our group also chose from a number of projection schemes to project our 3D images into a 2D plane. In the end we have to use ray casting, a method used by games such as Doom. It involves simpler mathematics unlike modern methods which involves huge matrix multiplications. These calculations are beyond the scope of our knowledge, as we did not take any graphics class prior to this project. Thus it would be almost impossible for us to implement it in our labkit and produce optimal results. Modern graphics cards process these calculations using dedicated hardware and optimized chips to achieve the desired results in minimal time. Our FPGA might not be able to emulate this ability.

We had a great time working on the project albeit the frustrations and long hours during the last few days. In the end, we were very satisfied with the results. We would like to take this opportunity to thank Professors Terman and Chuang for the incredible wealth of knowledge they shared regarding the issues we had especially with clock overloading. We also wish to thank all the teaching assistants, Javier, Willie, Jae and Eric, for giving us invaluable assistance and advice whenever we have questions. We believe that this class was really excellent and an excellent way to learn digital logic design.

```

Written by: Joshua Monzon, Tony Ng, Steven Zhou

6.111 Final Project: Digital Stereoscope

The top level module used to compile the whole project into the labkit. Contains integrated

submodule to create a digital stereoscope. Displays a 3D rendered world in the monitor from

two different viewpoints. These viewpoints correspond to what each eye sees. The user could

use the keyboard to move around the world.

all rights reserved.

Acknowledgements: Labkit code was made by Nathan Ickes.

module digital_stereoscope(beep, audio_reset_b,

ac97_sdata_out, ac97_sdata_in, ac97_synch,

ac97_bit_clock,

vga_out_red, vga_out_green, vga_out_blue, vga_out_sync_b,

vga_out_blank_b, vga_out_pixel_clock, vga_out_hsync,

vga_out_vsync,

tv_out_ycrcb, tv_out_reset_b, tv_out_clock, tv_out_i2c_clock,

tv_out_i2c_data, tv_out_pal_ntsc, tv_out_hsync_b,

tv_out_vsync_b, tv_out_blank_b, tv_out_subcar_reset,

tv_in_ycrcb, tv_in_data_valid, tv_in_line_clock1,

tv_in_line_clock2, tv_in_aef, tv_in_hff, tv_in_aff,

tv_in_i2c_clock, tv_in_i2c_data, tv_in_fifo_read,

tv_in_fifo_clock, tv_in_iso, tv_in_reset_b, tv_in_clock,

ram0_data, ram0_address, ram0_adv_ld, ram0_clk, ram0_cen_b,

{\tt ram0\_ce\_b,\ ram0\_oe\_b,\ ram0\_we\_b,\ ram0\_bwe\_b,}

raml_data, raml_address, raml_adv_ld, raml_clk, raml_cen_b,

raml_ce_b, raml_oe_b, raml_we_b, raml_bwe_b,

clock_feedback_out, clock_feedback_in,

flash_data, flash_address, flash_ce_b, flash_oe_b, flash_we_b,

flash_reset_b, flash_sts, flash_byte_b,

rs232_txd, rs232_rxd, rs232_rts, rs232_cts,

mouse_clock, mouse_data, keyboard_clock, keyboard_data,

clock_27mhz, clock1, clock2,

disp_blank, disp_data_out, disp_clock, disp_rs, disp_ce_b,

disp_reset_b, disp_data_in,

button0, button1, button2, button3, button_enter, button_right,

button_left, button_down, button_up,

switch,

led,

user1, user2, user3, user4,

daughtercard,

systemace_data, systemace_address, systemace_ce_b,

systemace_we_b, systemace_oe_b, systemace_irq, systemace_mpbrdy,

analyzer1_data, analyzer1_clock,

analyzer2_data, analyzer2_clock,

analyzer3_data, analyzer3_clock,

analyzer4_data, analyzer4_clock);

output beep, audio_reset_b, ac97_synch, ac97_sdata_out;

input ac97_bit_clock, ac97_sdata_in;

```

```

output [7:0] vga_out_red, vga_out_green, vga_out_blue;

output vga_out_sync_b, vga_out_blank_b, vga_out_pixel_clock,

vga_out_hsync, vga_out_vsync;

output [9:0] tv_out_ycrcb;

output tv_out_reset_b, tv_out_clock, tv_out_i2c_clock, tv_out_i2c_data,

tv_out_pal_ntsc, tv_out_hsync_b, tv_out_vsync_b, tv_out_blank_b,

tv_out_subcar_reset;

input [19:0] tv_in_ycrcb;

input tv_in_data_valid, tv_in_line_clock1, tv_in_line_clock2, tv_in_aef,

tv_in_hff, tv_in_aff;

output tv_in_i2c_clock, tv_in_fifo_read, tv_in_fifo_clock, tv_in_iso,

tv_in_reset_b, tv_in_clock;

inout tv_in_i2c_data;

inout [35:0] ram0_data;

output [18:0] ram0_address;

output ram0_adv_ld, ram0_clk, ram0_cen_b, ram0_ce_b, ram0_oe_b, ram0_we_b;

output [3:0] ram0_bwe_b;

inout [35:0] ram1_data;

output [18:0] raml_address;

output raml_adv_ld, raml_clk, raml_cen_b, raml_ce_b, raml_oe_b, raml_we_b;

output [3:0] ram1_bwe_b;

input clock_feedback_in;

output clock_feedback_out;

inout [15:0] flash_data;

output [23:0] flash_address;

output flash_ce_b, flash_oe_b, flash_we_b, flash_reset_b, flash_byte_b;

input flash_sts;

output rs232_txd, rs232_rts;

input rs232_rxd, rs232_cts;

input mouse_clock, mouse_data, keyboard_clock, keyboard_data;

input clock_27mhz, clock1, clock2;

output disp_blank, disp_clock, disp_rs, disp_ce_b, disp_reset_b;

input disp_data_in;

output disp_data_out;

input button0, button1, button2, button3, button_enter, button_right,

button_left, button_down, button_up;

input [7:0] switch;

output [7:0] led;

inout [31:0] user1, user2, user3, user4;

inout [43:0] daughtercard;

inout [15:0] systemace_data;

output [6:0] systemace_address;

output systemace_ce_b, systemace_we_b, systemace_oe_b;

input systemace_irq, systemace_mpbrdy;

output [15:0] analyzer1_data, analyzer2_data, analyzer3_data,

analyzer4 data;

output analyzer1_clock, analyzer2_clock, analyzer3_clock, analyzer4_clock;

// I/O Assignments

// Audio Input and Output

```

```

assign beep= 1'b0;

assign audio_reset_b = 1'b0;

assign ac97_synch = 1'b0;

assign ac97_sdata_out = 1'b0;

// Video Output

assign tv_out_ycrcb = 10'h0;

assign tv_out_reset_b = 1'b0;

assign tv_out_clock = 1'b0;

assign tv_out_i2c_clock = 1'b0;

assign tv_out_i2c_data = 1'b0;

assign tv_out_pal_ntsc = 1'b0;

assign tv_out_hsync_b = 1'b1;

assign tv_out_vsync_b = 1'b1;

assign tv_out_blank_b = 1'b1;

assign tv_out_subcar_reset = 1'b0;

// Video Input

assign tv_in_fifo_read = 1'b1;

assign tv_in_fifo_clock = 1'b0;

assign tv_in_iso = 1'b1;

assign tv_in_clock = clock_27mhz;//1'b0;

// ZBT SRAMs

// enable RAMO pins

assign ram0_ce_b = 1'b0;

assign ram0_oe_b = 1'b0;

assign ram0_adv_ld = 1'b0;

assign ram0_bwe_b = 4'h0;

// enable RAM1 pins

assign raml_ce_b = 1'b0;

assign ram1_oe_b = 1'b0;

assign raml_adv_ld = 1'b0;

assign ram1_bwe_b = 4'h0;

assign clock_feedback_out = 1'b0;

// Flash ROM

assign flash_data = 16'hZ;

assign flash_address = 24'h0;

assign flash_ce_b = 1'b1;

assign flash_oe_b = 1'b1;

assign flash_we_b = 1'b1;

assign flash_reset_b = 1'b0;

assign flash_byte_b = 1'b1;

// RS-232 Interface

assign rs232_txd = 1'b1;

assign rs232_rts = 1'b1;

// User I/Os

assign user1 = 32'hZ;

assign user2 = 32'hZ;

assign user3 = 32'hZ;

assign user4 = 32'hZ;

// Daughtercard Connectors

assign daughtercard = 44'hZ;

// SystemACE Microprocessor Port

assign systemace_data = 16'hZ;

assign systemace_address = 7'h0;

assign systemace_ce_b = 1'b1;

assign systemace_we_b = 1'b1;

assign systemace_oe_b = 1'b1;

// use FPGA's digital clock manager to produce a

// 65MHz clock (actually 64.8MHz)

```

```

wire clock_65mhz_unbuf,clock_65mhz,xclock_65mhz,x2clock_65mhz,x3clock_65mhz;

DCM vclk1(.CLKIN(clock_27mhz),.CLKFX(clock_65mhz_unbuf));

// synthesis attribute CLKFX_DIVIDE of vclk1 is 10

// synthesis attribute CLKFX_MULTIPLY of vclk1 is 24

// synthesis attribute CLK_FEEDBACK of vclk1 is NONE

// synthesis attribute CLKIN_PERIOD of vclk1 is 37

BUFG vclk2(.O(clock_65mhz),.I(clock_65mhz_unbuf));

BUFG vclk3(.0(xclock_65mhz),.I(clock_65mhz_unbuf));

BUFG vclk4(.O(x2clock_65mhz),.I(clock_65mhz_unbuf));

// default clock for the light load modules

wire clk = clock_65mhz;

wire clk_div1 = xclock_65mhz;

// clock of one of the high clock load divider modules

wire clk_div2 = x2clock_65mhz;

// clock of the other high clock load divider module

// power-on reset generation

wire power_on_reset;

// remain high for first 16 clocks

SRL16 reset_sr (.D(1'b0), .CLK(clk), .Q(power_on_reset),

.AO(1'b1), .A1(1'b1), .A2(1'b1), .A3(1'b1));

defparam reset_sr.INIT = 16'hFFFF;

// ENTER button is user reset

wire reset, user_reset;

debounce db1(power_on_reset, clk, ~button_enter, user_reset);

assign reset = (user_reset || power_on_reset) ? 1 : 0;

// Display module used for debugging

reg [63:0] dispdata;

display_16hex hexdisp1(reset, clk, dispdata, disp_blank, disp_clock, disp_rs, disp_ce_b,

disp_reset_b, disp_data_out);

// VGA Output. In order to meet the setup and hold times of the

// AD7125, we send it ~clock_65mhz.

assign vga_out_red = pixel[23:16];

assign vga_out_green = pixel[15:8];

assign vga_out_blue = pixel[7:0];

assign vga_out_sync_b = 1'b1; // not used

assign vga_out_pixel_clock = ~clock_65mhz;

assign vga_out_blank_b = ~b;

assign vga_out_hsync = hs;

assign vga_out_vsync = vs;

// Debugging

always @(posedge clk)

dispdata <= {ram0_wdata, 9'b0, ram0_addr};</pre>

assign led = ~{state, ~buffer_sel, buffer_sel, mem_ready, lasttriangledone};

// SLOW Clock - runs at 1/3 the speed of the 65 MHz clock. Used to accomodate the shader

// and comparator modules which require 3 clock cycles to do their computations

reg slow_clk;

reg [1:0] counter;

always @(posedge clk) begin

if (reset) begin

counter<=0;

slow_clk<=1;

end

else if (counter == 2) begin

counter <= 0;

slow_clk <= 1;

end

else begin

counter <= counter+1;</pre>

slow_clk <= 0;</pre>

end

end

```

```

// XVGA video signals

wire [10:0] hcount;

wire [9:0] vcount;

wire hsync, vsync, blank;

xvga xvga1(clk, hcount, vcount, hsync, vsync, blank);

// ZBT SRAMs - connections to the onboard SRAMs

wire [35:0] ram0_read_data, ram1_read_data;

wire [35:0] ram0_wdata, ram1_wdata;

wire ram0_we, ram1_we;

wire [18:0] zbt0_addr, zbt1_addr;

zbt_6111 zbt0(zbt0_clk, 1'b1, ram0_we, zbt0_addr,

ram0_wdata, ram0_read_data,

ram0_clk, ram0_we_b, ram0_address, ram0_data, ram0_cen_b);

zbt_6111 zbt1(zbt1_clk, 1'b1, ram1_we, zbt1_addr,

raml_wdata, raml_read_data,

raml_clk, raml_we_b, raml_address, raml_data, raml_cen_b);

\ensuremath{//} Displayer - extracts data from the ZBTs and displays them on the screen

wire buffer_sel, switchbuffers;

wire [23:0] pixel;

wire sds;

wire [35:0] fromzbt_data = buffer_sel? ram0_read_data : ram1_read_data ;

wire [18:0] tozbt_addr;

wire donedisplaying;

displayer disp (clk, reset, hcount, vcount, fromzbt_data,

tozbt_addr, pixel, donedisplaying, switchbuffers);

// Read and Write muxes - multiplexers to route the proper address and

// clocks to the correct ZBTs

assign zbt0_addr = buffer_sel ? tozbt_addr: ram0_addr;

assign zbt1_addr = buffer_sel ? ram1_addr : tozbt_addr;

assign zbt1_clk = clk;

assign zbt0_clk = clk;

// Delay Path - delays the hsync, vsync, and blank signals by 5 clock

// cycles to accomodate the 3 stage pipeline of the displayer module

wire

b, hs, vs;

delayN dn1(clk, hsync, hs);

delayN dn2(clk, sync, vs);

delayN dn3(clk, blank, b);

// 3D World - User Movement, Projection, Rendering, Shading, Storage Path

wire [17:0] pixeladdr;

wire [34:0] pixeldata;

wire [18:0] ram0_addr, ram1_addr;

wire [32:0] e1c1, e1c2, e1c3, e2c1, e2c2, e2c3;

wire [15:0] gaze_angle, tilt_angle;

wire [35:0] eye1, eye2;

wire [9:0] num_triangles;

wire [8:0] triangle_addr;

wire [7:0] inColor;

wire [35:0] corner1, corner2, corner3;

wire [7:0] color;

```

```

// Control and Communication Signals

wire shading_ready, shading_done;

wire mem readv;

wire tri_ready;

wire last_triangle;

wire lasttriangledone;

wire want_new_triangle;

reg old_frame, new_frame;

always @ (posedge clk) begin

if (slow_clk) begin

old_frame <= last_triangle;

new_frame <= (last_triangle & (~ old_frame));</pre>

end

end

// Outputs the corners and color of triangles stored in memory

trianglememory tmem(.addr(triangle_addr), .clk(clk), .din1(36'b0), .din2(36'b0),

.din3(36'b0), .dinc(8'b0), .dout1(corner1), .dout2(corner2),

.dout3(corner3), .doutc(inColor), .we(1'b0),

.num_triangles(num_triangles));

// Takes inputs from keyboard and updates eye position, gaze and tilt angles

position_controller posctrl(.clock(clk), .new_frame(new_frame), .reset(reset),

.keyboard_clock(keyboard_clock), .keyboard_data(keyboard_data),

.eye1(eye1), .eye2(eye2), .gaze_angle(gaze_angle),

.tilt_angle(tilt_angle));

// Projects corners of triangle in 3-D space onto the screen

perspectiveprojector pp(.clk(clk), .slow_clk(slow_clk), .reset(reset),

.corner1(corner1), .corner2(corner2), .corner3(corner3),

.inColor(inColor), .eye1(eye1), .eye2(eye2), .gaze_angle(gaze_angle),

.tilt_angle(tilt_angle), .start(want_new_triangle),

.num_triangles(num_triangles), .reset_last_triangle(lasttriangledone),

.outColor(color), .triangle_addr(triangle_addr),.elc1(elc1), .elc2(elc2),

.elc3(elc3), .e2c1(e2c1), .e2c2(e2c2), .e2c3(e2c3), .done(tri_ready),

.last_triangle(last_triangle));

// Extracts pixels' addresses and colors as well as routing signals

Projector_Shader ps (.clk(clk), .clk_div1(clk_div1), .clk_div2(clk_div2),

.slow_clk(slow_clk),

.reset(reset), .mem_ready(mem_ready), .tri_ready(tri_ready), .elc1(elc1),

.elc2(elc2), .elc3(elc3), .e2c1(e2c1), .e2c2(e2c2), .e2c3(e2c3),

.color(color), .last_triangle(last_triangle),

.shading_ready(shading_ready), .shading_done(shading_done),

.pixel_address(pixeladdr), .pixel_data(pixeldata),

.want new triangle(want new triangle),

.last_triangle_shading_done(lasttriangledone));

// Controls which buffer is being written to and read from

bufferselector bselector(.clock(clk), .reset(reset), .donedisplaying(donedisplaying),

.triangledone(lasttriangledone),.switchbuffers(switchbuffers),

.buffer_sel(buffer_sel));

// Interfaces the shader module to the ZBTS, controls overlap of images

bufferinterface datatobuffer (.clock(clk), .reset(reset), .shading_ready(shading_ready),

.shading_done(shading_done),.pixeldata(pixeldata), .pixeladdr(pixeladdr),

.ram0_wdata(ram0_wdata), .ram0_addr(ram0_addr), .ram0_we(ram0_we),

.raml_wdata(raml_wdata), .raml_addr(raml_addr), .raml_we(raml_we),

.mem_ready(mem_ready), .buffer_sel(buffer_sel),

.switchbuffers(switchbuffers));

endmodule

// xvga: Generate XVGA display signals (1024 x 768 @ 60Hz)

module xvga(vclock, hcount, vcount, hsync, vsync, blank);

input vclock;

```

```

output [10:0] hcount;

output [9:0] vcount;

output vsync; output hsync;

output blank;

hsync, vsync, hblank, vblank, blank;

reg [10:0] hcount; // pixel number on current line

reg [9:0] vcount; // line number

// horizontal: 1344 pixels total

// display 1024 pixels per line

wire

hsyncon, hsyncoff, hreset, hblankon;

hblankon = (hcount == 1023);

assign

hsyncon = (hcount == 1047);

assign

hsyncoff = (hcount == 1183);

assign

assign

hreset = (hcount == 1343);

// vertical: 806 lines total

// display 768 lines

wire

vsyncon, vsyncoff, vreset, vblankon;

vblankon = hreset & (vcount == 767);

assign

vsyncon = hreset & (vcount == 776);

assign

assign

vsyncoff = hreset & (vcount == 782);

vreset = hreset & (vcount == 805);

assign

// sync and blanking

next_hblank, next_vblank;

wire

assign next_hblank = hreset ? 0 : hblankon ? 1 : hblank;

assign next_vblank = vreset ? 0 : vblankon ? 1 : vblank;

always @(posedge vclock) begin

hcount <= hreset ? 0 : hcount + 1;

hblank <= next_hblank;</pre>

hsync <= hsyncon ? 0 : hsyncoff ? 1 : hsync; // active low</pre>

vcount <= hreset ? (vreset ? 0 : vcount + 1) : vcount;</pre>

vblank <= next_vblank;</pre>

vsync <= vsyncon ? 0 : vsyncoff ? 1 : vsync; // active low</pre>

blank <= next_vblank | (next_hblank & ~hreset);</pre>

end

endmodule

// parameterized delay line

module delayN(clk, in, out);

input clk;

input in;

output out;

parameter NDELAY = 5;

reg [NDELAY-1:0] shiftreg;

out = shiftreg[NDELAY-1];

wire

always @(posedge clk)

shiftreg <= {shiftreg[NDELAY-2:0],in};</pre>

```

endmodule

```

Written by: Joshua Jen Monzon

6.111 Final Project: Digital Stereoscope

This module interfaces the shading module with the ZBT SRAMS. Takes in control signals

when the pixels of a triangle need to be stored in the SRAMS and when a triangle is done

rendering. It also takes in the corresponding pixeldata and pixel address where the data

will be stored. It then routes the data to the proper ZBT pins depending which buffer is

selected and whether the data needs to be written or not. Comprised of different submodules

which performs a specific function in the buffer interface.

module bufferinterface (clock, reset, shading_ready, shading_done, pixeldata, pixeladdr,

ram0_wdata, ram0_addr, ram0_we, ram1_wdata, ram1_addr, ram1_we,

mem_ready, buffer_sel, switchbuffers);

input clock, reset;

// global signals

input shading_ready;

input shading_done;

// means rendered pixels are starting to be sent

// means a triangle is done rendering

input [34:0] pixeldata;

// \{24b'color, 11b'depth\}, information of a pixel // address to store the pixel (640*y + x)

input [17:0] pixeladdr;

// current buffer being written to

input buffer_sel;

input switchbuffers;

// pulse indicating buffers are switching

output [35:0] ram0_wdata, ram1_wdata; // color data written to corresponding ZBT's

output [18:0] ram0_addr, ram1_addr;

// address where the data is written to

output ram0_we, ram1_we;

output mem_ready;

// signal indicating memory is ready to accept data

wire [34:0] inputdata, bufferinitdata;

wire [18:0] writeaddr, bufferinitaddr, inputaddr;

wire [23:0] colordata;

wire mem_ready, init_done, init, we, switchbuffers, buffer_sel;

wire dcreset;

// Refresh buffers during reset or when switching buffers

assign dcreset = (reset || switchbuffers) ? 1 : 0;

// Chooses what data will be written in the memory, if we are initializing

// then we want data from the initiator otherwise we get data from the shading module

assign inputdata = mem_ready ? pixeldata : bufferinitdata;

assign inputaddr = mem_ready ? {1'b0, pixeladdr} : bufferinitaddr;

// Compares depth and makes decisions whether to write to the memory or not

depthcomparator dc (.clock(clock), .reset(dcreset), .shading_ready(shading_ready),

.shading_done(shading_done), .init_done(init_done), .inputdata(inputdata),

.pixeladdr(inputaddr), .writeaddr(writeaddr), .colordata(colordata), .we(we),

.init(init), .mem_ready(mem_ready));

// Initiates the memory of the buffers during reset or switching

depthbufferinitiator dbi (.clock(clock), .init(init), .pixeldata(bufferinitdata),

.pixeladdr(bufferinitaddr), .init_done(init_done));

// The module which process data from the displayer and depthcomparator and