# The Dorm Room Genie:

Design of a Dorm Room Automation System

David Nedzel and Aaron Stonely

6.111: Introductory Digital Systems Laboratory

December 14, 2005

#### **Abstract**

This paper describes the design and implementation of a dorm room automation system which we call the Dorm Room Genie. Through a system of keyboard inputs, push buttons, sensors, and a VGA display, the Dorm Room Genie provides the student with a customizable way to manage their dorm room with the ultimate goal of making the student's life easier. Students are issued keys by which to access their dorm rooms, but far too often, a key is forgotten inside, leaving the student locked out. The Dorm Room Genie addresses this issue by providing the student with the ability for keyless entry. The Dorm Room Genie also contains a burglar alarm system which will provide the student additional security in their dorm room. This additional security is provided through a loud buzzer and the ability to take photographs of the intruder. Additional functionality includes a digital clock and alarm clock. The Dorm Room Genie also provides the student with the ability to control the lights manually, automatically, or in conjunction with the alarm clock. Finally, student will be able to instantly see the status of the dorm room automation system via a system status display. The objective of this paper is to outline the planning, design, testing, and debugging involved in the implementation of a dorm room automation system on a field-programmable gate array.

# **Table of Contents**

| Dorm Room Genie Overview        | 5   |

|---------------------------------|-----|

| Description                     | 6   |

| Signal Processing Module        | 6   |

| Lock Module                     | 11  |

| Burglar Alarm Module            | 14  |

| Time Division Modules           | 16  |

| Clock Module                    | 17  |

| Wake-up Alarm Module            | 19  |

| Lighting Module                 | 22  |

| Display Module                  | 27  |

| Video/Motion Module             | 30  |

| Labkit Module                   | 34  |

| Testing and Debugging           | 36  |

| Section by Aaron Stonely        | 36  |

| Clock and Wake-up Alarm Modules | 37  |

| Lighting Module                 | 37  |

| Display Module                  | 38  |

| Labkit Module                   | 39  |

| Section by David Nedzel         | 40  |

| Signal Processing Module        | 40  |

| Lock Module                     | 40  |

| Burglar Alarm Module            | 40  |

| Video/Motion Module             | 41  |

| Conclusion                      | 42  |

| Appendix                        | 45  |

| Burglar Module                  | 45  |

| Video Capture Module            | 46  |

| Clock Module                    | 47  |

| One Hertz Enable Module         | 48  |

| Clock Register Module           | 49  |

| Character String Display Module | 50  |

| Debounce Module                 | 51  |

| DelayN Module                   | 52  |

| Delaycount Module               | 52  |

| Display Module                  | 53  |

| Divider Module                  | 58  |

| Font_Rom                        | 59  |

| Labkit Module                   | 60  |

| Debounce2 Module                | 67  |

| Lighting Module                 | 67  |

| One_hz_enable Module            |     |

| Demo Enable Module              | 71  |

| ADC Sampler Module              | 72  |

| Lock Module                     | 72. |

| NTSC to Pixel Module    |     |

|-------------------------|-----|

| PS2 Keyboard Module     | 76  |

| Ram16x8 Module          |     |

| Signal Processor Module | 81  |

| Synchronizer Module     |     |

| VGA Sync Module         |     |

| Video Module            |     |

| Video Decoder Module.   | 88  |

| Wake-up Module          | 104 |

| ZBT Module              |     |

# **List of Tables and Figures**

# **Tables**

| 1.   | Listing of ASCII translations by PS/2 to ASCII Module |    |

|------|-------------------------------------------------------|----|

| 2.   | Listing of Extended ASCII Assignments                 |    |

| 3.   | Lock Control Signals                                  | 9  |

| 4.   | Burglar Control Signals.                              | 9  |

| 5.   | Lighting Control Signals                              | 9  |

| 6.   | Wake Control Signals.                                 |    |

| 7.   | Clock Control Signals                                 | 10 |

| 8.   | Picture Control Signals                               | 10 |

| 9.   | Time Conversion Counts and Values                     | 16 |

| 10.  | Display Items and their Strings                       | 29 |

| 11.  | Display Items, their Inputs, and Coordinates          | 30 |

| Figu | res                                                   |    |

| 1.   | Signal Processing Module Block Diagram                | 6  |

| 2.   | Signal Processor's FSM                                | 11 |

| 3.   | Lock Module Block Diagram                             | 12 |

| 4.   | Lock Module FSM                                       |    |

| 5.   | Burglar Alarm Module Block Diagram                    | 14 |

| 6.   | Burglar Alarm FSM                                     | 15 |

| 7.   | Time Conversion Timing                                | 16 |

| 8.   | Clock Module Block Diagram.                           |    |

| 9.   | Clock Module Timing Diagram                           |    |

| 10.  | Wake-up Alarm Module Block Diagram                    | 20 |

| 11.  | Wake-up Alarm Module Timing                           |    |

| 12.  | Lighting Module Block Diagram.                        |    |

| 13.  | Lighting Module Timing                                |    |

| 14.  | Display Module Block Diagram                          |    |

| 15.  | Video Modual Block Diagram.                           |    |

| 16.  | Video Module FSM                                      |    |

| 17.  | Motion Detector Block Diagram.                        | 33 |

| 18.  | Dorm Room Controller Block Diagram                    | 35 |

| 19   | Dorm Room Genie Block Diagram                         | 36 |

#### **Dorm Room Genie Overview**

In university residence halls across the country, you'll find lots of busy students – many of whom enjoy gadgets and conveniences which make there lives a little more simple and fun. The Dorm Room Genie enhances a student's dormitory room with several features and conveniences which the user can choose to make use of:

- Electronic Lock: After installing an electronic strike plate, the Dorm Room Genie allows the student to input a password which can be used to unlock the door. This is convenient in the event of an accidental lock out, or in the event that the student wishes to grant a friend access to his or her room. The lock can be set to locked or unlocked, and additionally password entry can be disabled if the student wishes for an enhanced level of security.

- **Burglar Alarm**: After installing a magnetic sensor on the door, and mounting a camera, the student can take advantage of the security alarm feature. The security alarm can be armed at the touch of a button, to be tripped by the door sensor and a camera-implemented motion detector. If the student wishes to activate the burglar alarm while at home for added security, motion detection can be disabled. When the alarm is triggered, a buzzer sounds, the time is recorded, and the camera begins capturing images of the intrusion which can be viewed later. The alarm can be deactivated by entering the electronic lock password.

- **Lighting Control**: The Dorm Room Genie also offers advanced lighting control features. A lamp plugged into the system can be brightened or dimmed at the touch of a button. Additionally, the lighting controller will flash the lights during an intrusion to further deter a burglar. The lighting module also interacts with the alarm clock as described below.

- **Alarm Clock**: The Dorm Room Genie also contains an alarm clock which sounds a buzzer at the desired time. Optionally, 15 minutes before the user-programmed wake-up time, the lights can be set to gradually brighten to gently wake the student before the buzzer sounds. A 15 minute snooze feature is also included.

- **Display**: An easy to read LCD display outputs the status of the system to the user, and also allows the user to view images captured during an intrusion.

The user interfaces with the Dorm Room Genie thorough a standard PS/2 keyboard which is used for password setting and entry, setting the clock and wake-up time in addition to sending control signals to the various modules of the system. The keyboard with the control buttons is on the inside of the room and a keyboard without the control buttons is on the outside door. In explaining the architecture of the Dorm Room Genie, the follow section will consider the functionality and implementation of each individual model separately, and also explain how the modules interact with one another.

# Description

# **Signal Processing Module**

--By David Nedzel

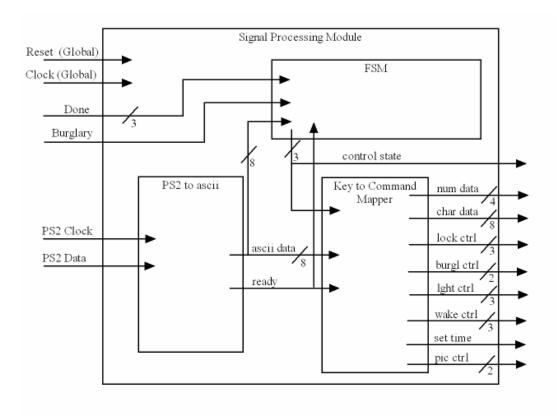

The Signal Processing Module allows the user to input commands into the system. It is responsible for interpreting the user's keyboard inputs, and sending the appropriate commands and signals off to the other modules of the Dorm Room Genie. As illustrated in Figure 1, the Signal Processing module has three primary components: A PS/2 to ASCII converter, a Finite State Machine (FSM), and a key to command mapper.

Figure 1

Both the PS/2 clock and data enter the signal processing module where they are fed into the PS2 to ASCII converter. The converter's job is to interpret the native keyboard data and output 8-bit ASCII code. The PS/2 module provided by the 6.111 staff correctly handled letters, assigning them the capital letter ASCII codes, numbers and punctuation marks as summarized in Table 1. Unfortunately, we also required the use of the keyboard's function keys and numeric keypad to send control signals to the lock, burglar alarm, clock, wake-up alarm, lighting and video modules. It was therefore necessary to expand the functionality of this module to include those additional keys listed in Table 2 along with their intended function. Note that the ASCII values assigned are not actually associated with those keys, but were used for convenience since they fall

outside of the standard 128 basic ASCII codes. It is of little concern that these codes overlap with the 256 extended ASCII codes, since the extended ASCII symbols are unimportant to this implementation. Once the data is converted to ASCII codes, it is sent to both the FSM and command mapper unit.

| Keyboard<br>Signal | ASCII Code | Character | Keyboard<br>Signal | ASCII Code | Character |

|--------------------|------------|-----------|--------------------|------------|-----------|

| 8'h1C:             | 8'h41      | А         | 8'h45:             | 8'h30      | 0         |

| 8'h32:             | 8'h42      | В         | 8'h16:             | 8'h31      | 1         |

| 8'h21:             | 8'h43      | С         | 8'h1E:             | 8'h32      | 2         |

| 8'h23:             | 8'h44      | D         | 8'h26:             | 8'h33      | 3         |

| 8'h24:             | 8'h45      | E         | 8'h25:             | 8'h34      | 4         |

| 8'h2B:             | 8'h46      | F         | 8'h2E:             | 8'h35      | 5         |

| 8'h34:             | 8'h47      | G         | 8'h36:             | 8'h36      | 6         |

| 8'h33:             | 8'h48      | Н         | 8'h3D:             | 8'h37      | 7         |

| 8'h43:             | 8'h49      | 1         | 8'h3E:             | 8'h38      | 8         |

| 8'h3B:             | 8'h4A      | J         | 8'h46:             | 8'h39      | 9         |

| 8'h42:             | 8'h4B      | K         |                    |            |           |

| 8'h4B:             | 8'h4C      | L         | 8'h0E:             | 8'h60      |           |

| 8'h3A:             | 8'h4D      | М         | 8'h4E:             | 8'h2D      | -         |

| 8'h31:             | 8'h4E      | N         | 8'h55:             | 8'h3D      | =         |

| 8'h44:             | 8'h4F      | 0         | 8'h5D:             | 8'h5C      | \         |

| 8'h4D:             | 8'h50      | Р         | 8'h29:             | 8'h20      | (space)   |

| 8'h15:             | 8'h51      | Q         | 8'h54:             | 8'h5B      | [         |

| 8'h2D:             | 8'h52      | R         | 8'h5B:             | 8'h5D      | ]         |

| 8'h1B:             | 8'h53      | S         | 8'h4C:             | 8'h3B      | •         |

| 8'h2C:             | 8'h54      | T         | 8'h52:             | 8'h27      | 1         |

| 8'h3C:             | 8'h55      | U         | 8'h41:             | 8'h2C      | ,         |

| 8'h2A:             | 8'h56      | V         | 8'h49:             | 8'h2E      |           |

| 8'h1D:             | 8'h57      | W         | 8'h4A:             | 8'h2F      | /         |

| 8'h22:             | 8'h58      | X         | 8'h5A:             | 8'h0D      | (enter)   |

| 8'h35:             | 8'h59      | Υ         |                    |            |           |

| 8'h1A:             | 8'h5A      | Z         |                    |            |           |

Table 1: Listing of ASCII translations by PS/2 to ASCII Module

| Keyboard Signal | "ASCII" Code | Key       | Function              |

|-----------------|--------------|-----------|-----------------------|

| 8'h05:          | 8'h81        | F1        | Lock                  |

| 8'h06:          | 8'h82        | F2        | Unlock                |

| 8'h04:          | 8'h83        | F3        | Inactive              |

| 8'h0C:          | 8'h84        | F4        | <not used=""></not>   |

| 8'h03:          | 8'h85        | F5        | Arm                   |

| 8'h0B:          | 8'h86        | F6        | Disarm                |

| 8'h83:          | 8'h87        | F7        | Next Picture          |

| 8'h0A:          | 8'h88        | F8        | Previous Picture      |

| 8'h01:          | 8'h89        | F9        | Set Wake Time         |

| 8'h09:          | 8'h8A        | F10       | Set Clock             |

| 8'h78:          | 8'h8B        | F11       | Set Password          |

| 8'h07:          | 8'h8C        | F12       | <not used=""></not>   |

|                 |              |           |                       |

| 8'h69:          | 8'h91        | numeric 1 | Alarm Clock On        |

| 8'h72:          | 8'h92        | numeric 2 | Alarm Clock Off       |

| 8'h7A:          | 8'h93        | numeric 3 |                       |

| 8'h6B:          | 8'h94        | numeric 4 | Lights Off            |

| 8'h73:          | 8'h95        | numeric 5 | Lights Sleep          |

| 8'h74:          | 8'h96        | numeric 6 | Lights Dim            |

| 8'h6C:          | 8'h97        | numeric 7 | Lights On             |

| 8'h75:          | 8'h98        | numeric 8 | Lights Auto           |

| 8'h7D:          | 8'h99        | numeric 9 | Lights Bright         |

| 8'h70:          | 8'h9A        | numeric 0 | Alarm Clock<br>Snooze |

| 8'h71:          | 8'h9B        | numeric . | 5522                  |

Table 2: Listing of extended ASCII assignments

The job of the command mapper is to convert the incoming ASCII data to an appropriate format for each of the modules, and route those data and commands to the modules. The signal processing modules sends three distinct types of signals: data signals, control commands and state information. There are two types of data signals: The first, character data sent to the lock, is simply the ASCII codes received by the command mapper. When such ASCII data corresponds to one of the characters listed in Table 1, that data is simply passed along to the lock module. The second type of data, numbed data sent to the clock and wake modules, involves slightly more processing. If the ASCII data is recognized as a number, that number is reduced to 4-bit hexadecimal format before being passed along to the clock and wake modules. This is actually quite simple to engineer, since the four low bits of the ASCII code for numbers are the hexadecimal representation of the numbers.

The command mapper must also pass along control signals from the various user inputs listed in Table 2. I will consider each control signal in turn, explaining exactly when and why it is sent based upon user input. For each module, a "zero" signal corresponds to "no signal being sent". The lock module receives the signals summarized in Table 3. The lock signal is sent when the user pushes "lock," but also if the user arms the burglar alarm. The unlock, inactive and change password signals are sent when the user pushes the corresponding "unlock," "inactive" and change password buttons. Each signal is sent for exactly one clock cycle.

| Lock Control Signals |                     |  |

|----------------------|---------------------|--|

| Signal               | Meaning             |  |

| 3'h1                 | Lock                |  |

| 3'h2                 | Unlock              |  |

| 3'h3                 | Inactive            |  |

| 3'h4                 | <not used=""></not> |  |

| 3'h5                 | Change Password     |  |

| 3'h6                 | <not used=""></not> |  |

| 3'h7                 | <not used=""></not> |  |

| 3'h0                 | No signal           |  |

| <b>Burglar Alarm Control Signals</b> |                     |  |

|--------------------------------------|---------------------|--|

| Signal                               | Meaning             |  |

| 2'h1                                 | Arm                 |  |

| 2'h2                                 | Disarm              |  |

| 2'h3                                 | <not used=""></not> |  |

| 2'h0                                 | No Signal           |  |

Table 4: Burglar Alarm Control Signals

Table 3: Lock Control Signals

The burglar alarm module receives the signals summarized in Table 4. The arm signal is sent when the user pushes "arm", and the disarm signal is sent when the user pushes "disarm", but also when the user either pushes the unlock button, or when the user enters set password mode. After all, you wouldn't be able to disarm the system if a burglary occurred during a password set phase, since you wouldn't be able to enter the code to disarm the system. For the remaining lighting, wake alarm, clock and picture playback module (part of the video module) the signals summarized in Tables 5, 6, 7 and 8 are sent exactly when the user pushes the corresponding button.

| <b>Lighting Control Signals</b> |                     |  |

|---------------------------------|---------------------|--|

| Signal                          | Meaning             |  |

| 3'h1                            | Off                 |  |

| 3'h2                            | On                  |  |

| 3'h3                            | Auto                |  |

| 3'h4                            | Bright              |  |

| 3'h5                            | Dim                 |  |

| 3'h6                            | Sleep               |  |

| 3'h7                            | <not used=""></not> |  |

| 3'h0                            | No Signal           |  |

| Wake Alarm Control Signals |                     |  |

|----------------------------|---------------------|--|

| Signal                     | Meaning             |  |

| 3'h1                       | Wake Alarm On       |  |

| 3'h2                       | Wake Alarm Off      |  |

| 3'h3                       | Snooze              |  |

| 3'h4                       | Wake Alarm Set      |  |

| 3'h5                       | <not used=""></not> |  |

| 3'h6                       | <not used=""></not> |  |

| 3'h7                       | <not used=""></not> |  |

| 3'h0                       | No Signal           |  |

Table 5: Lighting Control Signals

Table 6: Wake Control Signals

| Clock Control Signals |           |  |

|-----------------------|-----------|--|

| Signal                | Meaning   |  |

| 1'b1                  | Set Clock |  |

| 1'b0                  | No Signal |  |

| Picture Control Signals |                     |  |

|-------------------------|---------------------|--|

| Signal                  | Meaning             |  |

| 2'b01                   | Next Picture        |  |

| 2'b10                   | Previous Picture    |  |

| 2'b11                   | <not used=""></not> |  |

| 2'b00                   | No Signal           |  |

Table 7: Clock Control Signals

Table 8: Picture Control Signals

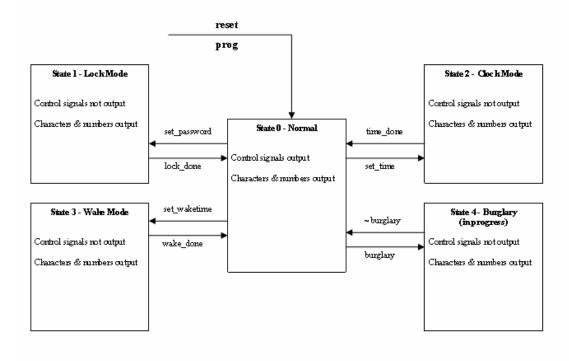

The final data output is state information. The signal processing module routes control commands, and part of that routing involves knowing when, and when not to send commands – specifically, that is the function of the FSM. As illustrated in Figure 2, the Signal Processing Module's FSM has five states: normal, lock mode, clock mode, wake mode and burglary. In each of these states, the command mapper is only allowed to send certain signals, and this state information is output to the display.

When in "normal mode," the command mapper routes all the signals as described above. However, if the FSM is in any other state, transmission of the control signals is blocked. It is important to successful operation of the Dorm Room Genie that while one is the process of programming either the password, system time, or wake time, that other control signals be withheld. When the user enters one such program mode summarized in Figure 2, the system will remain in that state until the corresponding module sends a "done" signal, releasing the semaphore.

A burglary is handled in a similar way. When the alarm module sends the burglary signal, the FSM locks the control commands such that the burglar cannot simply push "disarm". The FSM returns to normal mode following an alarm once the burglary module de-asserts the burglary signal. This process will be explained in the discussion of the burglary module.

## Signal Processor Finite State Machine: State Transition Diagram

Figure 2: Signal Processor's FSM

#### **Lock Module**

--By David Nedzel

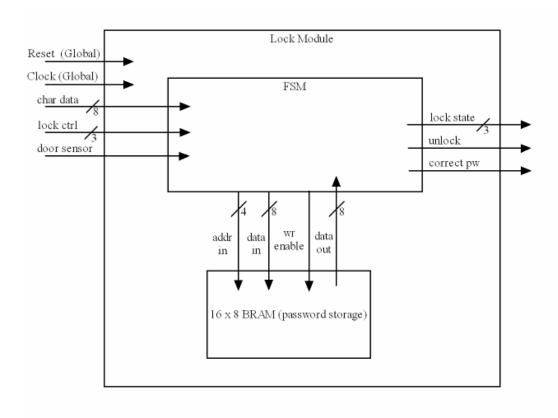

The two primary purposes of the lock module are to control whether or not an electric latch is unlocked, and to manage the user's password – both the storage of the password, and user authentication with the password. Each of the lock's primary subunits works toward those goals: a block RAM stores the user's password, while an FSM controls the electronic latch and user authentication. As illustrated in Figure 3, the lock module takes character data and control signals from the signal processing module and input from a magnetic door switch; it outputs its current state to the display, sends a control signal to unlock the door, and sends out a "correct password entered" signal when the user completes entering the current password.

Figure 3: Lock Module Block Diagram

I created the  $16 \times 8$  block RAM with the Xilinx Core Generation software. Each ASCII character in the password takes 8 bits to store, thus a user can have a password of up to sixteen characters. As I will explain, the FSM uses the data and control signals from the signal processing module and the door sensor to control both the reading and writing of the password storage RAM in addition to the unlock, correct password and lock state outputs. In using a magnetic door switch, with a digital system, I needed to design a way to hook up the magnetic switch to the lab kit. This turned out to be relatively simple. The 6.111 lab kit's user inputs accept voltage values of 3.3 V and 0 V as a logical "1" and "0". The magnetic sensor is simply a short circuit when the door is closed, and an open circuit when the door is open. Therefore, I hooked the lab kit's 3.3 V supply up to the user input across a  $10 \text{ k}\Omega$  resistor, and hooked the magnetic switch from 0 V to the user input. This when the door is open, the lab kit sees 3.3 V producing a logical "1", and when the door is closed, the 3.3 V is dropped a cross the resistor, and the lab kit sees 0 V producing a logical 0. With the magnetic sensor digitized, I set out to design the FSM.

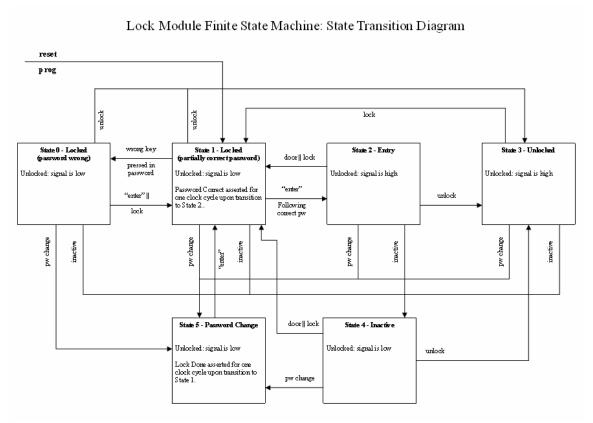

Figure 4: Lock Module FSM Diagram

As illustrated in Figure 4, the lock module has 6 states, but let us for the moment consider the four states "locked", "unlocked", "entry", and "inactive". When in any one of these states, the user can push "lock", "unlock" and "inactive" to transition to each of theses states. While locked, entering the correct code will transition the lock to the entry state. Once in entry state, the lock will remain unlocked until the door opens, at which point tit will re-lock itself. When inactive, the lock remains locked, but password entry is disabled – this mode would be useful to a user who has given out the code to a few close friends, but doesn't want them entering the room at a certain time. As a safeguard, if the door is opened while the lock is in inactive mode, the lock automatically returns to the locked state, preventing an accidental late-night lock-out after a visit to the bathroom.

The remaining two states deal with password entry and storage. When the lock receives a change password command, it allows the user to input a new password to be stored into the RAM. Since the lock module grabs the signal processors semaphore, it transmits a "lock done" signal to release the semaphore after the user pushes return to complete the password entry. The final state actually divides the "locked" state into two sub-states. As the user is entering a code for authentication purposes, each digit of the code is cross-referenced with the expected digit from the RAM. If the characters entered so far correctly correspond to the initial characters of the password, the FSM remains in "partially correct password" state. When the correct password has been entered, and the return key is pushed, the lock module outputs a "correct password" signal for one clock cycle before transitioning to the "entry" state. However, if the user makes a mistake at

any point during password entry, the FSM transitions to "password wrong state" – where the FSM will remain until the user completes entry of the wrong password by pressing return. It that point, the FSM returns to the "locked, partially correct password" state.

As eluded to earlier, the lock sends an "unlock signal" to the electronic latch, a done signal to release the signal processor's semaphore following a password change, a current state signal to the display, and a "correct password" signal to the burglar alarm module. Thus, the burglar alarm can be disarmed using the same password which unlocks the door. See the burglar alarm section for additional details.

## **Burglar Alarm Module**

--By David Nedzel

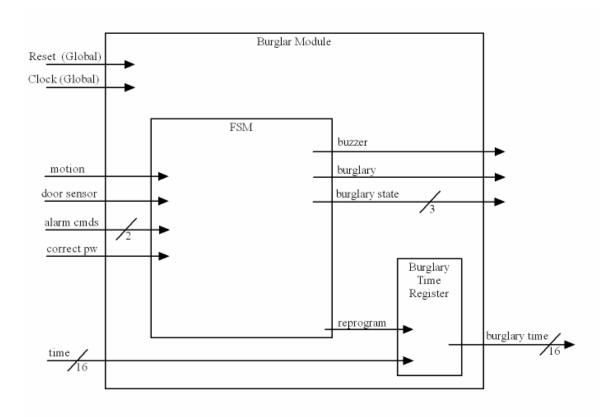

The burglar alarm module implements the primary means of security offered by the Dorm Room Genie. Its primary function is to trigger the "burglary" signal and sound an audible alarm when a burglary is detected. Like the lock module, the burglar alarm module receives control signals from the signal processing module, and users the magnetic door sensor. As shown in Figure 5, it also takes as input the current system time, the "correct password" signal from the lock module, and a "motion detected" signal from the video module. The burglar module outputs the burglary signal to many of the other modules in the system and sounds the alarm buzzer.

Figure 5: Burglar Alarm Module Block Diagram

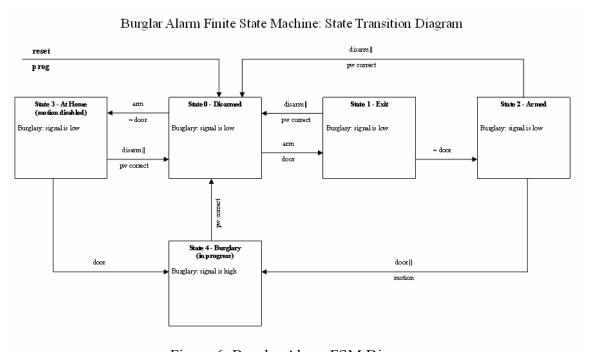

At the heart of the burglary module is an FSM which controls when and how an intrusion is detected. As illustrated in Figure 6, the FSM has 5 states: unarmed, exit, two armed states, and the burglary state. When in any state other than "burglary" a user can always press the disarm button to return the alarm to the disarmed state. No matter what state it is in, the alarm will always return to disarmed when the password is entered – the "password correct" signal generated by the lock module will disarm the burglar alarm. Note that this is the only way to disarm the system during a burglary.

The user can enable the alarm in two different modes. Often times, it is useful to enable the alarm while at home, in order to alert you while you sleep of a break in. This could be useful to a student who has friends that might try to pull a prank in the middle of the night. Obviously, if one is in the room, it would not be very useful to have the motion detector enabled since the alarm would sound as soon as you moved. Therefore, if you arm the system while the door is closed, the system activates without motion detection – only opening the door will trigger an alarm. Of course when leaving the room, the user would likely wish to enable motion detection. By arming the system while the door is open, the system transitions to "exit" mode. As soon as the door closes, the system will arm itself – now, either motion or opening the door will trigger an alarm.

Figure 6: Burglar Alarm FSM Diagram

When an alarm is triggered, the burglar alarm module activates the burglary signal and sounds the alarm buzzer – only entering the password will disable the alarm. The burglary signal is transmitted to nearly all other modules of the system – see the other module descriptions for information on how they react to this signal. The FSM also outputs its current state to the display module.

The burglar alarm module also has the capability to store the time at which a burglary occurs. Using the same 16-bit time format as the clock, the burglar alarm module store the current system time into a register (shown in Figure 5) each time the FSM transitions to burglary. This time is subsequently output to the display module.

#### **Time Division Modules**

-- By Aaron Stonely

The time division modules are responsible for creating the signals which drive the time-related elements of the Dorm Room Genie. The time division modules are comprised of the one hertz enable, one minute enable, and the one-sixtieth second enable modules. These time division modules are among the simplest of the modules used by the Controller Module. The time division modules take in as input a synchronized reset signal and the 27 megahertz system clock. The function of these modules is to take this signal and convert it into a signal of the appropriate length. For example, the one hertz enable module outputs an enable signal every 27 million clock cycles, which results in a second. Upon reaching the 27 millionth clock cycle, the counter resets to zero and the enable signal is disabled on the following clock cycle.

At the beginning of every clock cycle, the time division modules check to see if a reset has been asserted. If it has, the count is reset to zero, and the count begins incrementing again. If not, the time division modules continue by checking to see if the count has reached the specified value. If it has, the count is reset to zero, and the enable signal is asserted. If the count has not yet reached the specified value, the enable signal is held low, and the count is incremented. Table 9 contains a summary of the time division modules, their count, and their corresponding time value. The actual count value is one less than shown in the table, in order to account for the clock cycle delay for enable to be asserted high.

| Module         | Count Value  | Time Value        |

|----------------|--------------|-------------------|

| One_hz_enable  | 27 million   | 1 second          |

| One_min_enable | 1.62 billion | 1 minute          |

| Demo enable    | 500,000      | 1 sixtieth second |

Table 9

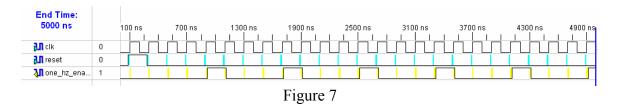

Figure 7 shows a timing diagram for a generic time division module. This particular timing diagram shows the behavior of a time division module that counts to three. In this case, the one\_hz\_enable count was temporarily set to three. This was done in order to demonstrate the behavior of the time division modules without having to simulate 27 million clock cycles in order to view a single enable signal. From the timing

diagram, it is clear that the enable signal is asserted on the fourth clock cycle instead of the third. This is a significant delay when the time division module is counting to three, but when it counts to values used in this lab, the introduction of an extra clock cycle delay has a negligible effect. However, as noted, in order to account for the extra clock cycle delay, the modules count to a value that is one less than that specified in Table 9.

#### **Clock Module**

#### -- By Aaron Stonely

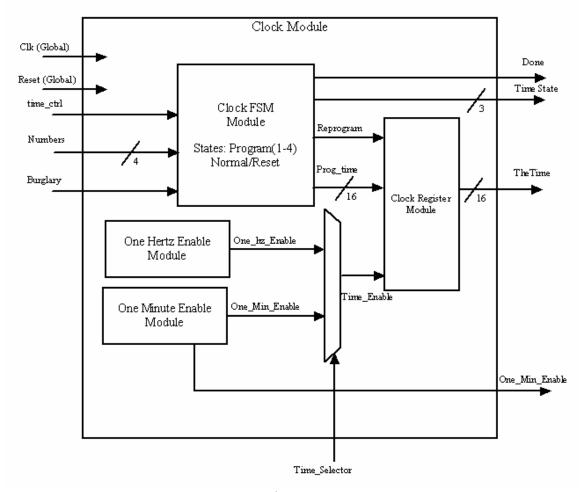

The clock module is responsible for keeping the system time. The time it outputs is used by several other modules throughout the system in order to implement functionality that depends on the current time. The clock module takes in as input the 27 megahertz system clock, the synchronized reset, a time control signal and numbers from the signal processor module, a time selector signal from the user, and a burglary signal from the burglary module. The clock module takes these signals and then outputs its current state, the system time, and a one minute enable signal to be used by other modules. Figure 8 shows the organization of the clock module.

Figure 8

The clock module implements the basic functionality of a digital clock. Under normal operation, the clock module outputs the current time, and updates it when either one minute, or one second has elapsed as specified by the user. The format for the time used by the dorm room genie is twenty-four hour time, displayed as 4 hex numbers. At any time, the user can request to reprogram the current time. The user does this by first making a reprogram request, and then by specifying four valid numbers for the time to be programmed. The clock module is divided into three major sections which include the Clock Finite State Machine (FSM) section, the time keeper module section, and the time enable section.

The simplest of these sections is the time enable section. This section includes an instance of the one minute enable module and the one hertz enable module. The output of the one minute enable module is output from the clock module so that it may be used by other modules within the Controller module. The purpose of this section is to allow the user to choose whether the system keeps time in minutes or seconds. This function is primarily intended for demonstration purposes because it allows other functionality in the Dorm room genie to be demonstrated in less time than normal operation would require. For example, the wake-up lighting sequence takes place over fifteen minutes, and would be difficult to demonstrate in a short period of time unless this option were present. The time mode specified by the user is then output to the time keeper section as a time\_enable signal.

The second section of the clock module comprises the clock register module. This module is basically a large register containing the system time, with some additional logic in order to increment the system time. The clock register takes in as input the global clock and reset, a reprogram signal from the clock finite state machine (FSM), a time enable signal as described previously, and the time to be programmed. The clock register uses these outputs to determine the current system time as well as the next time to be displayed. The largest portion of this module was dedicated to determining the next time to be displayed. This involved the conversion of the time enable signals and the current time into the system time which is displayed as 4 hexadecimal numbers. The system time is reprogrammed upon request from the clock FSM. If the clock register receives a reprogram signal from the clock FSM, the current reprogram time output from the FSM becomes the system time which is output from the clock module.

The third and final section in the clock module contains the clock finite state machine (FSM). The clock FSM takes in as input the global 27 megahertz clock, the synchronized reset, the time control and the 4-bit hex numbers from the signal processor module, and a burglary signal from the burglary module. The clock FSM directs the operation of the clock module. It controls the current state of the clock system as well as the programming sequence. The clock FSM has five states. The first state is the normal operating state. In this state, the FSM does not assert the reprogram signal, and the clock register module is allowed to keep the current system time as normal. Upon a reprogram request from the user, the FSM enters the program sequence. The programming sequence consists of the remaining states of the FSM, which are program 1-4. In the program 1

state, the clock FSM is waiting for the user to input the first number of the time to be programmed. In the program 2 state, the clock FSM waits for the user to input the second number of the time to be programmed, and the program 3-4 states continue this pattern. During a transition from the program four state to the normal operating state, which occurs after a successful reprogram, the clock FSM asserts a done signal, which is output from the clock module. This signal is used to let the signal processor module know that a programming sequence has been completed. One last thing of note is the function of the burglary input. During a burglary, the keyboard exits a reprogram sequence and enters a dedicated password entry sequence. If the user is in the middle of a reprogram sequence and burglary is asserted, the FSM immediately exits the reprogram sequence and returns to the normal operating state with the current time left unchanged.

Figure 9

Figure 9 shows a timing diagram of the clock module. As shown in figure 9, the current time (labeled 'thetime') is displayed as a 4 digit hexadecimal number. Time\_ctrl is the user input and when asserted high, represents a request to reprogram the current time. A reprogram sequence is also shown, in which the current time is reprogrammed to 17:58 versus the old time of 00:04. After the program sequence is completed, the done signal is asserted, and the current time becomes the programmed time. Finally, the function of the time selector is also demonstrated. Before the time selector was asserted, the time was being updated every six clock cycles. After the time selector was asserted, the time was updated every four clock cycles. This corresponds to the one\_minute\_enable count being reprogrammed to 5 clock cycles and the one\_hz\_enable count being reprogrammed to 3 clock cycles. The extra clock cycle delay is due to the clock cycle delay introduced by the clock register module updating the time.

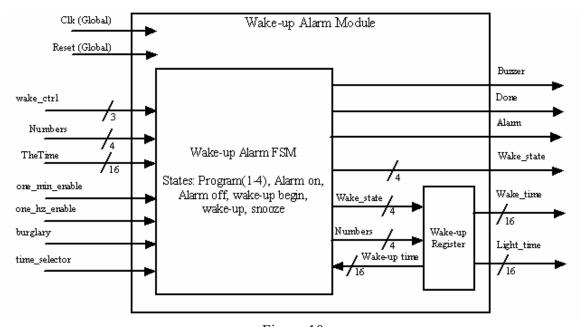

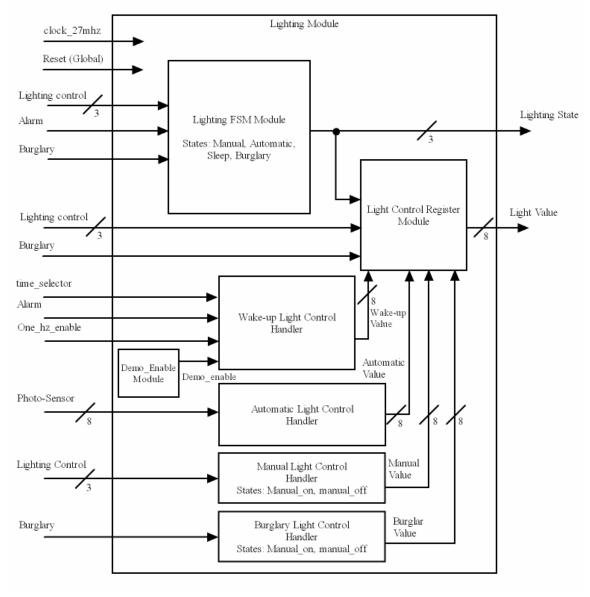

## Wake-up Alarm Module

-- By Aaron Stonely

The wake-up alarm module will implement additional functionality to the clock module. The alarm clock module allows the user to set a wake-up time and to be gently awoken by light, even if their curtains are closed. If the user fails to acknowledge the wake-up sequence, the wake-up alarm will sound a buzzer in short bursts in order to guarantee that the student will wake up. The wake-up module takes in as input the 27 megahertz system clock, the synchronized reset, a wake control signal and hexadecimal number from the signal processor module, the current time, a one minute enable signal, a one hertz enable signal, a burglary signal, and a time selector signal from the user. The

wake-up module outputs the current value of the wake-up time, a corresponding light time to be used by the lighting module, the current state of the wake-up module, a buzzer signal, a done signal, and an alarm signal.

The user interacts with the wake-up alarm module through the keyboard and the signal processor module. There are four user commands, and they include alarm on, alarm off, snooze, and set wake-up time. The user must first set the time they wish to wake-up at. After setting the wake-up time, the wake-up alarm is still inactive. The user can then choose to turn the alarm on or leave the alarm in its off state. If the user activates the alarm, the wake-up alarm module waits until the current time is within fifteen minutes of the programmed wake-up time. It is at this time that the wake-up sequence begins, and the lighting module is signaled to begin lighting through the alarm signal. As soon as the wake-up sequence begins, the user is able to snooze the wake-up alarm. This turns off the lights and gives the user another fifteen minutes of sleep. Once the current time reaches the wake-up time, the buzzer begins to sound for one second, every other second. This is a loud buzzer, and is intended to ensure the user will wake up and not sleep through an important deadline. The organization of the wake-up module is shown in figure 10.

Figure 10

The wake-up alarm module is split into two major sections. These sections are the wake-up alarm finite state machine (FSM) and the wake-up alarm register. The wake-up alarm register stores the most recently programmed wake-up time. During a reprogram, the register stores the number input from the user into the appropriate slot in the wake-up time. The wake-up register then outputs a wake-up time which is used to calculate the wake-up time. Most of the work for this part consisted of creating the logic needed to calculate the value of the wake-up time minus fifteen minutes in twenty-four hour hexadecimal format used. Once calculated, this value is output as the light time.

The second and largest section of the wake-up alarm module is the wake-up alarm finite state machine (FSM). The FSM is responsible for implementing the various functions of the wake-up alarm. It takes uses the current state and the current time to determine whether the alarm should be going off. The wake-up alarm module has several states. These states include the normal operating or 'off' state, the program 1-4 states, the "alarm on" state, the "wake-up sequence begin" state, the "wake-up active state", and the "snooze" state. Transitions between these states are governed by the user inputs from the signal processor module, which include no input, the "alarm on", "alarm off" "snooze" and "set wake-time" commands.

During the normal or "alarm off" state, the alarm will not go off. Instead, the wake-up module simply stores the last wake-up time value programmed by the user. If the user inputs a "set wake-time" command from the signal processor module, the wake-up alarm finite state machine (FSM) transitions to the program 1 state. In this state, the FSM waits for the user to input a valid number for the first number in the wake-up time to be programmed. Program states 1-4 all follow this pattern, just as in the clock module. Once the last valid number is programmed in the wake-up time by the user, the FSM asserts the done signal so that the signal processor module knows that a successful reprogram sequence has terminated. Once again, if the burglar signal has been activated during a program sequence, then the FSM aborts the programming sequence and returns to the default or "alarm off" state.

If the user issues an "alarm on" command from the signal processor module, the wake-up finite state machine (FSM) then transitions to the "alarm on" state. In this state, the user can turn off the alarm or choose to reprogram the wake-up time, both of which eventually leave the FSM in the "alarm off" state. While in the "alarm on" state, two types of behavior may be observed. If the current time is less than fifteen minutes from the programmed wake-up time when the user turns the alarm on, then the interval is too short for a lighting wake-up, and instead only the buzzer will be used to wake-up the user.

If when the user turns the alarm on, the current time is more than fifteen minutes from the programmed wake-up time, then the user has the option to wake-up to a lighting sequence, which is selected by the user in the lighting module. In this case, once the time reaches the time for the lighting sequence to begin, the wake-up module finite state machine (FSM) transitions to the "wake-up sequence begin" state. Without input from the user, the FSM will remain in this state until the current time reaches the user-programmed wake-up time. Once the wake-up time is reached, the FSM enters the "alarm active" state. While in the "wake-up sequence begin state", the user has the option of turning the alarm off or pressing the snooze command. If the user turns the alarm off, the lights will turn off, and the alarm will be deactivated. If the user chooses to snooze, the alarm will give the user another fifteen minutes before the FSM transitions to the alarm active state. In addition to halting the lighting sequence, the lights are turned off since a snooze request during the wake-up sequence demonstrates that the user does not want the lights on. If the dorm room genie is in demonstration mode (shorter time intervals) then the snooze only lasts for duration of fifteen seconds.

When in the "alarm active" state, the wake-up module finite state machine (FSM) is sounding the buzzer. The buzzer is activated for duration of one second every other second in order to ensure the user wakes up and acknowledges the alarm. When in this state, the user may choose to turn the alarm off, or snooze the alarm. If the user commands the alarm off, the alarm will transition to the "alarm off" state, and the buzzer will stop sounding. If the user commands the alarm to snooze, then the lights will once again shut off, and the user will get another fifteen minutes to sleep before the alarm becomes active once again and the buzzer starts sounding. Once again, if the dorm room genie is in demonstration mode, the snooze will only last fifteen seconds.

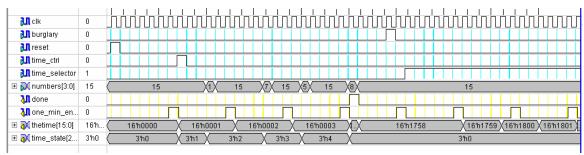

Figure 11

Figure 11 contains the timing diagram of the wake-up alarm module. Wake\_ctrl is the user input from the signal processor module. A value of 4 represents a reprogram request, a value of 1 represents an "alarm on" request, a value of 2 represents an "alarm off" request, and a value of 3 represents a snooze request. As shown, the wake-up time is update as the user puts the numbers in. Since the time is static and does not change as the user inputs a new time to be programmed, there was no need to delay the reprogram, so the wake-up time is updated as the inputs are received. Note how alarm is asserted once the current time reaches the programmed wake-up time and again when the user turns the alarm off. This is used to tell the lighting module when a lighting sequence should begin, and when the lighting sequence should be terminated.

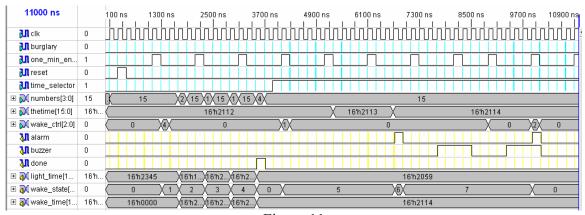

# **Lighting Module**

-- By Aaron Stonely

The lighting control module is designed to give the user even greater control of their dorm room. The lighting module adds another level of functionality to the wake-up alarm, as well as three other modes of functionality. The lighting module takes in as input the 27 megahertz system clock, the synchronized reset, lighting control commands from the signal processor module, the alarm signal from the wake-up module, the burglary signal from the burglary module, the time selector input from the user, a one hertz enable signal, a demo enable signal, and photo-sensor data containing the ambient lighting

value. The lighting module outputs the lighting module state, and the lighting value. The lighting value is an 8-bit number as is used to represent a lighting value when converted using a DAC0831 digital audio converter chip.

The lighting module has four operating modes which include "manual mode", "automatic mode", "sleep mode", and "burglary mode". In "manual" mode, the user can manually adjust the lighting level. This includes the ability to turn the lights on and off, as well as the ability to brighten or dim the lights. This implementation allows eight discrete lighting levels which the user can select between using the brighten and dim commands. In "automatic" mode, the light intensity is controlled by the level of ambient light as determined by a photo-sensor and the ADC0841 inputs. This lets the system adjust the lights in order to maintain a certain level of brightness. When in "sleep" mode, the lighting module works with the wake-up module in order to wake up the user with a lighting sequence. Finally, when a burglary occurs, the lighting module enter "burglary" mode which flashes the lights on and off in order to attract additional attention to the burglar with the goal of deterring theft. Figure 12 shows the organization of the lighting module.

Figure 12

The lighting controller is divided into five major sections. These include the wake-up, automatic, manual, and burglary light control handlers, the light control register, and the lighting finite state machine (FSM). The user interacts with the lighting module through the keyboard control commands which come from the signal processing module. These commands include no input, 'off', 'on', 'automatic', 'brighten', 'dim', and 'sleep'.

## Lighting Module Finite State Machine

The lighting module finite state machine (FSM) interprets the user command inputs, and uses these to maintain the state of the lighting module, which in turn

determines which lighting value is selected to be output to the rest of the system. The lighting module FSM has four states. These states include the 'manual', 'automatic', 'sleep', and the 'burglary' operating state. Transitions between these states are fairly straightforward. For example, if the FSM is in any other state than manual, if the user inputs a manual command such as 'on', 'off', 'dim', or 'brighten', the FSM transitions to the 'manual' state. Once in the 'manual' state, the FSM remains there until the user issues a non-manual command. The user can transition between the 'manual', 'automatic', and 'sleep' states (or modes), at any time with the corresponding user command. The FSM only enters the burglary state during an active burglary. Once the burglary is over, the FSM transitions to the reset or 'manual' operating state.

# Wake-up Light Control Handler

The wake-up light control handler is responsible for implementing the additional functionality associated with the wake-up alarm. Once the time has approached fifteen minutes before the programmed wake-up time, the wake-up module signals the light control module to begin the wake-up sequence. As described earlier in the wake-up module, the user has the option of making the sequence begin fifteen seconds before the programmed wake-up time. The start of the wake-up sequence causes the lighting control module to use the lighting value provided by the wake-up control handler.

At the beginning of the sequence, the lights are off. The lighting module then gradually increments the lighting value so that the lighting level is its maximum value as the time reaches the programmed wake-up time. This is done by incrementing the lighting value by one every three time units until the maximum value of 255 is achieved. The wake-up handler uses a sub-module called demo enable. The demo enable module takes in the system clock and the reset and outputs an enable signal once every sixtieth of a second. This module is needed in order to properly demonstrate the lighting sequence when in demonstration mode (minutes lasting one second). When not in demonstration mode, the lighting sequence lasts fifteen minutes instead of fifteen seconds. During a lighting sequence, the user may choose to snooze or shut off the wake-up alarm. If the user does so, the wake-up alarm module asserts the alarm signal, and the wake-up light control handler aborts the lighting sequence and shuts off the lights.

#### Automatic Light Control Handler

The automatic lighting control functionality is designed to handle the lighting for the user without the user having to adjust it as the room gets lighter or darker. The automatic light control handler does this through the use of the light sensor which outputs a voltage that is converted to an 8-bit number through the use of the ADC0841. The automatic light control handler then interprets this lighting value and adjusts the lighting level accordingly. Due to the properties of the lighting sensor, a lighting threshold was set for about half of the 8-bit light range. This is because the user would likely want the lighting at full intensity even if it wasn't pitch black in the room. When the light level falls below this threshold, the lights are set to full intensity. Otherwise, the lighting value is set to the maximum lighting value minus the level of ambient light in the room. This

results in the behavior that when the room gets brighter, the lights dim, until eventually they aren't visible.

## Manual Light Control Handler

The manual light control handler is responsible for implementing the on, off, brighten, and darken command functionality. The manual light control handler is basically a register for the manual lighting value with additional logic. The manual control handler stores the current value of the lighting, and allows the user to turn the lights off to the minimum intensity, on to the maximum intensity, and uses brighten or dim to reach the six other lighting intensities in between. The on and off command implementations are fairly straightforward and simply adjust the lighting to the value 0 or 255, which correspond to the minimum and maximum lighting intensities respectively. The brighten and darken commands increase and decrease the lighting value by 32 so that there are 8 discrete lighting values. This is because many lighting values are virtually indistinguishable, so 8 discrete lighting values allows a good amount of user control while maintaining discernable lighting levels. When in manual mode, the resulting manual lighting value is output as the lighting value from the lighting module.

## Burglary Light Control Handler

The burglary control handler takes care of the behavior associated with a burglary in progress. When there is a suspected burglary in progress, the lighting control FSM transitions to burglary mode, and the lighting value output from the burglary light control handler is used as the output from the light controller module. During a burglary in progress, the lights flash on and off for one second duration every two seconds. This means that the lighting value will change between 0 and 255 when the lights flash off and on respectively.

#### Light Control Register

The light control register determines which of the handler's lighting values is output as the lighting value of the system. The light control register takes in the current state of the lighting finite state machine, and selects the output that corresponds to the current state or mode of operation.

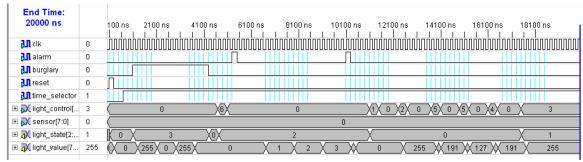

Figure 13

Figure 13 shows the timing diagram of the light control system. Displayed are the burglary, automatic, wake-up, and manual modes of operation. The result is shown as light\_value which ranges from 0 to 255 corresponding to the minimum and maximum lighting intensities respectively.

# **Display Module**

-- By Aaron Stonely

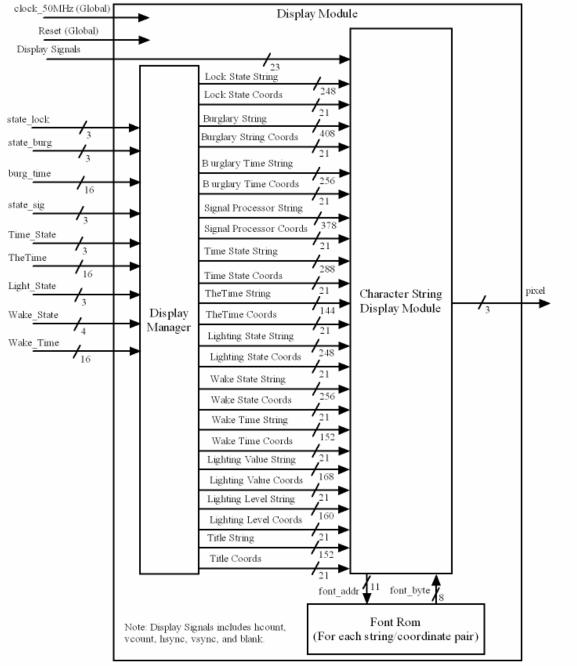

The lighting module is responsible for displaying the status of the entire controller system. This allows the user to see what settings are in place and what module they are currently sending input to. The display module takes in as the 57 megahertz system clock, the synchronized reset, the system time from the clock module, the burglary time from the burglary module, the wake-up time from the wake-up module, vocunt and hocunt from the video module, the light value from the lighting module, and the states of the clock, signal processor, burglary, lock, wake-up, and lighting modules. For all these inputs, the display module only outputs a 3-bit wide pixel value which corresponds to the values of the hocunt and vocunt inputs.

First, all the inputs to the display module are synchronized with the system clock using the synchronize module provided by the 6.111 course staff. This is necessary because the inputs are coming from the modules which are operating at 27 megahertz. One the inputs pass through the synchronizer module, they are now ready to be used by the logic operating at 50 megahertz. Next, the inputs are then used by logic in order to determine the display.

The display module makes heavy use of the character string display module provided by the 6.111 course staff. One instance of character string display module and its corresponding font rom was created for each line of text that was displayed. For each status line in the display module, logic was created in order to generate the string to be displayed according to the value of the input. Once the string was generated, an instance of the character string display module was created which would use this string to create a pixel value for the appropriate values of hount and vocunt. The generated pixel would have a 3-bit value of 111 when the hount and vocunt fell within a letter in the string, and a 3-bit value of 000 when hount and vocunt were outside of the display window. Each instance of the character display module had a specified coordinate on the display string. so that the information could be organized, and displayed without text overlapping. The character string display module provided by the 6.111 course staff was slightly altered so that it would support the pipelining of pixels which will be described further in the testing and debugging section. Once the pixel is output from the character display module, it again passes through a register in order to pipeline the logic associated with the pixel. The organization of the display module is in figure 14.

Figure 14

The number of bits in each string varies since it depends on the length of the string that is displayed for a given input. Each display string also has an associated set of coordinates which are used to determine the position of the string on the display screen. Tables 10 and 11 contain a list of all the display outputs for each corresponding input and their relative position on the screen. The display module is designed to display all the text on a screen resolution of  $640 \times 480$ .

| Display Item           | Associated Strings                                                                                     |  |

|------------------------|--------------------------------------------------------------------------------------------------------|--|

| Title                  | "The Dorm Room Genie"                                                                                  |  |

| System Time            | "System Time: (HH:MM)"                                                                                 |  |

| System Time State      | "System clock is in operational mode."                                                                 |  |

|                        | "Please program the current time."                                                                     |  |

| Wake-up Time           | "Wake-up Time: (HH:MM)"                                                                                |  |

| Wake-up State          | "Wake-up Alarm is off."                                                                                |  |

| 1                      | "Please program the wake-up time."                                                                     |  |

|                        | "The wake-up alarm is on."                                                                             |  |

|                        | "The wake-up sequence has begun." "Time to wake up!!"                                                  |  |

|                        |                                                                                                        |  |

|                        | "Alarm is in snooze mode."                                                                             |  |

| Signal Processor State | "System is in normal operating mode."                                                                  |  |

|                        | "The clock module is waiting for input."                                                               |  |

|                        | "The wake-up module is waiting for input."                                                             |  |

|                        | "Burglary in progress! Enter password to                                                               |  |

|                        | disarm."                                                                                               |  |

| Lock State             | "The door is locked."                                                                                  |  |

|                        | ""Please enter."                                                                                       |  |

|                        | "The door is unlocked."                                                                                |  |

|                        | "Keyless entry is inactive."                                                                           |  |

|                        | "Please enter your new password."                                                                      |  |

| Burglary State         | "Burglar alarm is disarmed." "Burglar alarm is in standby: Please exit now." "Burglar alarm is armed." |  |

|                        |                                                                                                        |  |

|                        |                                                                                                        |  |

|                        |                                                                                                        |  |

|                        | "Burglar alarm is armed. (Motion detection                                                             |  |

|                        | disabled.)"                                                                                            |  |

|                        | "Burglary in progress!!"                                                                               |  |

| Burglary Time          | "A burglary has not occurred."                                                                         |  |

|                        | "A burglary occurred at: (HH:MM)"                                                                      |  |

| Light State            | "Lighting is in manual mode." "Lighting is in automatic mode." "Lighting is in sleep mode."            |  |

|                        |                                                                                                        |  |

|                        |                                                                                                        |  |

| 7:1.771                | "Intruder alert! Intruder alert!"                                                                      |  |

| Light Value            | "Light value: (8-bit binary number)"                                                                   |  |

| Light Level            | "Light Level: 7 (Max)"                                                                                 |  |

|                        | "Light Level: (1-6)"                                                                                   |  |

|                        | "Lights are off."                                                                                      |  |

Table 10

| Display Item           | Inputs            | (Horizontal, Vertical) |

|------------------------|-------------------|------------------------|

|                        |                   | Coordinates            |

| Title                  | N/A               | (248, 20)              |

| System Time            | [15:0] TheTime    | (100,260)              |

| System Time State      | [2:0] Time_state  | (100,280)              |

| Wake-up Time           | [15:0] wake_time  | (100,300)              |

| Wake-up Time State     | [3:0] Wake_state  | (100,320)              |

| Signal Processor State | [2:0] state_sig   | (100,60)               |

| Lock State             | [2:0] state_lock  | (100,100)              |

| Burglary State         | [2:0] state_burg  | (100,160)              |

| Burglary Time          | [15:0] burg_time  | (100,180)              |

| Light State            | [2:0] light_state | (100,400)              |

| Light Value            | [7:0] light_value | (100,420)              |

| Light Level            | [7:0] light_value | (100,444)              |

Table 11

## **Video/Motion Module**

--By David Nedzel

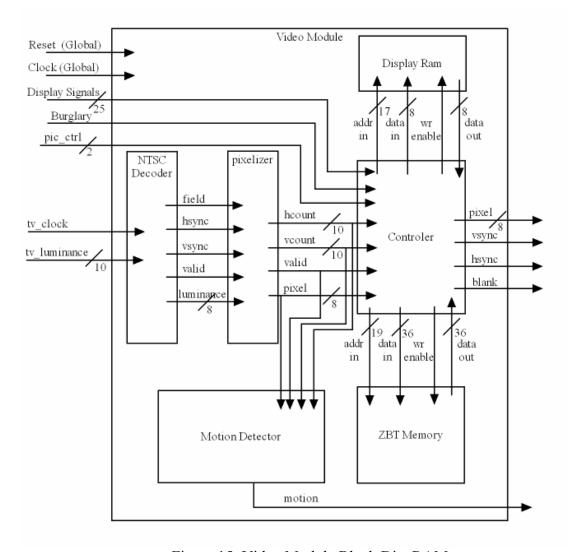

The most complicated of all the modules of the Dorm Room Genie, the video module is responsible for sensing motion in the room, capturing images of the burglary, and displaying them back upon request. As shown in Figure 15, the video module makes use of several labkit features. In explaining the functionality of the video module, I will follow the track of the video signal from camera input to display output.

Figure 15: Video Module Block DiagRAM

When the tv clock and luminance data first enter the video module, the pass through the 6.111 provided NTSC Decoder and are transformed into field, horizontal and vertical sync signals, luminance values, and a valid signal. In order for these signals to be used effectively, they must be further transformed to indexed pixels. The pixilizer, a modified version of some 6.111 sample code performs this function. The pixilizer interprets the fvh and valid signals to select the upper left 320x240 pixels in the camera's field of view. I choosing the resolution of the snapshots, there were several considerations. First, they had to be sharp enough, to ensure that you would probably be able to identify the burglar. Second, they had to be small enough so that several could be stored in memory as a record of what happened during a specific time period. By using grayscale video and reducing the image resolution to 320x240 we can reasonably balance these two conflicting objectives. Once the pixels have been indexed, they are sent to both the motion detector unit, and the video capture and playback unit.

The purpose of the video capture and playback unit is to make a record of the burglary so that the user might learn who is responsible for missing items, or how the event happened. Having settled on 320x240 resolution, it was a simple matter to calculate how many images the ZBT memory could store. Having  $2^19$  indexes of 36 pixels each, there is enough room to store  $(2^19)/4 = 2^17$  pixels, since each pixel has eight bits of luminance data. Each 320x240 image is 76,800 pixels, or 19200 index slots of the ZBT.  $(2^19)$  index slots 19,200 index slots per image 27 images. By capturing these images every two seconds, we can document roughly the first minute of the intrusion.

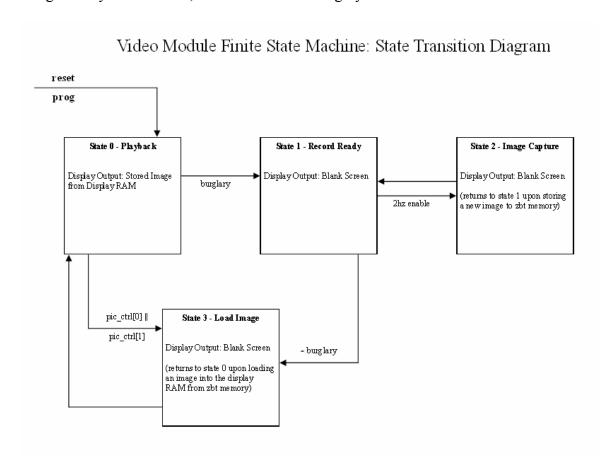

Figure 16: Video Module FSM DiagRAM

After the burglary ends, the controller then pulls an image out of the ZBT memory and loads it into the display RAM for display on the monitor. One of the complicated design elements of this module is that the components are clocked at 27MHz, except for the display RAM and video signals which are clocked at 50MHz. The still image is displayed on the monitor until the user requests the next image. Like many of the other modules, the video capture module uses an FSM to manage its actions. As illustrated in Figure 16, the FSM has four states: playback, record ready, image capture and load image. Driving the FSM to change states are the burglary signal from the burglar alarm module, the picture control signal from the signal-processing module, and 2 second enable signal created by a clock divider. While in playback mode, the user can request a new image by pushing next/previous picture. The FSM transitions to load to

load the requested picture into the display RAM. Once the picture has been loaded, the FSM transitions back to playback mode. When a burglary occurs, the FSM transitions to "record ready." Then, so long as there is sill memory space available, the FSM transitions to "image capture" every two seconds to store an image into the ZBT, and then immediately back to "record ready". Once the burglary ends, the FSM transitions to load, and finally back to playback.

The final component to the video module is the motion detector. In principle, as an object moves from location to location in a picture, the average luminosity of pixels in a particular area should change as that object moves. The motion detector attempts to leverage that principle by averaging the luminosity of groups of pictures, and looking for deviations in those averages.

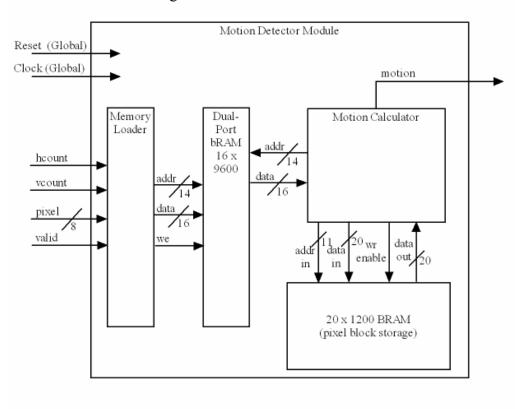

Figure 17: Motion Detector Block DiagRAM

As illustrated in Figure 17, the motion detector takes indexed pixels as input. The memory loader sums rows of eight pixels and stores them into the dual port RAM. Then the motion calculator sums adjacent rows, such that it then stores luminosity sum of an 8x8 pixel grid. Finally, as the motion calculator is updating pixels averages in the pixel-block RAM, it measures the amount of change. If that change is above a certain threshold, the module signals that motion has been detected. This threshold would be found experimentally after successfully implementing the pixel averaging functions.

#### **Labkit Module**

--By David Nedzel and Aaron Stonely

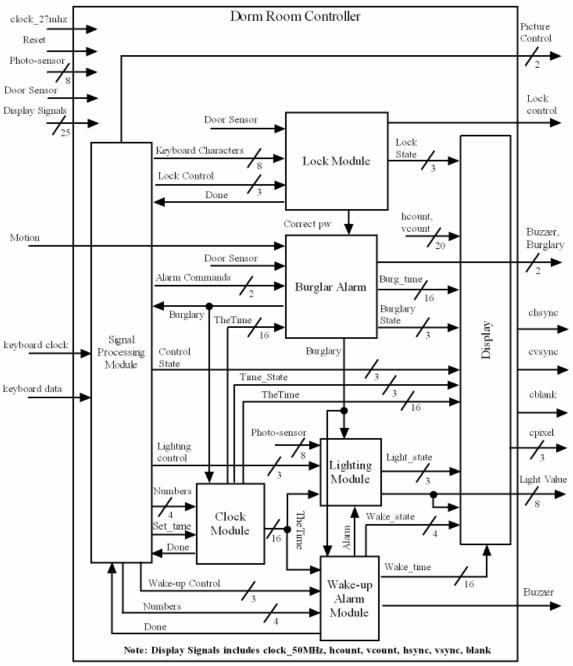

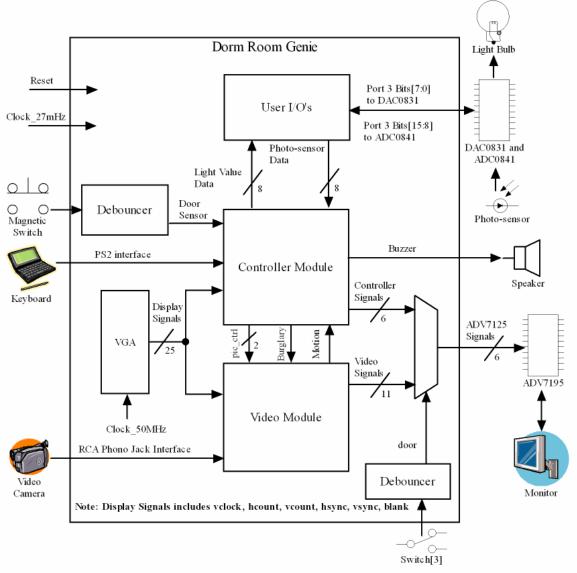

The labkit module is the top level file in the Dorm Room Genie. The labkit file contains both the entire controller module and the video modules that are used to display the status of the system, as well as capturing a snapshot of the burglar. The purpose of this module is to create an instance of each of the sub-modules described and wire them up together. The labkit module acts as a bridge between the 6.111 FPGA labkit hardware and the verilog implementations in the sub-modules. Here, all the user inputs are assigned to switches, buttons, and the user I/O's. Also, the outputs sent through the user I/O's and the LED displays are assigned. All of the user inputs are synchronized to the system clock and debounced so that they may be used by the modules. The labkit also contains the code provided which creates and assigns the video signals which are used by our displays. Figures 18 and 19 show the organization of the labkit.v file and all of the modules declared within it.

Figure 18

Figure 19

### **Testing and Debugging**

## Section by Aaron Stonely

As is almost always the case, the implementation of my modules did not work perfectly the first time. In fact, testing and debugging of the modules both individually and together took a substantial amount of the total project time. The testing and debugging of the modules took place in several steps. First, each module was debugged for syntax errors. This was usually the simplest step because the Xilinx ISE debugger is very good at identifying typos and other common mistakes. Next, once the modules correctly compiled, I simulated each module using the Xilinx ISE/Modelsim waveform simulators. This step involved testing all of the possible cases for input in order to determine correct functionality. Once each individual module passed this step, I next

proceeded to wire them up according to the layout presented in figures 9 and 10. After the modules were wired up and they passed the syntax and compilation steps, the next step would ordinarily have been to test the labkit file in the waveform simulators. Unfortunately however, since the labkit contains so many inputs and outputs, waveform simulations are often not helpful as simulation errors occur frequently, and simulation data becomes complex an intractable. The following step involved generating the program file. Once the modules passed this test, the next step was to program the modules onto the FPGA. Once the FPGA was programmed, the most difficult part of the debugging process began. The process of understanding what was happening on the outputs and why involved many stages of trial and error. Common debugging tools such as displaying a value on the LED's became invaluable in gaining insight into the operation of the system. Below, the testing and debugging of each of the modules is described in greater detail.

# Clock and Wake-up Alarm Modules

As expected, these modules did not work perfectly the first time; however, the debugging of these modules was relatively simple when compared to other modules. This was because all of the behavior of these modules could be easily simulated using the Xilinx ISE/Modelsim waveform simulators. Most of the issues I had with these two modules involved the calculations of the current time, the next time, and the light time. The format chosen for use in the Dorm Room Genie was twenty-four hour time and the format was 4 hexadecimal numbers. While this format was particularly simply to display and program from the keyboard, it made calculating times difficult. This was because each digit was to be treated individually in order to keep it in 4 hexadecimal number format. Thus, the logic to keep time, or subtract 15 minutes for the lighting time was not straightforward and involved careful thought. This also meant that I did not get the formulas right the first time. In order to guarantee their functionality, I had to careful test and simulate all fringe cases for the time in order to ensure that there were no bugs. After several adjustments to the calculations, and some debugging of state transitions, the modules passed the simulation. Since the simulation was very effective in catching the behavior of these modules, further testing during the integration stage was minimal and only involved a few minor adjustments to make my modules compatible with my partner's.

## Lighting Module

As with the clock and wake-up alarm modules, testing and debugging for the module itself was relatively straightforward. Use of the Xilinx ISE debugged and the Modelsim waveform simulators were helpful in determining what bugs were present, and the correction for the bugs found were relatively straightforward. As a result of the extensive simulation testing, the integration of the lighting module itself was relatively simple and only ran into a few minor compatibility issues which were quickly resolved.

The biggest problem I ran into with the lighting module involved the automatic wake-up feature. This is because it involved analog devices which were hooked up to the

FPGA user I/O pins. Both the light value to light voltage and ambient light voltage to ambient light value stages were particularly difficult, and as a result, not all of the functionality desired in the plan was completed.

The lighting module outputs an 8-bit number corresponding to a lighting value which was supposed to be converted into a voltage and displayed on the light bulb. After several hours, a couple fried chips, and two minor burns later, I was able to successfully hook up the output from the FPGA user I/O's to the DAC0831 which converted the binary light value into a current which was then converted into a voltage using a transimpedance amplifier. Once I obtained a working light voltage from the light values, I was pleased with the result, but not for long. This is because upon hooking up the light bulb to the output voltage of the op amp, the voltage at the output would disappear! After another couple hours spent trying to debug this, I finally went downstairs to the 6.002 lab and determined that the resistance of the light bulb was four ohms which effectively made it a short, which explained the loss of voltage at the output of the op amp as well as the fried op amp and my burnt finger. After trying several strategies, including a voltage buffer op amp, I was unable to find a solution for how to place a voltage of five volts across a four ohm resistor. The result was that while I was able to demonstrate the voltage on the oscilloscope, I was unable to demonstrate the lighting of the light bulb as desired.

The second aspect of the automatic lighting mode also presented considerable difficulty and was ultimately left for future work. This part involved obtaining a lighting value from a lighting sensor. For this part of the project, I purchased two sensors from DigiKey which seemed to be exactly what I wanted. I found all of the specs to be what I wanted, except for the minor detail that the sensors were a few millimeters large. My partner and I spent considerable time trying to solder the small sensors so that they could be used in our project, but we were ultimately unsuccessful when in the process of soldering, the contacts were ripped off the sensors. The next idea for sensing the lighting value involved the luminance data which could be calculated using the camera and functionality to be implemented by my partner. My partner will describe this debugging process in greater detail; however the ultimate result was that we were unable to obtain the luminance data from the camera as we had hoped to do. This resulted in our inability to sense the lighting level and thus, the automatic functionality was never fully implemented.

## Display Module