# 6.111 Lecture 12

#### Today: <u>Arithmetic: Addition & Subtraction</u>

Binary representation

Addition and subtraction

Speed: Ripple-Carry

Carry-bypass adder

Carry-lookahead adder

#### Acknowledgements:

- R. Katz, "Contemporary Logic Design", Addison Wesley Publishing Company, Reading, MA, 1993. (Chapter 5)

- J. Rabaey, A. Chandrakasan, B. Nikolic, "Digital Integrated Circuits: A Design Perspective" Prentice Hall, 2003.

- Kevin Atkinson, Alice Wang, Rex Min

#### Arithmetic Circuits

## 1. Binary Representation of Numbers

#### How to represent negative numbers?

- Three common schemes:

- sign-magnitude, ones complement, twos complement

- <u>Sign-magnitude</u>: MSB = 0 for positive, 1 for negative

- Range:  $-(2^{N-1}-1)$  to  $+(2^{N-1}-1)$

- Two representations for zero: 0000... & 1000...

- Simple multiplication but complicated addition/subtraction

- <u>Ones complement</u>: if N is positive then its negative is N

- Example: 0111 = 7, 1000 = -7

- Range:  $-(2^{N-1} 1)$  to  $+(2^{N-1} 1)$

- Two representations for zero: 0000... & 1111...

- Subtraction is addition followed by ones complement

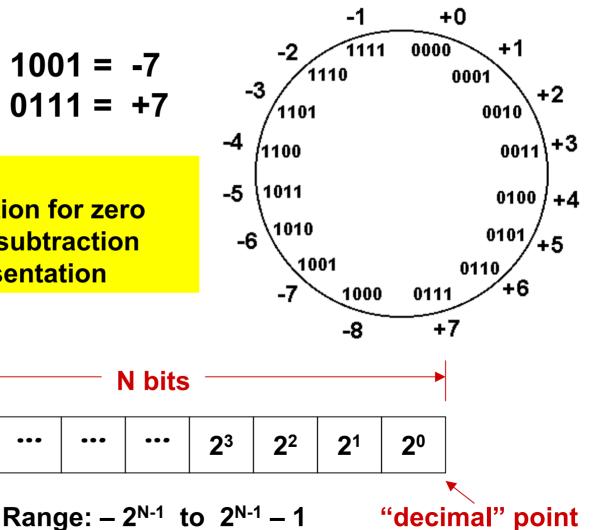

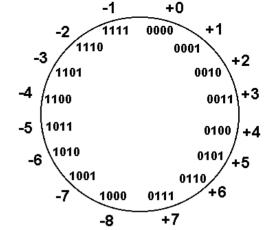

# Negative Numbers: Twos Complement Twos complement = bitwise complement + 1 -1 - +0

Asymmetric range

Only one representation for zero

Simple addition and subtraction

Most common representation

**-2**<sup>N-1</sup>

**2**N-2

6.111 Fall 2005

"sign bit"

### Twos Complement: Examples & Properties

#### • 4-bit examples:

| 4   | 0100 | -4 1100     | 4 0100   | -4  | 1100 |

|-----|------|-------------|----------|-----|------|

| + 3 | 0011 | + (-3) 1101 | - 3 1101 | + 3 | 0011 |

| 7   | 0111 | -7 11001    | 1 10001  | -1  | 1111 |

[Katz'93, chapter 5]

•8-bit twos complement example:

$11010110 = -2^7 + 2^6 + 2^4 + 2^2 + 2^1 = -128 + 64 + 16 + 4 + 2 = -42$

- With twos complement representation for signed integers, the same binary addition procedure works for adding both signed and unsigned numbers.

- •By moving the implicit location of "decimal" point, we can represent fractions too:

$1101.0110 = -2^3 + 2^2 + 2^0 + 2^{-2} + 2^{-3} = -8 + 4 + 1 + 0.25 + 0.125 = -2.25$

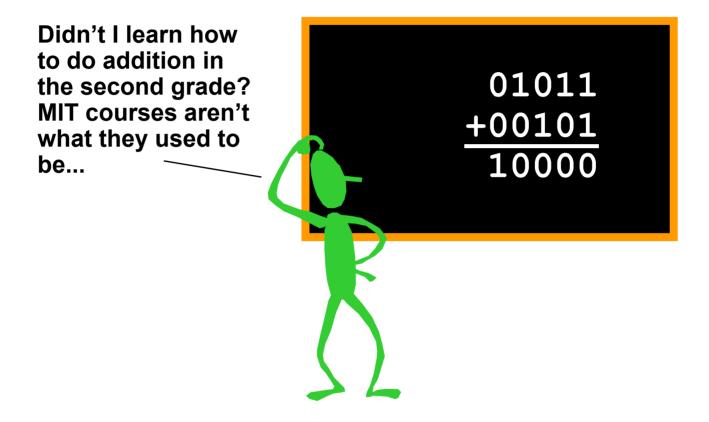

## 2. Binary Addition & Subtraction

#### **Addition:**

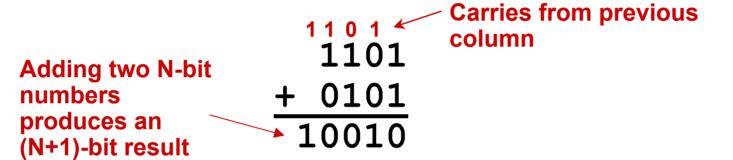

Here's an example of binary addition as one might do it by "hand":

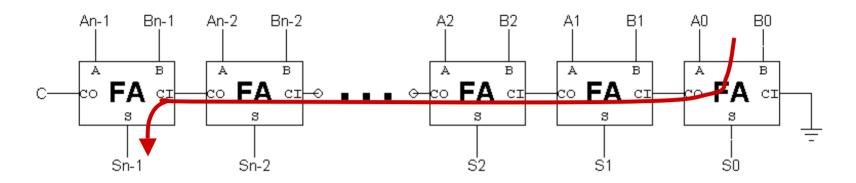

We've already built the circuit that implements one column:

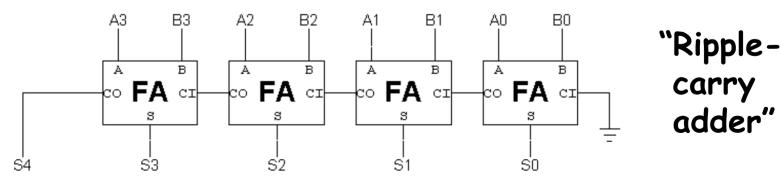

So we can quickly build a circuit two add two 4-bit numbers...

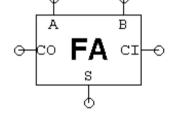

#### Subtraction: A-B = A + (-B)

Using 2's complement representation: -B = -B + 1

So let's build an arithmetic unit that does both addition and subtraction. Operation selected by *control input*:

~B

= bit-wise complement

В

#### **Condition Codes**

Besides the sum, one often wants four other bits of information from an arithmetic unit: To compare A and B, perform A–B and use condition codes: Z (zero): result is = 0 big NOR gate Signed comparison: N (negative): result is < 0  $S_{N-1}$ N⊕V Т.Т LE Z+(N⊕V) **C** (carry): indicates an add in the most EO Z significant position produced a carry, ~Z NE e.g., 1111 + 0001 from last FA ~ (N⊕V) GE ~(Z+(N⊕V)) GT V (overflow): indicates that the answer has too many bits to be represented **Unsigned comparison:** correctly by the result width, e.g., T.TTJ С 0111 + 0111C+ZLEU ~C GEU

$$V = A_{N-1}B_{N-1}\overline{S_{N-1}} + \overline{A_{N-1}}B_{N-1}S_{N-1}$$

$$V = COUT_{N-1} \oplus CIN_{N-1}$$

~(C+Z)

GTU

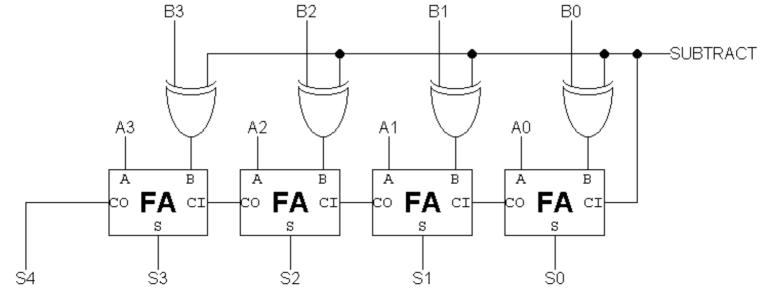

## 3. Speed: $t_{PD}$ of Ripple-carry Adder

Worse-case path: carry propagation from LSB to MSB, e.g., when adding 11...111 to 00...001.

$$f_{PD} = (N-1)^* (t_{PD,OR} + t_{PD,AND}) + t_{PD,XOR} \approx \Theta(N)$$

$$CI \text{ to } CO \qquad CI_{N-1} \text{ to } S_{N-1}$$

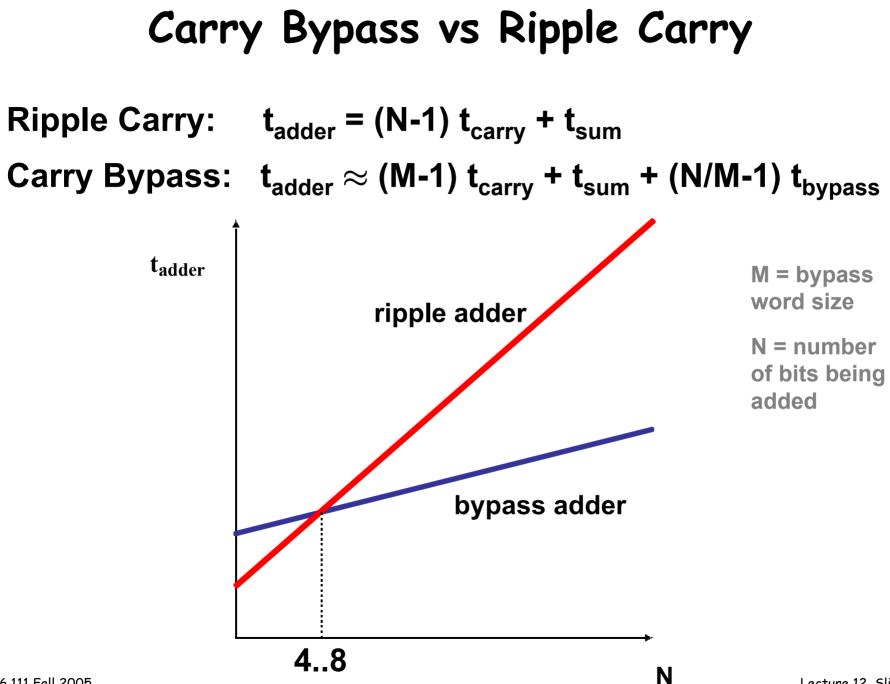

$$t_{adder} = (N-1)t_{carry} + t_{sum}$$

𝔅(N) is read

"order N":

means that the

latency of our

adder grows at

worst in

proportion to

the number of

bits in the

operands.

### Faster carry logic

Let's see if we can improve the speed by rewriting the equations for  $C_{OUT}$ :

$$C_{in} \xrightarrow{A} B = C_{OUT} = AB + AC_{IN} + BC_{IN}$$

= AB + (A + B)C<sub>IN</sub>

= AB + (A + B)C<sub>IN</sub>

where G = AB and P = A + B

generate propagate

S

Generate (G) = AB

Propagate (P) = A  $\oplus$  B

$$C_o(G, P) = G + PC_i$$

S(G, P) = P  $\oplus$  C<sub>i</sub>

S(G, P) = P  $\oplus$  C<sub>i</sub>

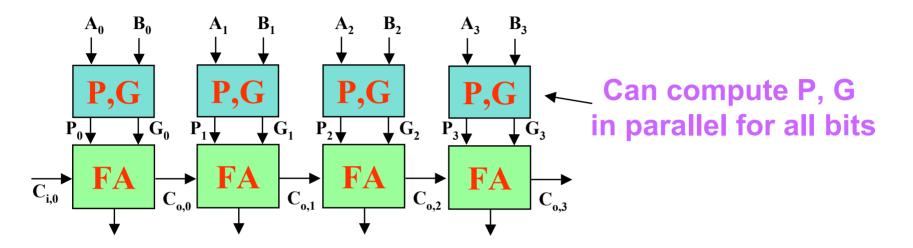

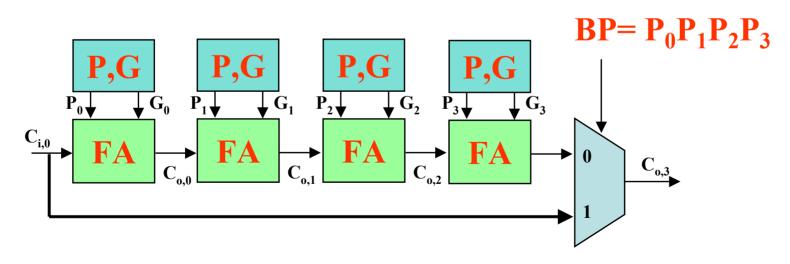

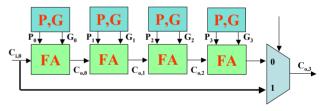

# 4. Carry Bypass Adder

**Key Idea:** if  $(P_0 P_1 P_2 P_3)$  then  $C_{0,3} = C_{i,0}$

6.111 Fall 2005

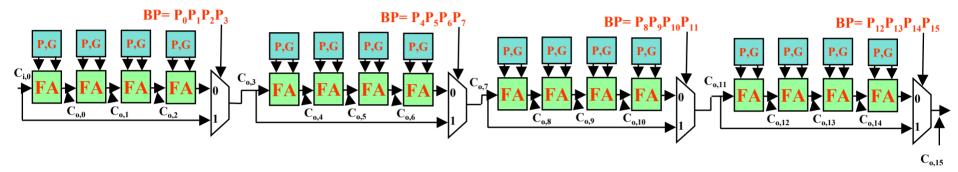

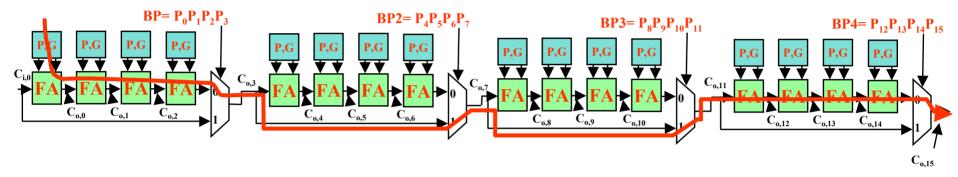

## 16-bit Carry Bypass Adder

# What is the worst case propagation delay for the 16-bit adder?

#### Assume the following for delay each gate:

P, G from A, B: 1 delay unit P, G, C<sub>i</sub> to C<sub>o</sub> or Sum for a FA: 1 delay unit 2:1 mux delay: 1 delay unit

## **Critical Path Analysis**

For the second stage, is the critical path:

BP2 = 0 or BP2 = 1?

#### Message: Timing Analysis is Very Tricky – Must Carefully Consider Data Dependencies For <u>False Paths</u>

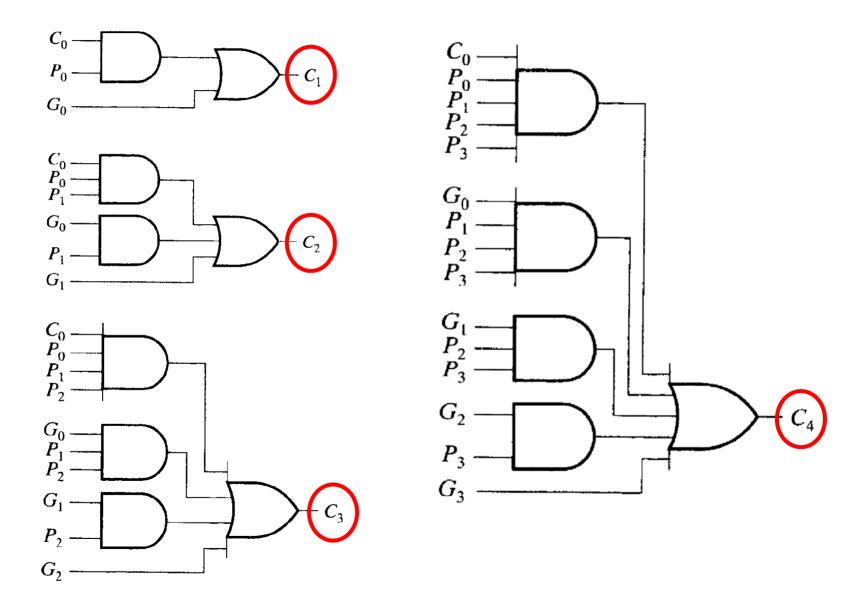

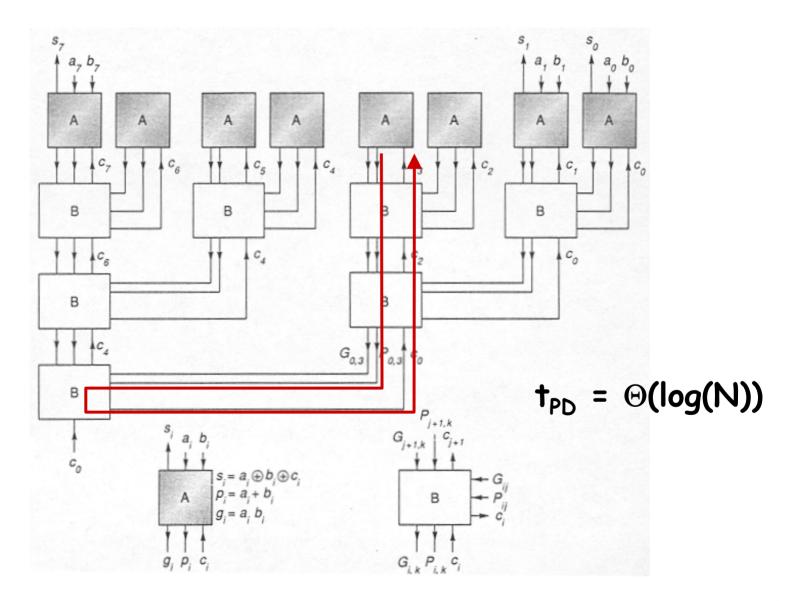

#### 5. Carry Lookahead Adder (CLA)

• Recall that  $C_{OUT} = G + P C_{IN}$

$C_{OUT} = G + P C_{IN}$  where G = AB and  $P = A \oplus B$

• For adding two N-bit numbers:

$$C_{N} = G_{N-1} + P_{N-1}C_{N-1}$$

=  $G_{N-1} + P_{N-1}G_{N-2} + P_{N-1}P_{N-2}C_{N-2}$

=  $G_{N-1} + P_{N-1}G_{N-2} + P_{N-1}P_{N-2}G_{N-3} + ... + P_{N-1}...P_{0}C_{IN}$

$C_{N}$  in only 3 gate delays (!) :

1 for P/G generation, 1 for ANDs, 1 for final OR

Idea: pre-compute all carry bits combinatorially

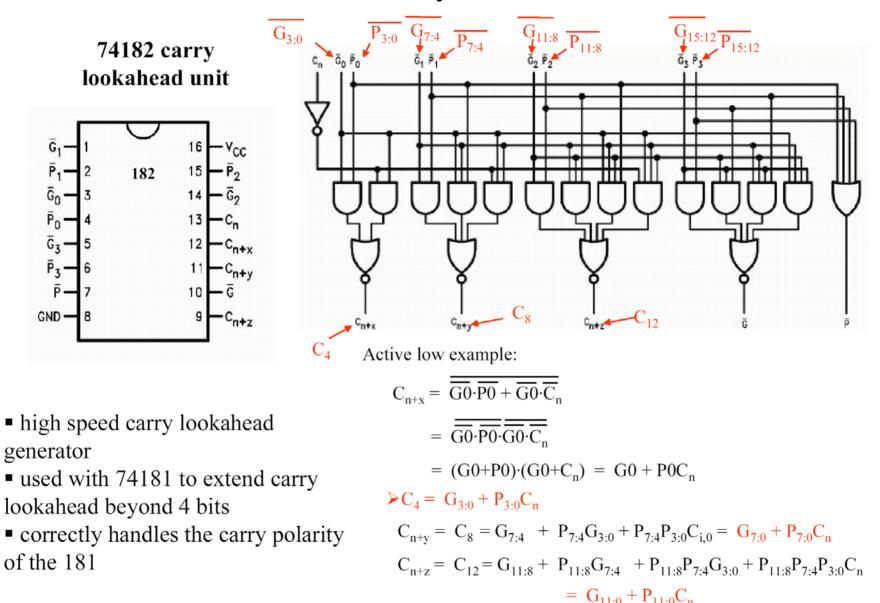

#### **Carry Lookahead Circuits**

The 74182 Carry Lookahead Unit

Lecture 12, Slide 17

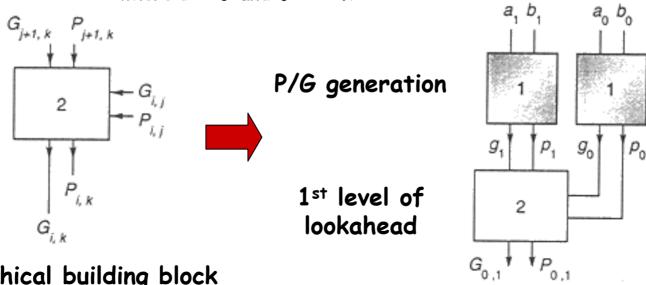

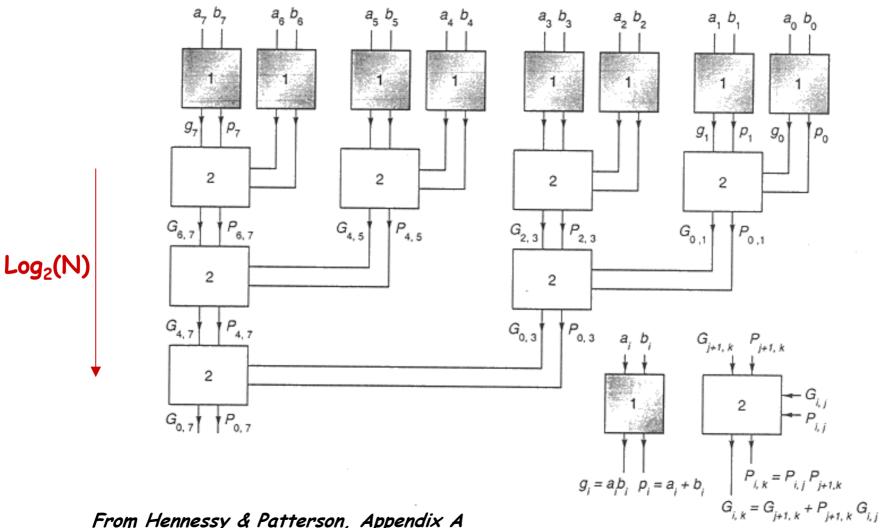

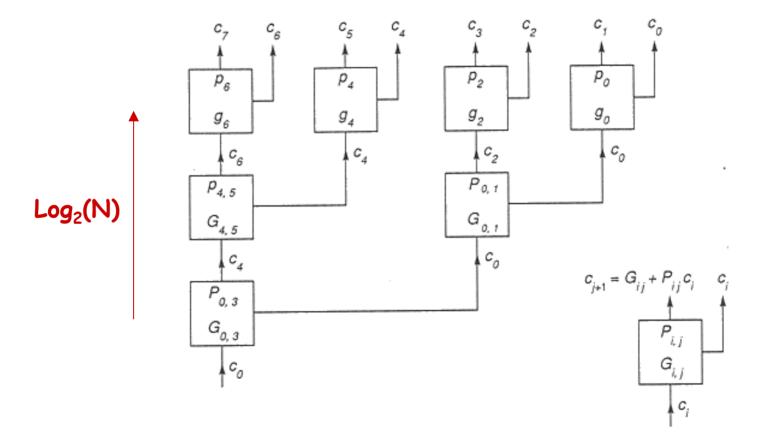

### **Block Generate and Propagate**

G and P can be computed for groups of bits (instead of just for individual bits). This allows us to choose the maximum fan-in we want for our logic gates and then build a hierarchical carry chain using these equations:

$$C_{J+1} = G_{IJ} + P_{IJ}C_{I}$$

$$G_{IK} = G_{J+1,K} + P_{J+1,K}G_{IJ}$$

$$P_{IK} = P_{IJ}P_{J+1,K}$$

generate a carry from bits I thru K if it is generated in the high-order (J+1,K) part of the block or if it is generated in the low-order (I,J) part of the block and then propagated thru the high part"

where I < J and J+1 < K

Hierarchical building block

8-bit CLA (P/G generation)

From Hennessy & Patterson, Appendix A

### 8-bit CLA (carry generation)

#### 8-bit CLA (complete)

### Summary

- Negative numbers:

- Twos Complement -B =  $\overline{B}$  + 1

- Addition & Subtraction use same adder

- Ripple Carry Adder:

- $t_{adder} = (N-1) t_{carry} + t_{sum}$

- Carry Bypass Adder:  $- t_{adder} \approx (M-1) t_{carry} + t_{sum} + (N/M-1) t_{bypass}$

- Carry Lookahead Adder:  $- t_{adder} \approx 2 \log_2(N) t_{pg}$