#### Memories: a practical primer

- The good news: huge selection of technologies

- Small & faster vs. large & slower

- Every year capacities go up and prices go down

- New kid on the block: high density, fast flash memories

- Non-volatile, read/write, no moving parts! (robust, efficient)

- The bad news: perennial system bottleneck

- Latencies (access time) haven't kept pace with cycle times

- Separate technology from logic, so must communicate between silicon, so physical limitations (# of pins, R's and C's and L's) limit bandwidths

- New hopes: capacitive interconnect, 3D IC's

- Likely the limiting factor in cost & performance of many digital systems: designers spend a lot of time figuring out how to keep memories running at peak bandwidth

- "It's the memory, stupid"

#### Memories in Verilog

- reg bit; // a single register

- reg [31:0] word; // a 32-bit register

- reg [31:0] array[15:0] // 16 32-bit regs

- wire [31:0] read\_data,write\_data; wire [3:0] index;

// combinational (asynch) read

assign read\_data = array[index];

// clocked (synchronous) write

always @ (posedge clock)

array[index] <= write\_data;</pre>

#### Multi-port Memories (aka regfiles)

reg [31:0] regfile[31:0]; // 32 32-bit words

```

// Beta register file: 2 read ports, 1 write

wire [4:0] ra1,ra2,wa;

wire [31:0] rd1,rd2,wd;

```

```

assign ra1 = inst[20:16];

assign ra2 = ra2sel ? inst[25:21] : inst[15:11];

assign wa = wasel ? 5'd30 : inst[25:21];

```

// read ports

assign rd1 = (ra1 == 31) ? 0 : regfile[ra1];

assign rd2 = (ra2 == 31) ? 0 : regfile[ra2];

// write port

always @ (posedge clk)

if (werf) regfile[wa] <= wd;</pre>

```

assign z = ~ | rd1; // used in BEQ/BNE instructions

6.111 Fall 2005

```

## FPGA memory implementation

- Regular registers in logic blocks

- Piggy use of resources, but convenient & fast if small

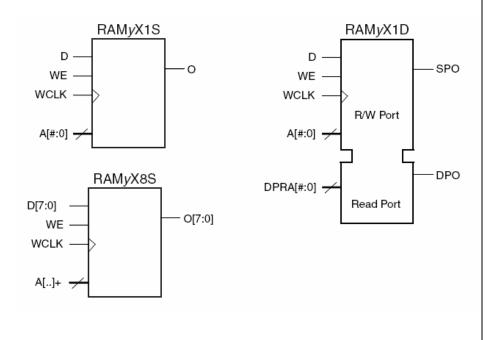

- [Xilinx Vertex II] use the LUTs:

- Single port: 16x(1,2,4,8), 32x(1,2,4,8), 64x(1,2), 128x1

- Dual port (1 R/W, 1R): 16x1, 32x1, 64x1

- Can fake extra read ports by cloning memory: all clones are written with the same addr/data, but each clone can have a different read address

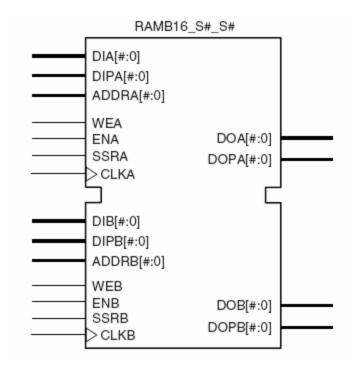

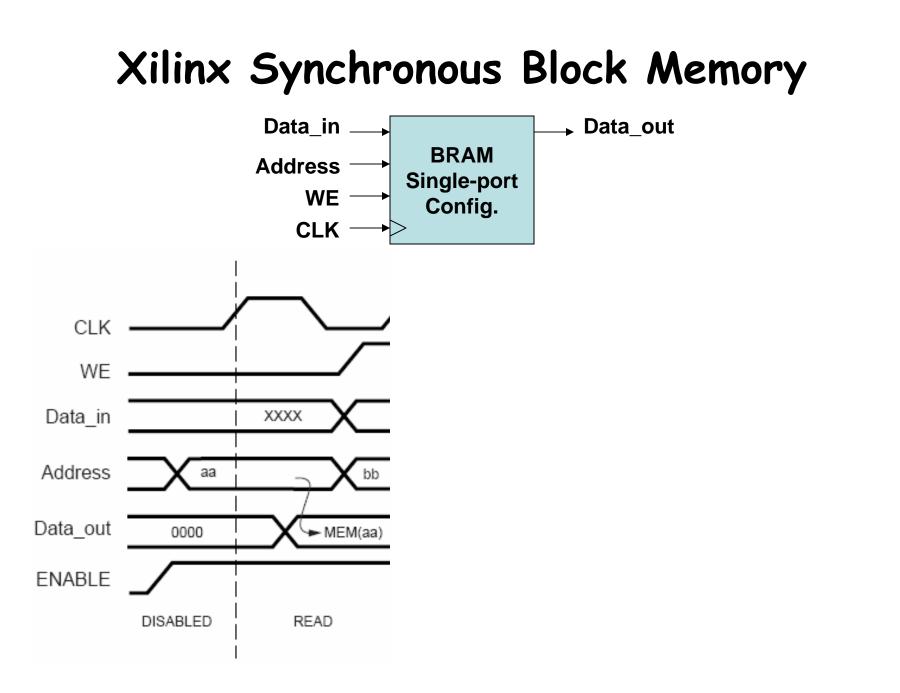

- [Xilinx Vertex II] use block ram:

- 18K bits: 16K×1, 8K×2, 4K×4 with parity: 2K×(8+1), 1K×(16+2), 512×(32+4)

- Single or dual port

- Pipelined (clocked) operations

- Labkit XCV2V6000: 144 BRAMs, 2952K bits total

#### Virtex memory configurations

# Using LUT resources in configurable logic blocks:

Using BRAMs:

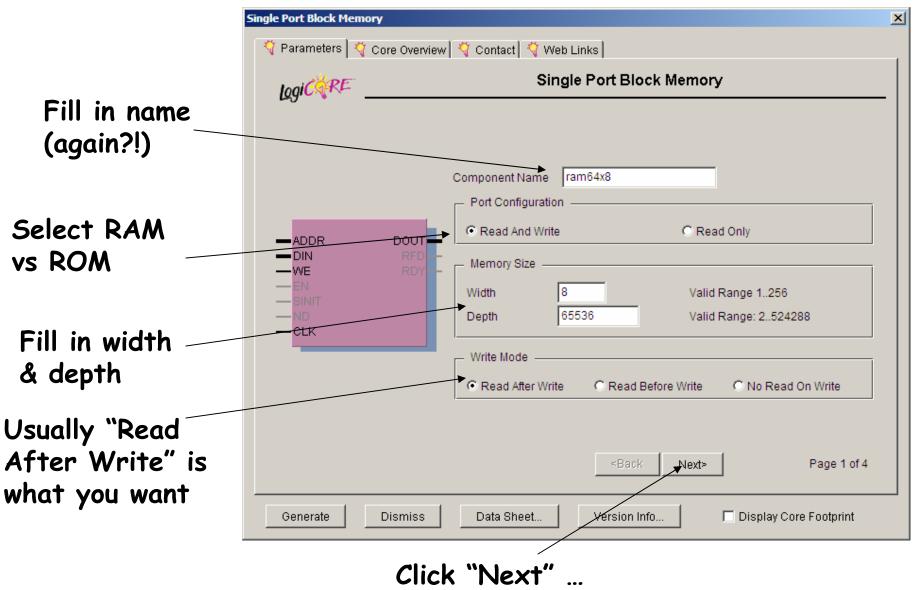

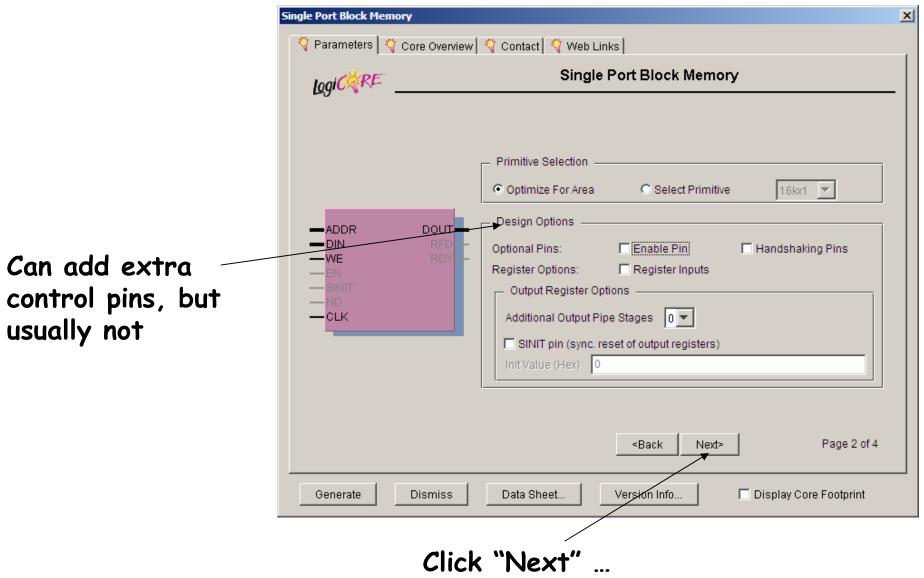

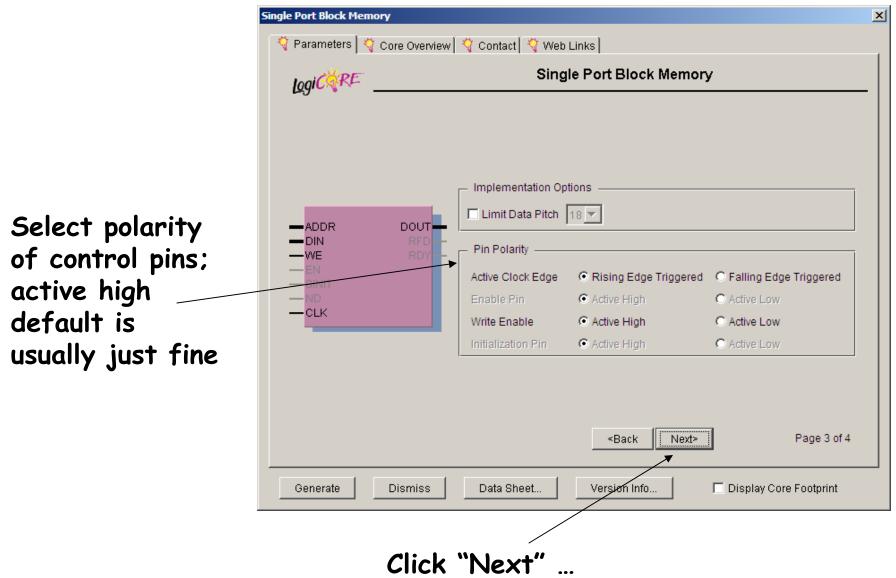

## Using BRAMs (eg, a 64Kx8 ram)

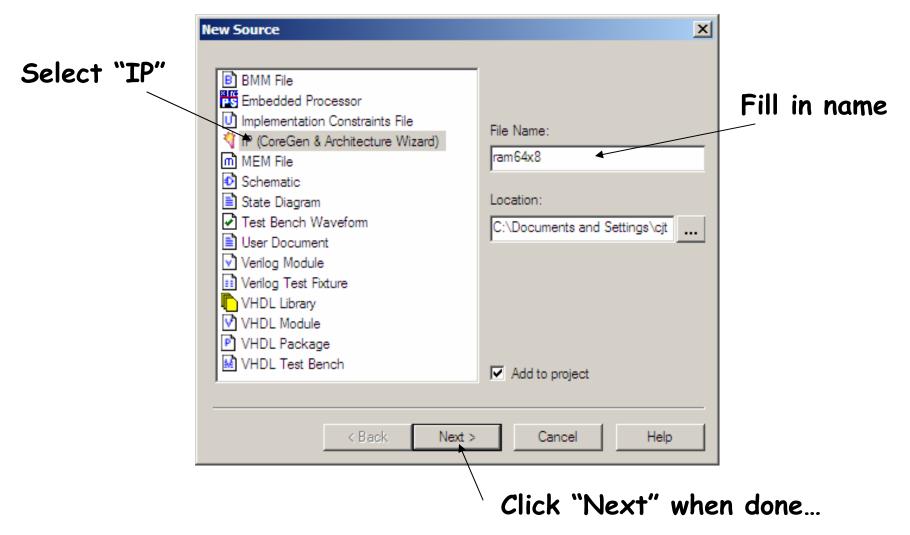

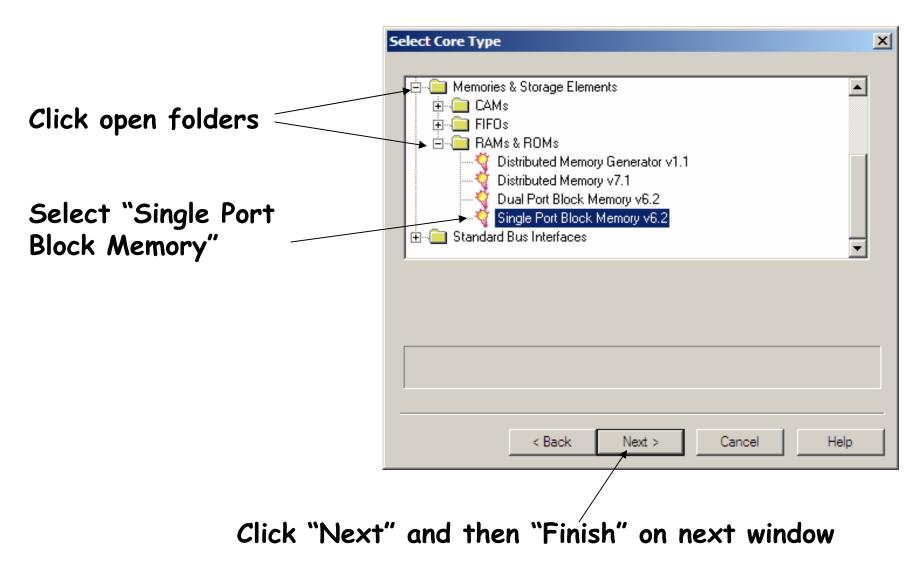

• From menus: Project  $\rightarrow$  New Source...

| Simulation Model Options<br>Warnings Disable Warning Messages<br>Initial Contents<br>Global Init Value:<br>Use of the second seco |                                                                         | LogiCZRE                               | [ Core Overview   🏹 Contact   🏹 Web Links  <br>Single Port Block Memory                                                                                                                                                                                                                                                                                             |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Click to name a<br>.coe file that<br>specifies initial<br>contents (eg, | ADDR<br>DIN<br>WE<br>EN<br>SINIT<br>ND | Warnings       Disable Warning Messages         Initial Contents       Global Init Value:         0       Image: Contents         Load Init File       Show Coefficients         Load File       Show Coefficients         Information Panel       Address Width         Address Width       16         Blocks Used       32         Read Pipeline Latency:       1 |  |

6.111 Fall 2005

#### .coe file format

memory\_initialization\_radix=2;

memory\_initialization\_vector=

0000000,

- 00111110,

- 01100011,

- 0000011,

- 0000011,

- 00011110,

- 00000011,

- 0000011,

- 01100011,

- 00111110,

0000000,

0000000,

Memory contents with location 0 first, then location 1, etc. You can specify input radix, in this example we're using binary. MSB is on the left, LSB on the right. Unspecified locations (if memory has more locations than given in .coe file) are set to 0.

## Using result in your Verilog

Look at generated Verilog for module def'n:

```

module ram64x8 (addr,clk,din,dout,we);

input [15 : 0] addr;

input clk;

input [7 : 0] din;

output [7 : 0] dout;

input we;

...

endmodule

```

• Use to instantiate instances in your code:

```

ram64x8 foo(addr,clk,din,dout,we);

```

## Toward FSM Modularity

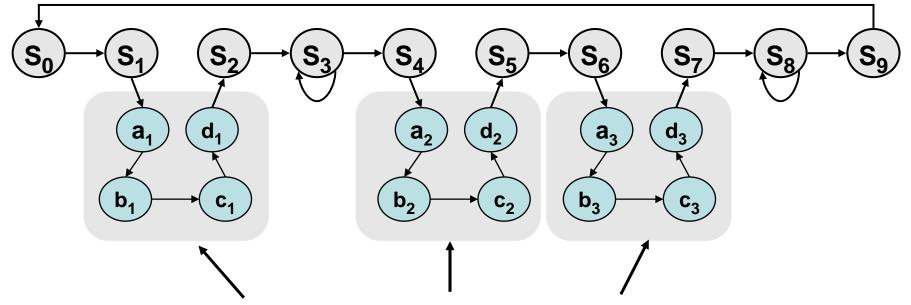

• Consider the following abstract FSM:

- Suppose that each set of states a<sub>x</sub>...d<sub>x</sub> is a "sub-FSM" that produces exactly the same outputs.

- Can we simplify the FSM by removing equivalent states? No! The outputs may be the same, but the next-state transitions are not.

- This situation closely resembles a procedure call or function call in software...how can we apply this concept to FSMs?

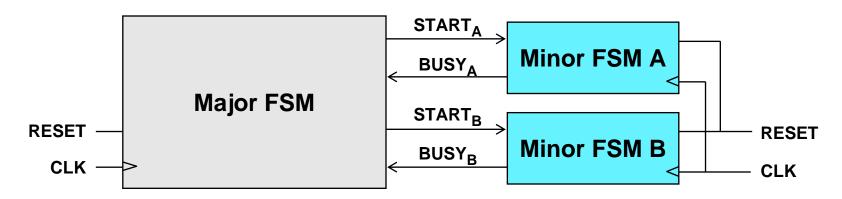

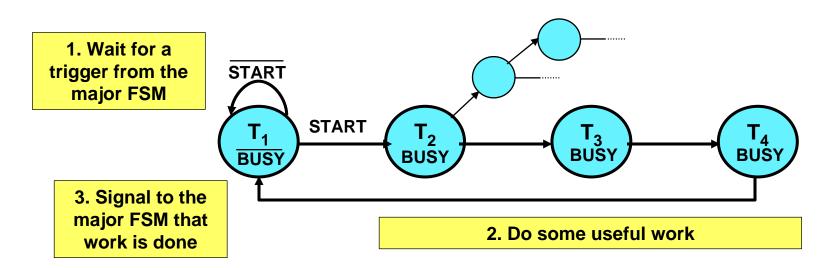

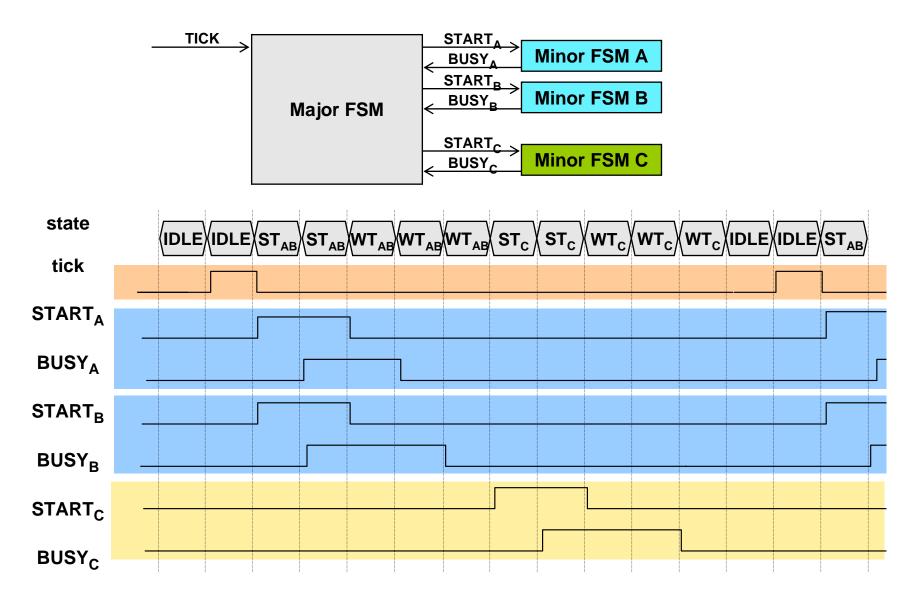

## The Major/Minor FSM Abstraction

- Subtasks are encapsulated in minor FSMs with common reset and clock

- Simple communication abstraction:

- START: tells the minor FSM to begin operation (the call)

- BUSY: tells the major FSM whether the minor is done (the return)

- The major/minor abstraction is great for...

- Modular designs (*always* a good thing)

- Tasks that occur often but in different contexts

- Tasks that require a variable/unknown period of time

- Event-driven systems

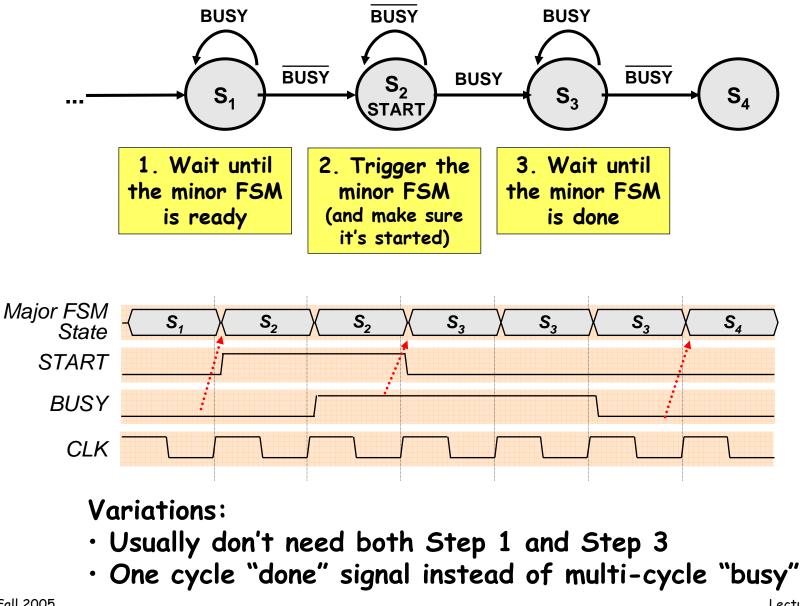

## Inside the Major FSM

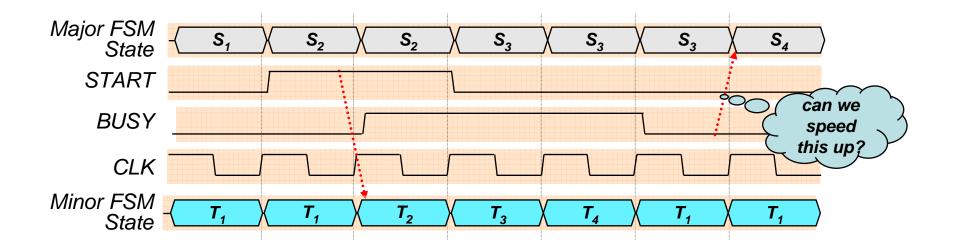

#### Inside the Minor FSM

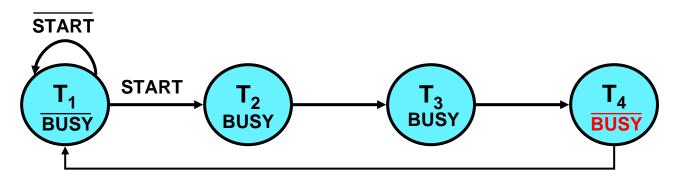

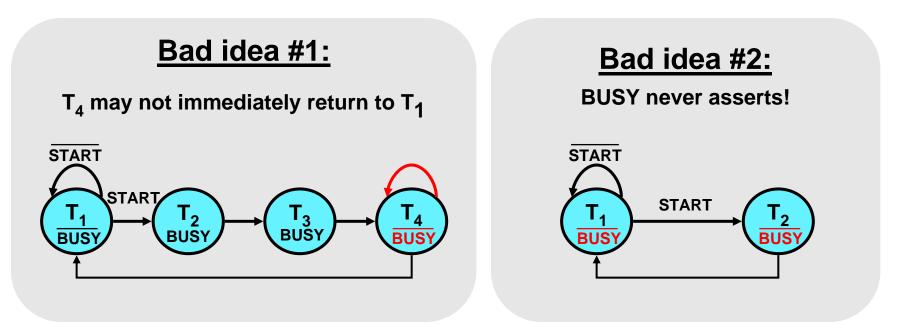

## Optimizing the Minor FSM

Good idea: de-assert BUSY one cycle early

#### A Four-FSM Example TICK START, **Operating Scenario: Minor FSM A** Major FSM is triggered • BUSY, by TICK START<sub>P</sub> Minors A and B are started simultaneously **Minor FSM B** BUSY<sub>B</sub> **Major FSM** Minor C is started once both A and B complete START TICKs arriving before the completion of C are **Minor FSM C** BUSY ignored Assume that BUSY<sub>A</sub> and BUSY<sub>A</sub>+BUSY<sub>B</sub> BUSY<sub>B</sub> both rise before either TICK BUSY<sub>A</sub>+BUSY<sub>B</sub> minor FSM completes. Otherwise, we loop forever! BUSY<sub>A</sub>BUSY<sub>B</sub> STAB TICK WT<sub>AB</sub> IDLE **START**<sub>A</sub> START<sub>B</sub> BUSYABUSYB BUSY<sub>C</sub> ST<sub>C</sub> WT<sub>c</sub> BUSY<sub>C</sub> START **BUSY**<sub>C</sub> BUSY<sub>C</sub> Lecture 9, Slide 20 6.111 Fall 2005

## Four-FSM Sample Waveform

6.111 Fall 2005

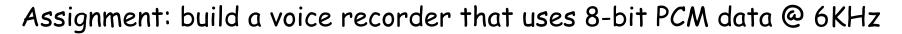

#### Lab 3 overview

About 11 seconds of speech @ 6KHz

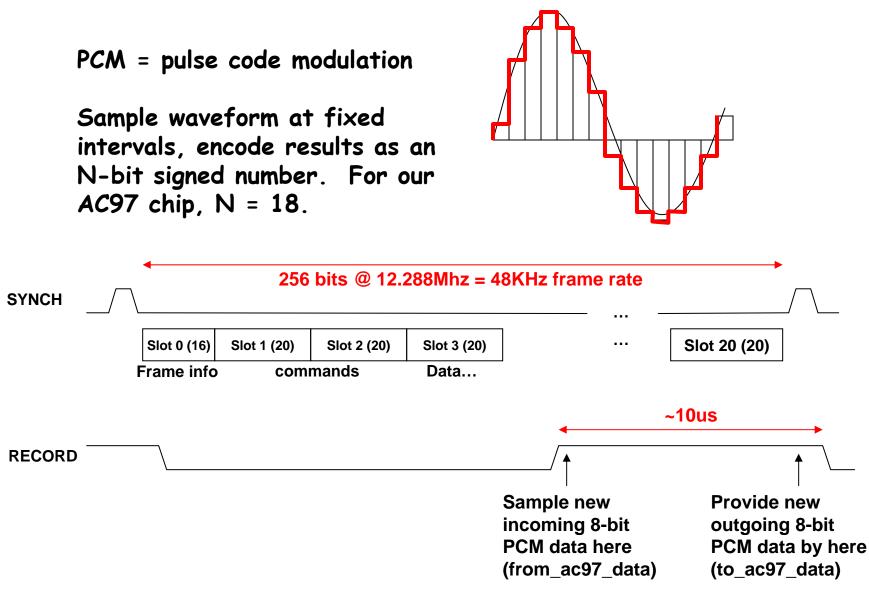

## AC97: PCM data