# 6.111 Lecture 6

Today: 1.Blocking vs. non-blocking assignments 2.Single clock synchronous circuits

**3.**Finite State Machines

#### I. <u>Blocking vs. Nonblocking Assignments</u>

Conceptual need for two kinds of assignment (in always blocks):

### Assignment Styles for Sequential Logic

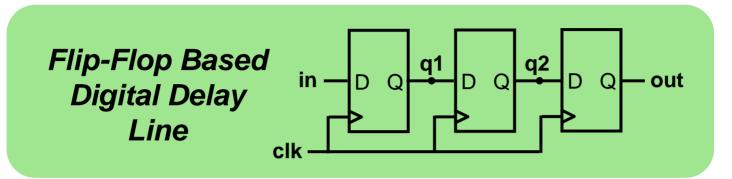

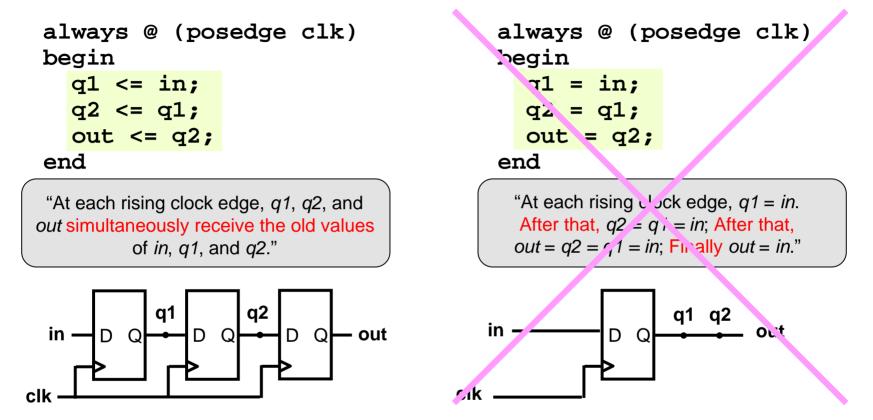

Will nonblocking and blocking assignments both produce the desired result?

```

module nonblocking(in, clk, out);

input in, clk;

output out;

reg q1, q2, out;

always @ (posedge clk)

begin

q1 <= in;

q2 <= q1;

out <= q2;

end

endmodule</pre>

```

```

module blocking(in, clk, out);

input in, clk;

output out;

reg q1, q2, out;

always @ (posedge clk)

begin

q1 = in;

q2 = q1;

out = q2;

end

endmodule

```

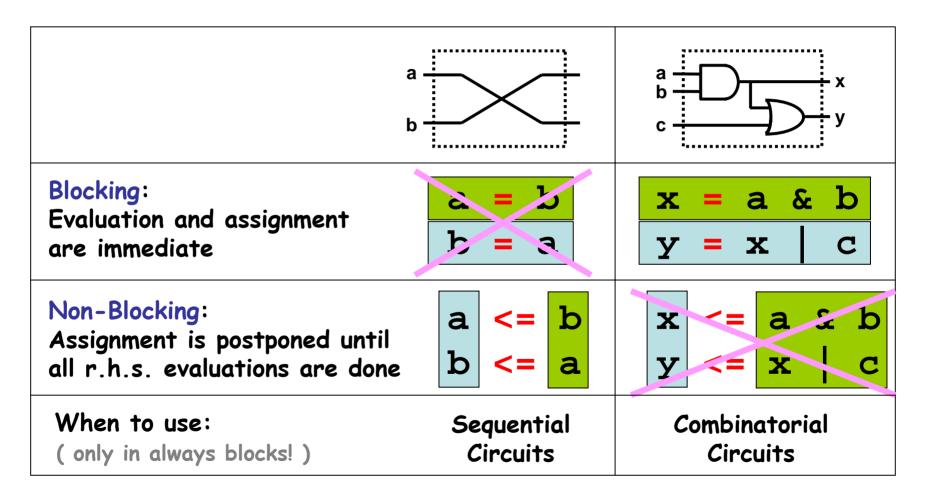

### Use Nonblocking for Sequential Logic

- Blocking assignments do not reflect the intrinsic behavior of multi-stage sequential logic

- Guideline: use <u>nonblocking</u> assignments for <u>sequential</u> always blocks

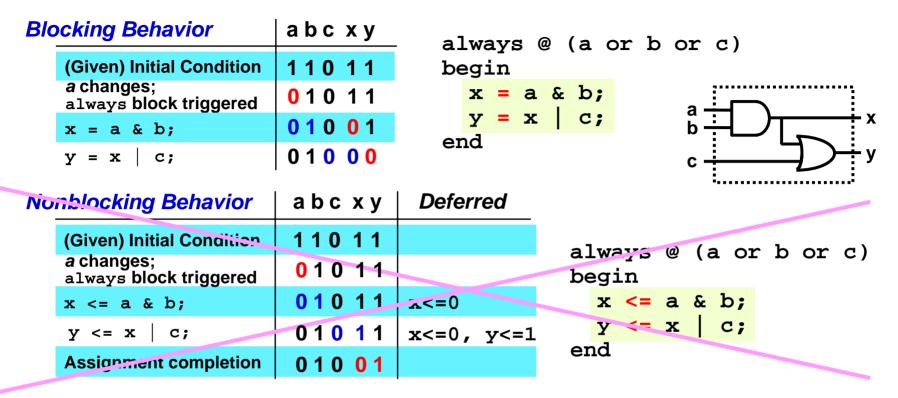

### Use Blocking for Combinational Logic

- Nonblocking assignments do not reflect the intrinsic behavior of multi-stage combinational logic

- While nonblocking assignments can be hacked to simulate correctly (expand the sensitivity list), it's not elegant

- Guideline: use <u>blocking</u> assignments for <u>combinational</u> always blocks

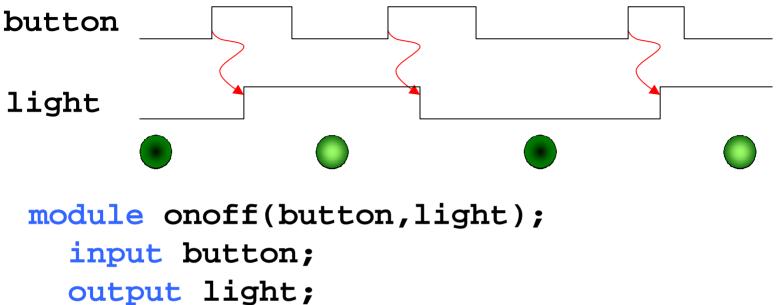

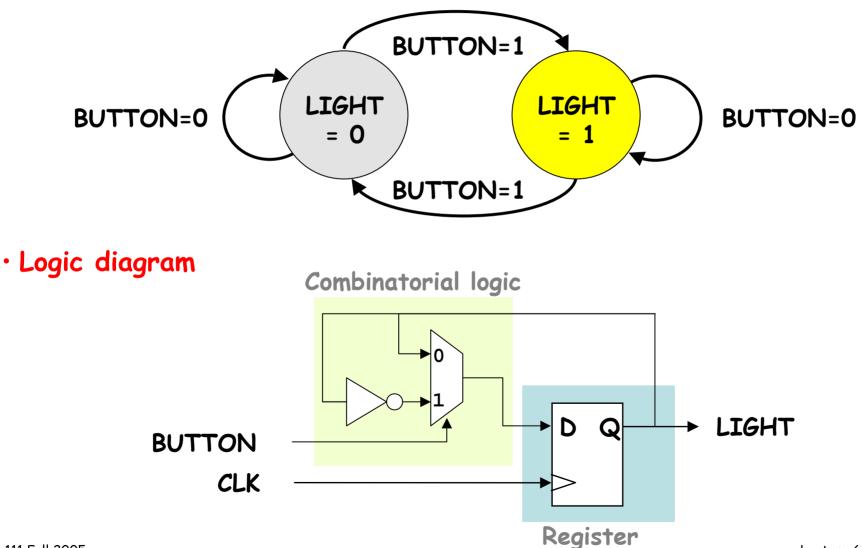

#### Implementation for on/off button

```

reg light;

always @ (posedge button)

begin

light <= ~light;

end

BUTTON → Q

```

endmodule

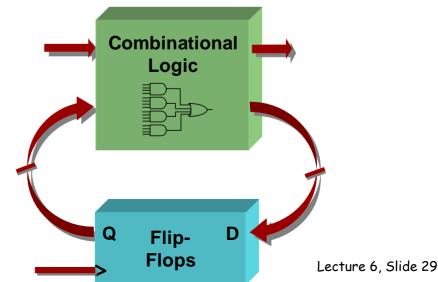

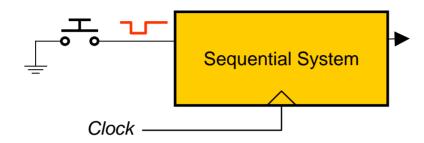

#### II. Single-clock Synchronous Circuits

We'll use Flip Flops and *Registers* – groups of FFs sharing a clock input – in a highly constrained way to build digital systems.

#### Single-clock Synchronous Discipline:

- No combinational cycles

- Single clock signal shared among all clocked devices

- Only care about value of combinational circuits just before rising edge of clock

- Period greater than every combinational delay

- Change saved state after noise-inducing logic transitions have stopped!

#### Clocked circuit for on/off button

0

D

LOAD-ENABLED REGISTER

Q

```

module onoff(clk,button,light);

input clk,button;

output light;

reg light;

always @ (posedge clk)

begin

if (button) light <= ~light;</pre>

```

D

LE

CLK

end

endmodule

SINGLE GLOBAL CLOCK

BUTTON

CLK

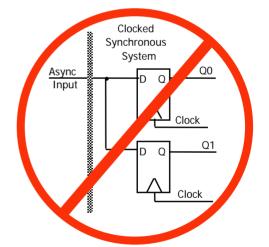

#### Asynchronous Inputs in Sequential Systems

What about external signals?

Can't guarantee setup and hold times will be met!

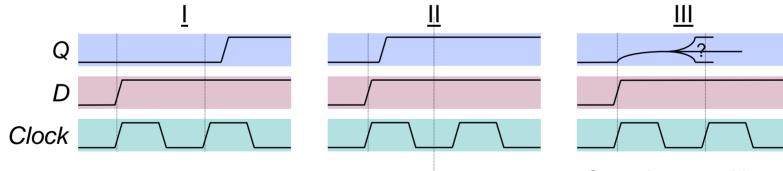

When an asynchronous signal causes a setup/hold violation...

Transition is missed on first clock cycle, but caught on next clock cycle.

Transition is caught on first clock cycle.

Output is metastable for an indeterminate amount of time.

#### Q: Which cases are problematic?

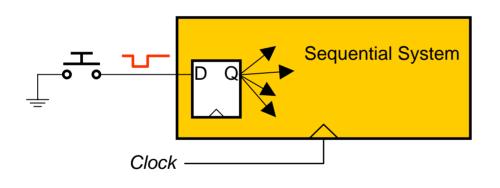

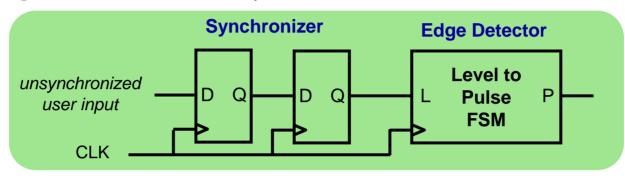

#### Asynchronous Inputs in Sequential Systems

All of them can be, if more than one happens simultaneously within the same circuit.

Idea: ensure that external signals directly feed exactly one flip-flop

This prevents the possibility of I and II occurring in different places in the circuit, but what about metastability?

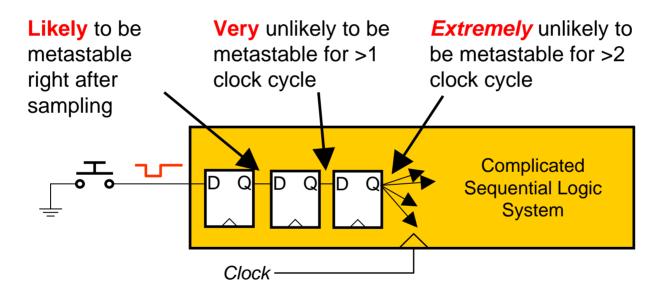

## Handling Metastability

- Preventing metastability turns out to be an impossible problem

- High gain of digital devices makes it likely that metastable conditions will resolve themselves quickly

- Solution to metastability: allow time for signals to stabilize

How many registers are necessary?

- Depends on many design parameters(clock speed, device speeds, ...)

- In 6.111, a pair of synchronization registers is sufficient

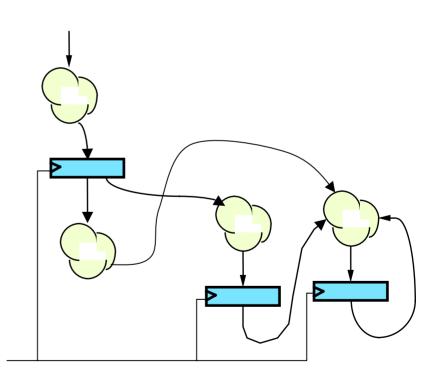

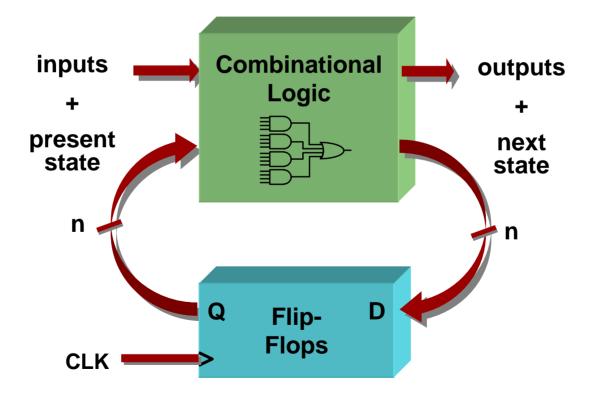

#### III. <u>Finite State Machines</u>

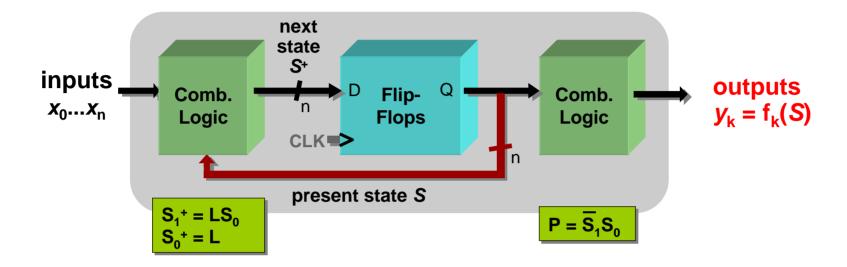

- Finite State Machines (FSMs) are a useful abstraction for sequential circuits with centralized "states" of operation

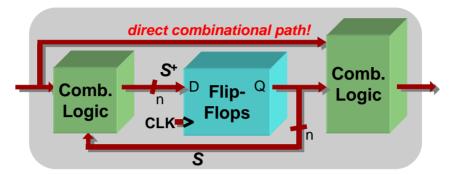

- At each clock edge, combinational logic computes outputs and next state as a function of inputs and present state

### Example 1: Light Switch

State transition diagram

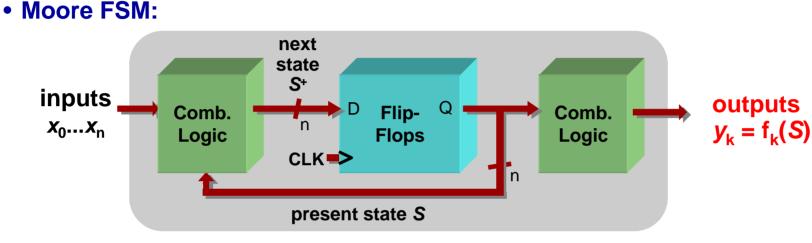

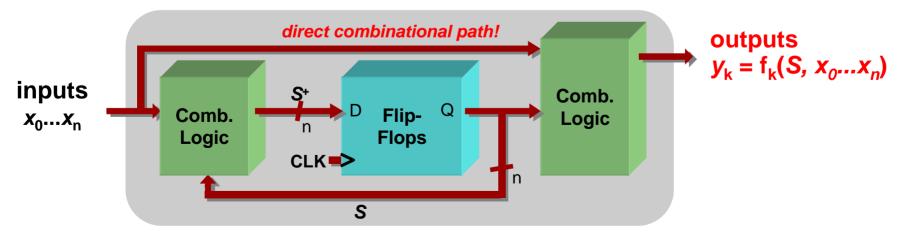

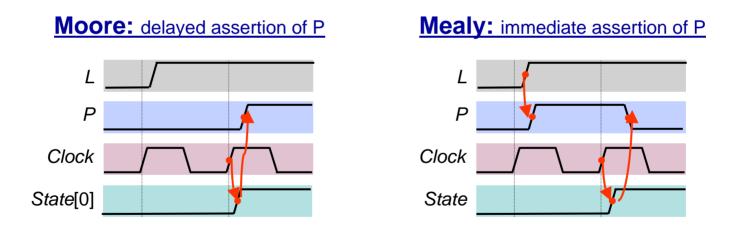

# Two Types of FSMs

Moore and Mealy FSMs : different output generation

• Mealy FSM:

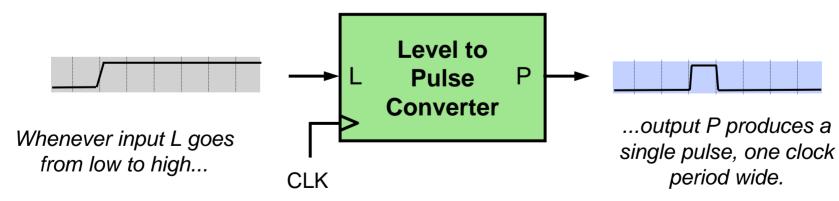

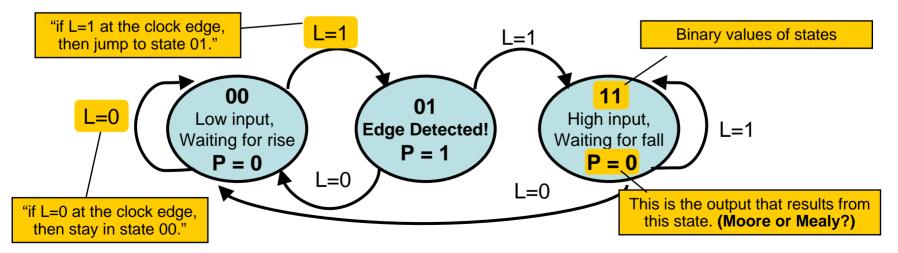

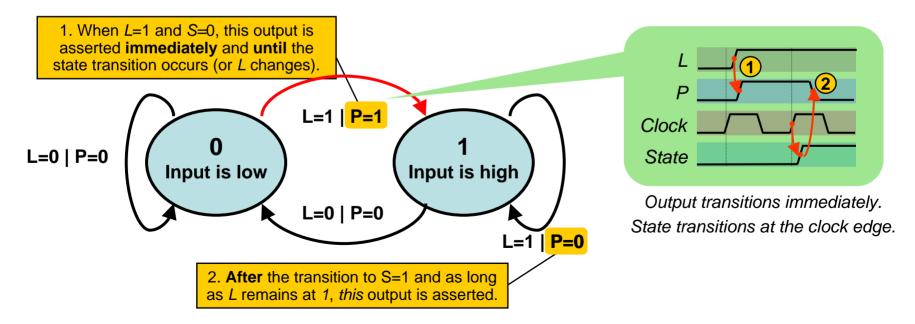

# Design Example: Level-to-Pulse

- A level-to-pulse converter produces a single-cycle pulse each time its input goes high.

- It's a synchronous rising-edge detector.

- Sample uses:

- Buttons and switches pressed by humans for arbitrary periods of time

- Single-cycle enable signals for counters

#### Step 1: State Transition Diagram

Block diagram of desired system:

• State transition diagram is a useful FSM representation and design aid:

٠

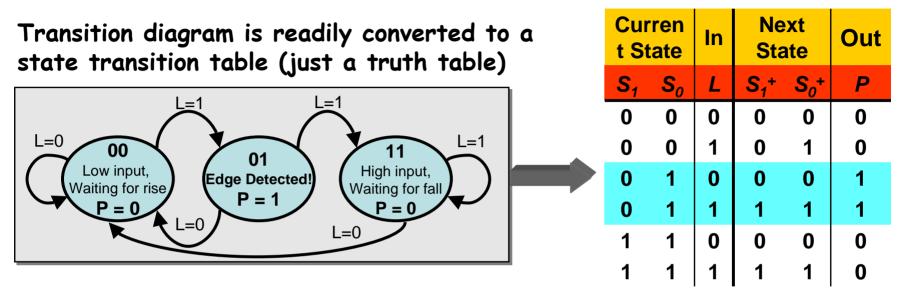

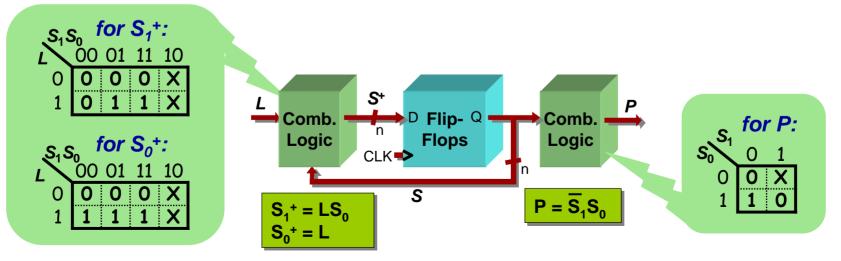

# Step 2: Logic Derivation

• Combinational logic may be derived using Karnaugh maps

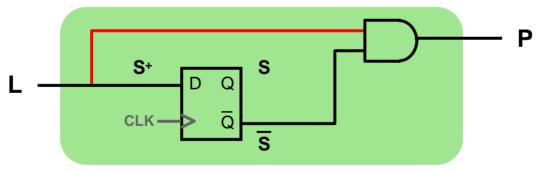

#### Moore Level-to-Pulse Converter

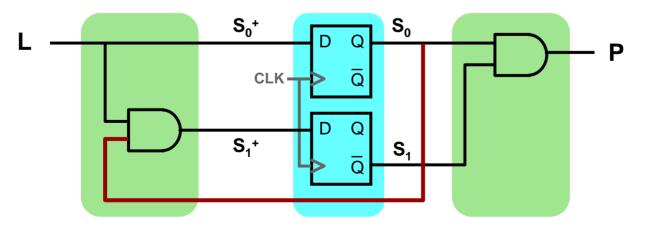

Moore FSM circuit implementation of level-to-pulse converter:

### Design of a Mealy Level-to-Pulse

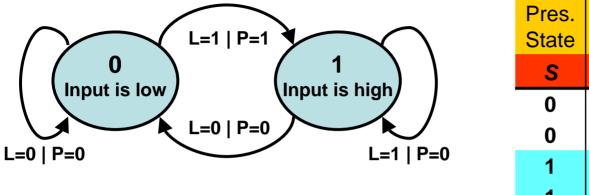

Since outputs are determined by state and inputs, Mealy FSMs may need fewer states than Moore FSM implementations

#### Mealy Level-to-Pulse Converter

| Pres.<br>State | In | Next<br>State | Out |

|----------------|----|---------------|-----|

| S              | L  | S+            | Р   |

| 0              | 0  | 0             | 0   |

| 0              | 1  | 1             | 1   |

| 1              | 0  | 0             | 0   |

| 1              | 1  | 1             | 0   |

Mealy FSM circuit implementation of level-to-pulse converter:

- FSM's state simply remembers the previous value of L

- Circuit benefits from the Mealy FSM's implicit singlecycle assertion of outputs during state transitions

#### Moore/Mealy Trade-Offs

- How are they different?

- Moore: outputs = f( state ) only

- Mealy outputs = f( state and input )

- Mealy outputs generally occur <u>one cycle earlier</u> than a Moore:

- Compared to a Moore FSM, a Mealy FSM might...

- Be more difficult to conceptualize and design

- Have fewer states

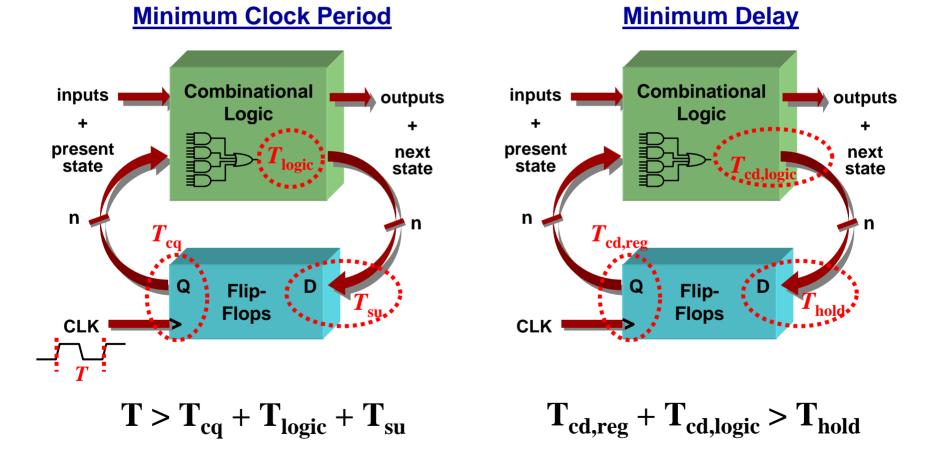

### **FSM** Timing Requirements

Timing requirements for FSM are identical to any generic sequential system with feedback

#### Summary

- Assignments in always blocks:

- blocking ("=") for combinational logic

- non-blocking ("<=") for sequential logic</pre>

- Single-clock Synchronous discipline:

- Reliable digital circuits / systems

- Global clock to edge-triggered registers

- Finite state machines:

- Programmable systems

- Moore & Mealy