### Something We Can't Build (Yet)

What if you were given the following design specification:

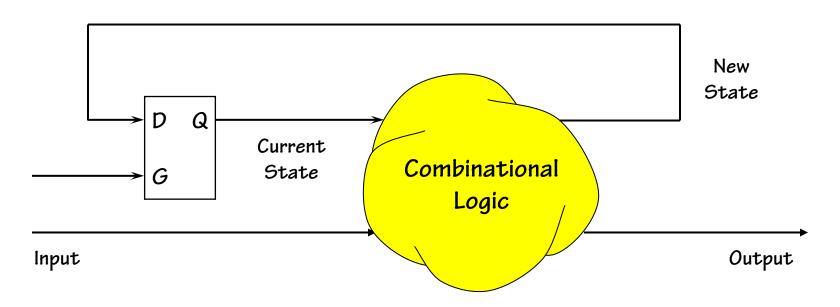

#### Digital State One model of what we'd like to build

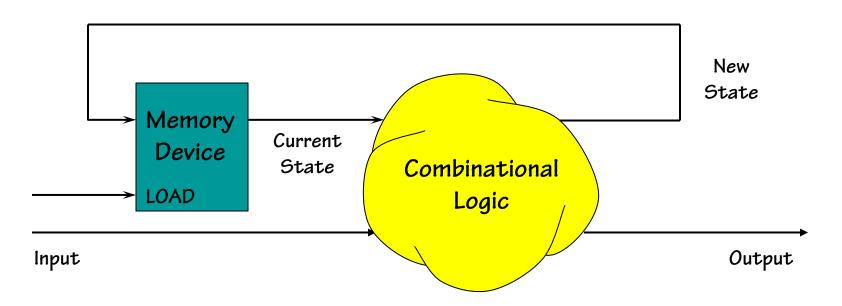

Plan: Build a Sequential Circuit with stored digital STATE -

- Memory stores CURRENT state, produced at output

- Combinational Logic computes

- NEXT state (from input, current state)

- OUTPUT bit (from input, current state)

- State changes on LOAD control input

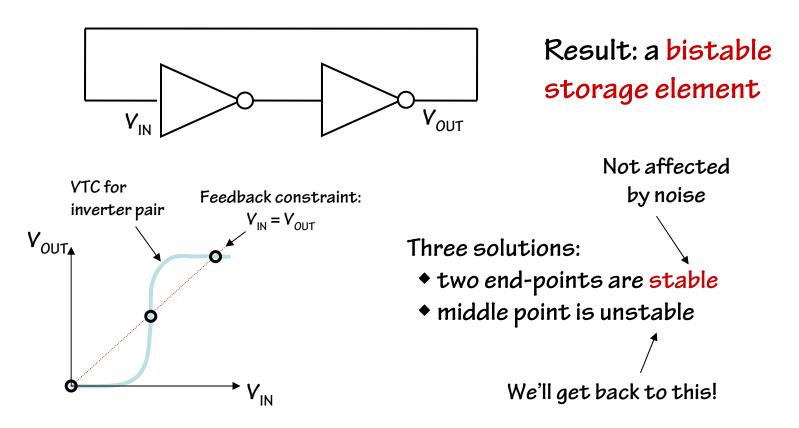

# Storage: Using Feedback

IDEA: use **positive feedback** to maintain storage indefinitely. Our logic gates are built to restore marginal signal levels, so noise shouldn't be a problem!

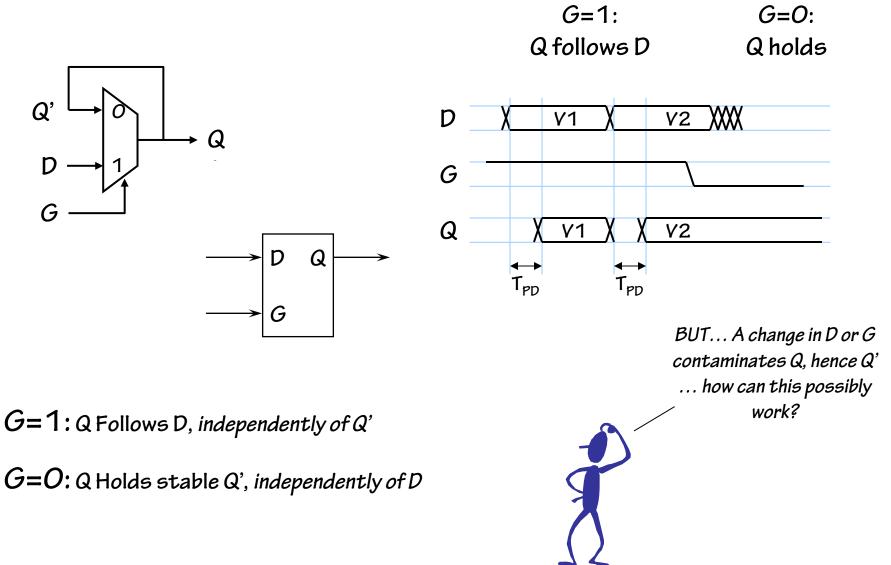

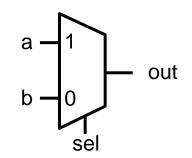

#### Settable Storage Element

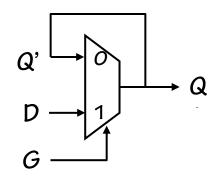

It's easy to build a settable storage element (called a latch) using a *lenient* MUX: Here's a feedback path, "state" signal so it's no longer a appears as both combinational circuit. input and output G D **Q**<sub>IN</sub> **Q**<sub>OUT</sub> 0 Q 1 Qstable 1 1 D 0 1 0 --1 1 --Q follows D G

#### New Device: D Latch

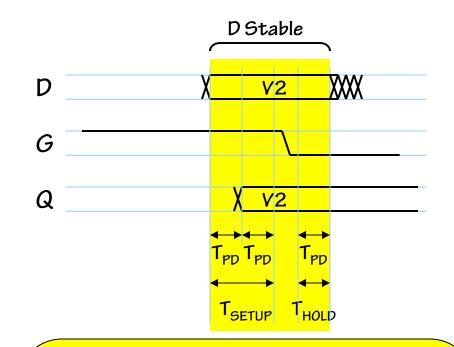

# D-Latch timing

#### To <u>reliably latch</u> V2:

- Apply V2 to D, holding G=1

- After  $T_{PD}$ , V2 appears at Q=Q'

- After another T<sub>PD</sub>, Q' & D both valid for T<sub>PD</sub>; will hold Q=V2 independently of G

- Set G=O, while Q' & D hold Q=D

- After another T<sub>PD</sub>, G=O and Q' are sufficient to hold Q=V2 independently of D

#### Dynamic Discipline for our latch:

T<sub>SETUP</sub> = 2T<sub>PD</sub>: interval *prior to G* transition for which D must be stable & valid

T<sub>HOLD</sub> = T<sub>PD</sub>: interval *following* G transition for which D must be stable & valid

Lecture 5, Slide 6

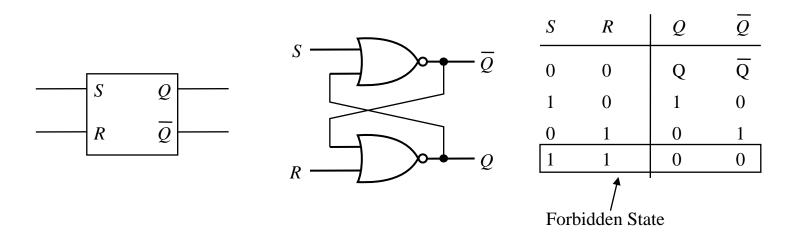

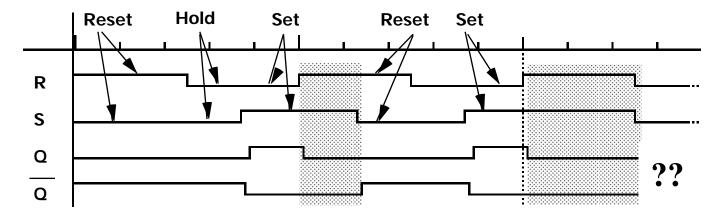

#### NOR-based Set-Reset (SR) Flipflop

Flip-flop refers to a bi-stable element

Lecture 5, Slide 7

#### Lets try using the D-Latch...

Plan: Build a Sequential Circuit with one bit of STATE -

- Single latch holds CURRENT state

- Combinational Logic computes

- NEXT state (from input, current state)

- OUTPUT bit (from input, current state)

- State changes when G = 1 (briefly!)

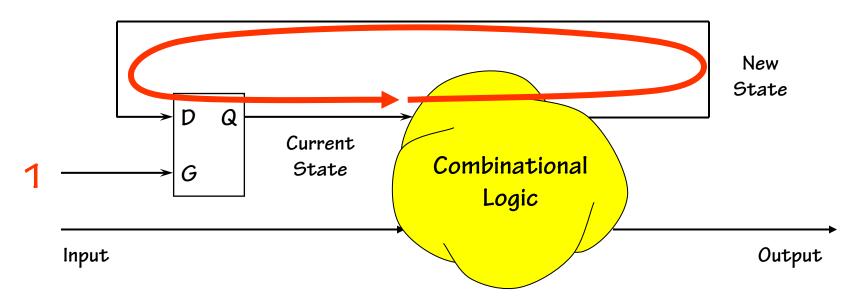

#### **Combinational Cycles**

When G=1, latch is Transparent...

... provides a combinational path from D to Q.

Can't work without tricky timing constrants on G=1 pulse:

- Must fit within contamination delay of logic

- Must accommodate latch setup, hold times

Want to signal an INSTANT, not an INTERVAL... 6.111 Fall 2005

Lecture 5, Slide 9

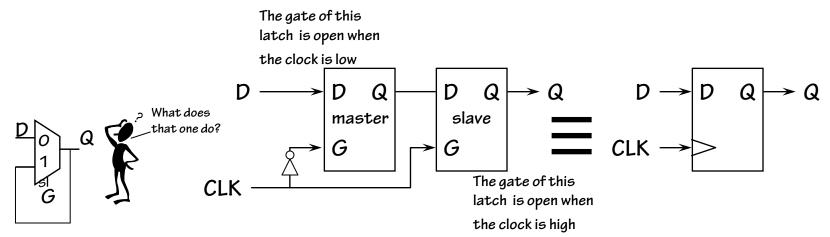

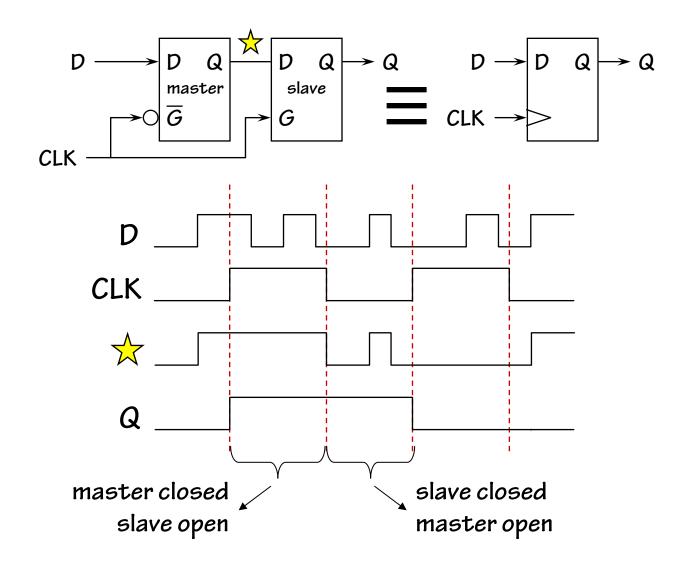

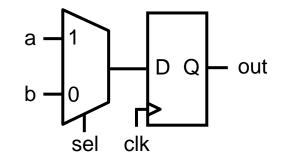

## Edge-triggered D-Register

#### **Observations:**

- only one latch "transparent" at any time:

- master closed when slave is open

- slave closed when master is open

- $\rightarrow$  no combinational path through flip flop

(the feedback path in one of the master or slave latches is always active)

◆ Q only changes shortly after O → 1 transition of CLK, so flip flop appears to be "triggered" by rising edge of CLK

Transitions mark *instants*, not intervals

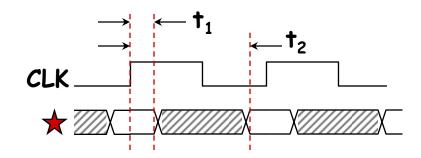

#### **D-Register Waveforms**

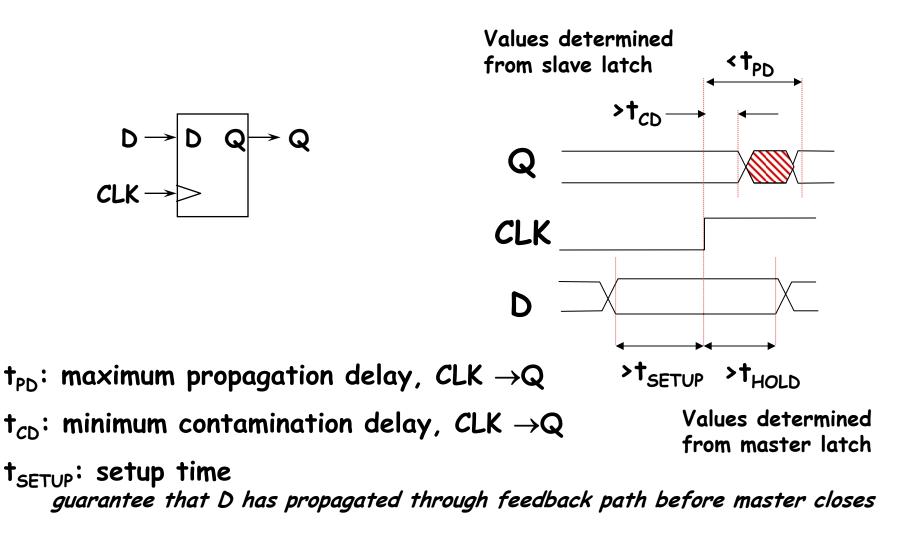

### D-Register Timing - I

t<sub>HOLD</sub>: hold time

guarantee master is closed and data is stable before allowing D to change

### D-Register Timing - II

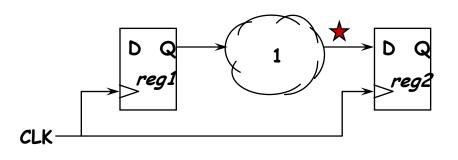

$$t_1 = t_{CD,reg1} + t_{CD,1} > t_{HOLD,reg2}$$

$$t_2 = t_{PD,reg1} + t_{PD,1} < t_{CLK} - t_{SETUP,reg2}$$

Questions for register-based designs:

- how much time for useful work (i.e. for combinational logic delay)?

- does it help to guarantee a minimum t<sub>CD</sub>? How about designing registers so that t<sub>CD,reg</sub> > t<sub>HOLD,reg</sub>?

- what happens if CLK signal doesn't arrive at the two registers at exactly the same time (a phenomenon known as "clock skew")?

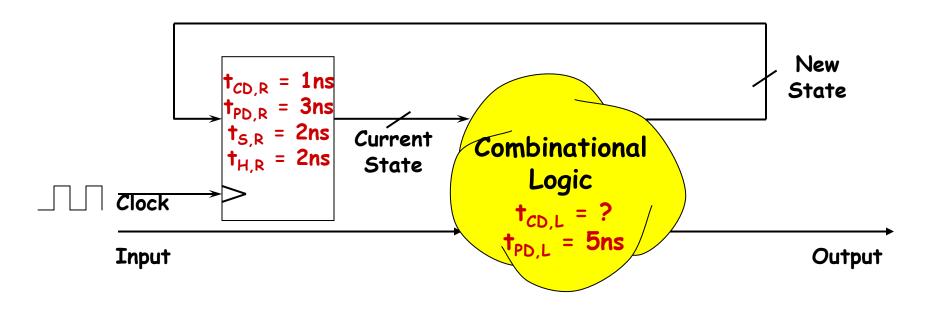

### Sequential Circuit Timing

#### Questions:

- Constraints on  $T_{CD}$  for the logic? > 1 ns

- Minimum clock period?

- Setup, Hold times for Inputs?

> 10 ns (T<sub>PD,R</sub>+T<sub>PD,L</sub>+ T<sub>S,R</sub>)

$$T_{s} = T_{PD,L} + T_{s,R}$$

$$T_{H} = T_{H,R} - T_{CD,L}$$

This is a simple *Finite State Machine* ... more on next time!

#### The Sequential always Block

Edge-triggered circuits are described using a sequential always block

#### **Combinational**

#### **Sequential**

```

endmodule

```

endmodule

## Importance of the Sensitivity List

- The use of posedge and negedge makes an always block sequential (edge-triggered)

- Unlike a combinational always block, the sensitivity list does determine behavior for synthesis!

| D Flip-flop with synchronous clear                                                                              | D Flip-flop with asynchronous clear                                                                          |  |

|-----------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|--|

| <pre>module dff_sync_clear(d, clearb,<br/>clock, q);<br/>input d, clearb, clock;<br/>output q;<br/>reg q;</pre> | <pre>module dff_async_clear(d, clearb, clock, q);<br/>input d, clearb, clock;<br/>output q;<br/>reg q;</pre> |  |

| always @ (posedge clock)                                                                                        | always @ (negedge clearb or posedge clock)                                                                   |  |

| <pre>begin<br/>if (!clearb) q &lt;= 1'b0;<br/>else q &lt;= d;<br/>end<br/>endmodule</pre>                       | <pre>begin<br/>if (!clearb) q &lt;= 1'b0;<br/>else q &lt;= d;<br/>end<br/>endmodule</pre>                    |  |

| always block entered only at                                                                                    | always block entered immediately                                                                             |  |

always block entered only at each positive clock edge always block entered immediately when (active-low) clearb is asserted

Note: The following is **incorrect** syntax: always @ (clear or negedge clock) If one signal in the sensitivity list uses posedge/negedge, then all signals must.

#### Assign any signal or variable from <u>only one</u> always block, Be wary of race conditions: always blocks execute in parallel

# Blocking vs. Nonblocking Assignments

- Verilog supports two types of assignments within always blocks, with subtly different behaviors.

- Blocking assignment: evaluation and assignment are immediate

```

always @ (a or b or c)

begin

x = a | b; 1. Evaluate a | b, assign result to x

y = a ^ b ^ c; 2. Evaluate a^b^c, assign result to y

z = b & ~c; 3. Evaluate b&(~c), assign result to z

end

```

• Nonblocking assignment: all assignments deferred until all righthand sides have been evaluated (end of simulation timestep)

```

always @ (a or b or c)

begin

x <= a | b; 1. Evaluate a | b but defer assignment of x

y <= a ^ b ^ c; 2. Evaluate a^b^c but defer assignment of y

z <= b & ~c; 3. Evaluate b&(~c) but defer assignment of z

end</pre>

```

Sometimes, as above, both produce the same result. Sometimes, not!

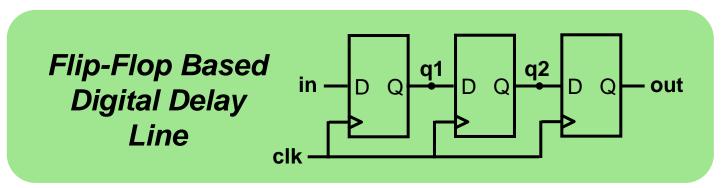

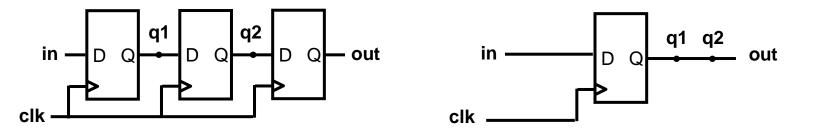

#### Assignment Styles for Sequential Logic

Will nonblocking and blocking assignments both produce the desired result?

```

module nonblocking(in, clk, out);

module blocking(in, clk, out);

input in, clk;

input in, clk;

output out;

output out;

reg q1, q2, out;

reg q1, q2, out;

always @ (posedge clk)

always @ (posedge clk)

begin

begin

q1 <= in;

q1 = in;

q_2 <= q_1;

q^2 = q^1;

out \leq q_2;

out = q_2;

end

end

endmodule

endmodule

```

### Use Nonblocking for Sequential Logic

```

always @ (posedge clk)

begin

q1 <= in;

q2 <= q1;

out <= q2;

end</pre>

```

"At each rising clock edge, q1, q2, and *out* simultaneously receive the old values of *in*, q1, and q2."

"At each rising clock edge, q1 = in. After that, q2 = q1 = in. After that, out = q2 = q1 = in. Therefore out = in."

- Blocking assignments do not reflect the intrinsic behavior of multi-stage sequential logic

- Guideline: use nonblocking assignments for sequential always blocks

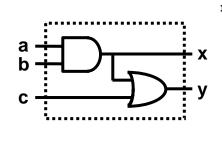

# Use Blocking for Combinational Logic

| Blog | cking Behavior                              | abc xy              |

|------|---------------------------------------------|---------------------|

|      | (Given) Initial Condition                   | 11011               |

|      | <i>a</i> changes;<br>always block triggered | <mark>0</mark> 1011 |

|      | x = a & b;                                  | <b>01001</b>        |

|      | y = x   c;                                  | 01000               |

```

module blocking(a,b,c,x,y);

input a,b,c;

output x,y;

reg x,y;

always @ (a or b or c)

begin

x = a & b;

y = x | c;

end

```

endmodule

| Nonblocking Behavior                        | abc xy               | <b>Deferred</b> mod | <pre>module nonblocking(a,b,c,x,y);</pre>                                                                |

|---------------------------------------------|----------------------|---------------------|----------------------------------------------------------------------------------------------------------|

| (Given) Initial Condition                   | 11011                |                     | input a,b,c;<br>output x,y;                                                                              |

| <i>a</i> changes;<br>always block triggered | <mark>0</mark> 1011  |                     | <pre>reg x,y; always @ (a or b or c) begin     x &lt;= a &amp; b;     y &lt;= x   c; end endmodule</pre> |

| x <= a & b;                                 | <mark>01</mark> 011  | x<=0                |                                                                                                          |

| y <= x   c;                                 | 01 <mark>0</mark> 11 | x<=0, y<=1          |                                                                                                          |

| Assignment completion                       | 010 <mark>01</mark>  |                     |                                                                                                          |

- Nonblocking and blocking assignments will synthesize correctly. Will both styles simulate correctly?

- Nonblocking assignments do not reflect the intrinsic behavior of multi-stage combinational logic

- While nonblocking assignments can be hacked to simulate correctly (expand the sensitivity list), it's not elegant

- Guideline: use blocking assignments for combinational always blocks

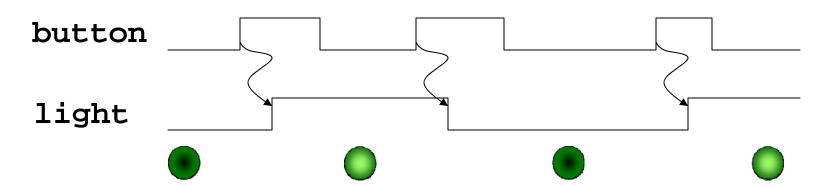

#### Implementation for on/off button

```

module onoff(button,light);

input button;

output light;

reg light;

always @ (posedge button)

begin

light <= ~light;

end

BUTTON → Q

endmodule

```

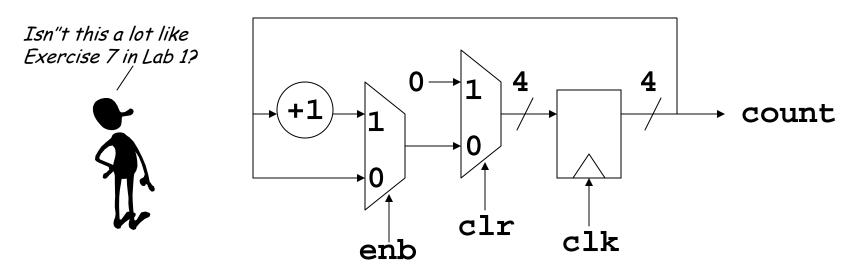

### A Simple Counter

```

# 4-bit counter with enable and synchronous clear

module counter(clk,enb,clr,count);

input clk,enb,clr;

output [3:0] count;

reg [3:0] count;

always @ (posedge clk) begin

count <= clr ? 4'b0 : (enb ? count+1 : count);

end

endmodule

```